# An Analytical Delayed-Turn-off Model for Buried-Channel PMOS Devices Operating at 77K

J. H. Sim and J. B. Kuo

Rm. 526, Dept. of Electrical Eng., National Taiwan University Roosevelt Rd. Sec. 4 #1, Taipei, Taiwan 107 FAX:886-2-363-8247, Telephone:886-2-363-5251 E-mail:kuojb@leibniz.ee.ntu.edu.tw

### Abstract

Current circuit simulation programs such as SPICE do not provide a sufficient low-temperature device model for buried-channel PMOS devices biased in the delayed-turn-off region [1]. This paper presents a closed-form analytical PMOS delayed-turn-off model suitable for simulation of circuits with PMOS devices operating at the liquid nitrogen temperature. As compared to the low-temperature PISCES [2]-[4] results, the closed-form analytical PMOS delayed-turn-off model provides a much better accuracy for simulation of circuits operating at 77K.

#### Summary

Recently, low temperature operation of CMOS circuits has been receiving substantial attention owing to advantages in speed performance, latchup immunity, and relaxed scaling restrictions[5]. However, the available circuit simulation programs such as SPICE do not provide accurate models for CMOS devices operating at 77K. Especially, the delayed-turn-off phenomenon of the PMOS device with a counterdoped channel, operating at 77K, is not included in the SPICE model. Although, device-level models describing the PMOS delayed-turn-off behavior has been reported [1] using iterative numerical methods, it is not suitable for circuit simulation. In this paper, a closed-form analytical delayed-turn-off model of the PMOS device operating at 77K suitable for SPICE circuit simulation is described.

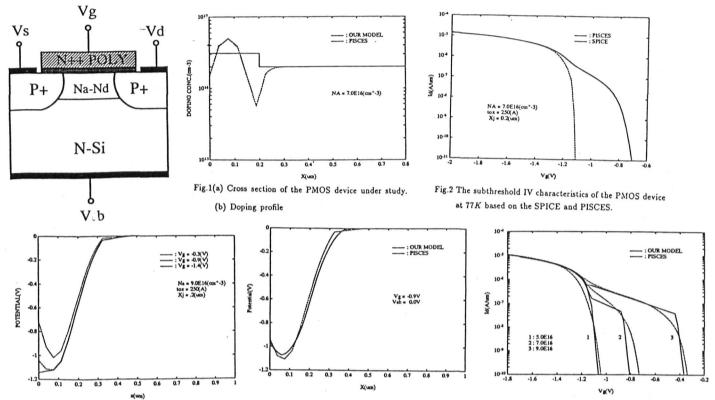

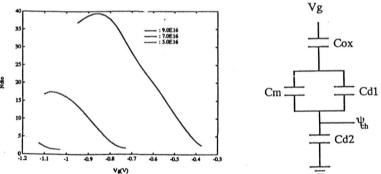

Fig. 1(a) shows the cross section of a PMOS device based on a  $1.2\mu m$ CMOS technology used in the study. The PMOS device has a gate oxide thickness of 250Å. Fig. 1(b) shows the vertical doping profile in the center of the channel with a junction depth of  $0.2\mu m$ . As shown in Fig. 2, based on the current SPICE model, the subthreshold IV characteristics of the PMOS device at 77K is very different from the PISCES results[3][4], where incomplete ionization, bandgap narrowing, concentration and E-field dependent mobilities, Shockley-Read-Hall and Auger recombinations with concentration dependent lifetimes have been included [4]. As shown in Fig. 3, at 77K, in the PMOS device biased in the delayed-turn-off region, the potential distribution indicates a valley at the peak of the implanted channel, which implies a zero electric field. Between the peak of the implanted channel and the silicon surface, the potential difference is large for the device biased in the strong and conventional weak inversion regions. However, in the delayed-turn-off region, the voltage difference between the silicon surface and the potential valley is small, where the freeze-out effects are important. As shown in Fig. 4, a closed-form analytical delayed-turnoff model has been successfully created by solving Poisson's equation with incomplete ionization around the potential valley for the regions above and below the potential valley. As shown in Fig. 5, a good agreement between the analytical model and the PISCES results can be found in the potential distribution for the device operating in the delayed-turn-off region. Fig. 6 shows the subthreshold IV characteristics of the PMOS device with a channel implant depth of  $0.2\mu m$  for three peak concentrations ( $5,7,9 \times 10^{16} cm^{-3}$ ) based on the analytical and PISCES results. For a higher peak concentration, the PMOS device indicates a longer delayed-turn-off interval. The analytical model demonstrates a very close fit to the 2D results in the delayed-turn-off region. Fig. 7(a) shows the subthreshold slope  $(n \equiv \frac{\partial V_G}{\partial \Psi_{ch}})$  of the PMOS device with a channel implant depth of  $0.2 \mu m$  for three peak concentrations. In the delayed-turn-off region, as the gate voltage moves toward the positive direction, the slope is decreasing. As it reaches the weak

inversion region, the slope is at minimum. Among three cases, the delayed-turn-off slope is the largest for the  $9 \times 10^{16} cm^{-3}$  case, which shows the strongest delayed-turn-off phenomenon. For a peak concentration of less than  $5 \times 10^{16} cm^{-3}$ , the delayed-turn-off behavior almost diminishes. As shown in Fig. 7(b), in addition to the oxide capacitance, the equivalent capacitance model is composed of two depletion capacitances  $(C_{D1}, C_{D2})$  and another capacitance  $C_M$  accounting for the mobile charge in the channel. As the gate voltage is near the conventional weak inversion region, the subthreshold slope of the analytical model results is approaching  $n = 1 + C_{D2}(\frac{1}{C_{D1}} + \frac{1}{C_{O\lambda}})$ , as for the room temperature case [6] since freeze-out effect is negligible. Figs. 8(a) & (b) show the interval of  $V_G$  where delayed-turn-off exists and the delayed-turn-off slope vs. the junction depth of the channel implant for various peak concentrations and gate oxide thicknesses. With a deeper channel implant, the device indicates a stronger delayed-turnoff behavior. On the other hand, with a thinner gate oxide, the device shows a less delayed-turn-off phenomenon owing to a more influence from the gate. In conclusion, a closed-form analytical delayed-turn-off model of a PMOS device operating at 77K has been successfully created. Compared to low-temperature PISCES results, a much better match can be identified using the analytical model, which is suitable for simulation of circuits with PMOS devices operating at 77K.

## Acknowledgments

The authors would like to thank Prof. Dutton of Stanford University for helping us obtain the license to use the PISCES program. The authors would also like to thank W. C. Lee and Y. W. Chen of National Taiwan University for their help during the initial phase of the work. This work is supported under R.O.C. National Science Council Contract #79-0404-E002-21.

# References

[1]F. II. Gaensslen and R. C. Jaeger, "Temperature Dependent Threshold Behavior of Depletion Mode MOSFETs," Solid State Electronics, 1979 [2] Y. W. Chen, K. H. Lou and J. B. Kuo, "Two-Dimensional Transient Analysis of a BiNMOS Transistor Operating at 77K Using a Modified PISCES Program," Proc. of IEEE Process/Device Modeling Workshop, Tokyo,8/90 [3] Y. W. Chen, K. II. Lou and J. B. Kuo, "Two-Dimensional Transient Analysis of a BiPMOS Transistor Operating at 77K Using a Modified PISCES

Program," Digest of IEEE International EDMS, 11/90

[4] Y. W. Chen, K. II. Lou and J. B. Kuo, "Two-Dimensional Transient Analysis of BiNMOS Device," to be published in IEEE TED

[5] "Low Temperature Electronics," IEEE Press Book, 1986

[6]T. E. Hendrickson, "A Simplified Model for Subpinchoff Conduction in Depletion-Mode IGFET's," IEEE TED 4/78

Fig. 3 Potential distributions in the PMOS device at 77K.

Fig. 5 Potential distribution in the PMOS device at 77K using the analytical model and the PISCES results. Fig. 6 Subthreshold IV characteristics of the PMOS device using the analytical model and the PISCES results.

Fig. 7 (a)Subthreshold slope of the PMOS device using the analytical model and the PISCES results.

(b)Equivalent capacitance model

Fig. 8 (a) The voltage interval where delayed-turn-off exists (b)  $n_{dto}$  vs. the junction depth of the channel implant