# TCAD Analysis on the Geometry Effects in Three-Independent-Gates Reconfigurable FETs

J.M. Gonzalez-Medina<sup>1</sup>, L.-C. Hung<sup>1,5</sup>, Y. He<sup>2</sup>, A. Arsalane<sup>3</sup> O. Baumgartner<sup>1</sup>,

T. Mikolajick<sup>2,4</sup> J. Trommer<sup>2</sup>, C. Mukherjee<sup>3</sup> and M. Karner<sup>1</sup>

Global TCAD Solutions GmbH, Vienna, Austria email: jm.gonzalezmedina@globaltcad.com.

NaMLab gGmbH, Nöthnitzer Strasse 64a, 01187, Dresden, Germany.

Image: Germany of Nanoelectronic Materials, University of Technology Dresden, Dresden, Germany

Institute of Microelectronics, TU Wien, 1040 Vienna, Austria

Abstract—The n-type and p-type operations of 22 nm Fully Depleted Silicon on Insulator (FDSOI) Three-Independent-Gates Reconfigurable Field Effect Transistors (TIG-RFETs) are simulated, incorporating Schottky contacts to the drift-diffusion model. Key-features are selected and adjusted to fit experimental results, like: Schottky barrier height (SBH), direct tunnelling and presence of traps. The inclusion and correct adjustment of these parameters reveals the importance of strong electrostatic control over the energetic barrier at the metal-semiconductor junctions. We extend this analysis with a study of the theoretical impact of the metal-semiconductor interface position under the source-drain gates coupled with the length of the ungated regions.

Index Terms—RFET, TCAD, FDSOI, Schottky contact, DTCO.

### I. INTRODUCTION

Reconfigurable FETs are an interesting alternative to the classic CMOS technology that offer more flexibility at the circuit design level [1]-[3]. Keeping the channel intrinsic, and directly contacting it with the source and drain metals, a Schottky Barrier will form. A gate is placed on top of each contact, which is used to electrostatically control the screening length, allowing or blocking the flow of one type of carrier. In addition to this, a third gate can be placed in the middle of the channel to control its conductivity in a more classical way. This flexibility comes with a performance penalty inherent to any Schottky-based transistor [4], [5], and more complexity when designing new logic cells. However, it allows that the same circuit block has various and run-time configurable working modes. The amount of different operation modes [6]-[8], input variables and potential transistors and cells designs is almost unlimited [9], [10]. Here is where accurate TCAD and compact models can offer a great help to explore the working principles and main parameters of the complete family of such devices [11].

In this work, we calibrate a semi-classical TCAD model to fit the experimentally measured transfer characteristics of a TIG-RFET based on the devices described in [12]. The model is used to explore the impact in the performance due to modifications of the geometry. This impact is difficult and expensive to systematically investigate in hardware. Examples of such parameters are the position of the contacts under the source-drain gates and the length of the ungated regions.

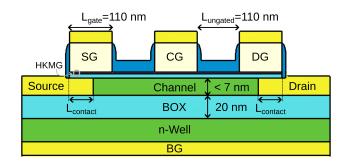

Fig. 1. Device schematic of a TIG-RFET. The key elements analysed in this study are: the ungated length  $(L_{ungated})$  and the gate-contact overlap  $(L_{contact})$

### II. DEVICE DESCRIPTION AND WORKING PRINCIPLE

Fig. 1 shows the implemented geometry of the studied TIG-RFET taken from [12]. It is composed of a doping-free Silicon channel over an SiO<sub>2</sub> layer (BOX), a Back Gate (BG) below an n-type doped well, and three top gates, namely Source Gate (SG), Drain Gate (DG) and Central Gate (CG). These gates are subdivided into two groups: Programming Gates and Control Gates. Usually, the Programming Gate is the one used to select the kind of carrier that can flow in the device, whereas the Control Gate regulates the flow. Which one is the Control Gate depends on the operation mode and the number of gates in the RFET [13]. In a TIG-RFET, when the Control Gate is the central one and the Source Gate is biased together with the Drain Gate to program the transport mode, low threshold voltage (V<sub>T</sub>) transfer curves are achieved. If, instead, the Source Gate is the one controlling the carrier flow, then a higher  $V_T$  is obtained. This is the high- $V_T$  operation

In this analysis, we will work on the numerical characterization of n-type and p-type branches, both under high-  $V_T$  and low- $V_T$  operation modes. Optimizing the source/drain (S/D) contact is also crucial for enhancing the performance of these Schottky-barrier based devices. Therefore, the impact of geometry parameters, such as the gate-contact overlap length ( $L_{contact}$ ) and the ungated length ( $L_{ungated}$ ), is investigated.

### III. TCAD MODEL

To account for the effects of quantum confinement, the density gradient model [14] is coupled in a Drift-Diffusion solver [15]. Thermionic emission (TE) at the contacts are evaluated, taking into account the SBH. The permeation model, as proposed by [16], is applied to account for direct tunnelling of both carriers through the SBH, depending on the operation mode. The transmission coefficient calculation is based on the Wentzel-Kramers-Brillouin (WKB) method for linear barriers. In an ideal case, these elements would be enough to describe the behaviour of these Schottky-barrier based devices. However, to better match experimental results, the presence of bulk traps in the channel, close to the contacts, also needs to be considered. The higher number of gates and operation modes compared to a classical MOSFET leads to a large design space. This can also complicate the fitting process to experimental data. Therefore, an optimization flow has been implemented to adjust the key selected parameters of the model, as demonstrated by [17].

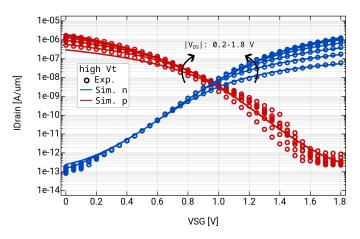

Fig. 2. TCAD simulation fitting to experimental transfer curves at different drain voltages in the high- $V_{\rm T}$  regime. In this case, the bias of CG and DG gates is fixed, whereas the SG is swept. The impact of the Schottky barrier, direct tunnelling and bulk traps is considered.

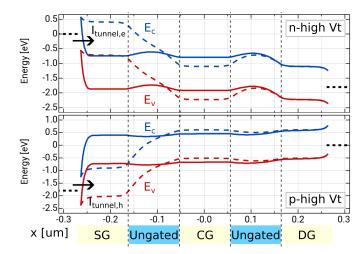

The fitted tranfer curves in comparison to the experimentally measured transfer curves for the high-V<sub>T</sub> operation modes are depicted in Fig. 2, showing a good agreement with the measurements. The key parameters used in the simulation, including band edge parameters, metal work function of source and drain contacts, and tunneling effective masses, are summarized in Table I. Some interesting conclusions can be extracted from this fitting work. First, the current in this transport mode is mostly dominated by the access resistance at the sourcechannel interface. This is easier to understand with support of the band diagrams, depicted in Fig. 3. Conduction and valence bands, together with electron and hole quasi-Fermi levels are extracted in a cut in the middle of the channel along the transport direction. To keep the right voltage reference, the n-type branch is biased with  $V_D = 1.8 \text{ V}$  and  $V_S = 0.0$ V, whereas for the p-branch  $V_D = 0.0 \text{ V}$  and  $V_S = 1.8 \text{ V}$ . In all this analysis, the BG is kept to 0.0 V. When the SG

Fig. 3. Band diagrams of the n-type (top) and p-type (bottom) high- $V_{\rm T}$  transport modes, in on-state (solid) and off-state (dashed)

is activated (low voltage for p-type transport, high positive voltage for n-type), the electrostatic screening length of the mid-gap SBH is reduced for the selected carrier, allowing the tunneling injection through the barrier. As SG is turned off, the screening length is recovered, and the access resistance blocks the tunnelling injection, resulting in a TE-dominated transport. It is noteworthy to mention the impact of the ungated regions. As can be seen, the energy bands bend in those regions, which translates in an insufficient amount of carrier concentration and hence a low conductivity of the channel. Secondly, we can mention that traps close to the source-channel interface have a negative impact on the screening length, decreasing the top gate control. For the n-type transport, this results into a more pronounced dependency of the on-current with the drain bias, and an increase of the off-current. The measurements suggest that p-type transport is significantly influenced by trap dynamics, leading to a noticeable threshold voltage shift in the off-state regime. Moreover, this V<sub>T</sub> shift exhibits a clear dependence on the drain-source bias, which may suggest a bias-temperature instability under p-type operation. However, a detailed modeling of this phenomenon is beyond the scope of this work.

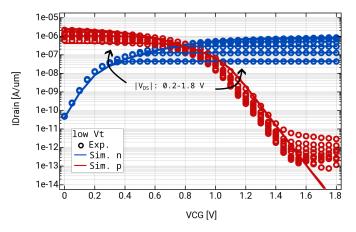

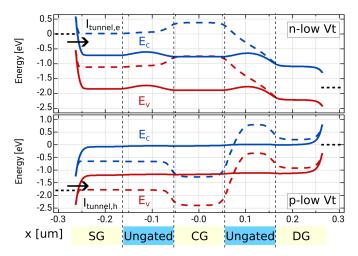

The results from the fitting of the transfer characteristics of the device for low- $V_T$  operation mode are depicted in Fig. 4. It is possible to see how the behaviour of the device drastically changes with the configured operation mode. Compared to the previous high- $V_T$  mode, this one has a much smaller subthreshold slope and turn-on voltage, more suitable for logic devices. Again it is possible to visualize in Fig. 5 the band diagrams in on- and off-state for this low- $V_T$  operation mode. Since this configuration fixes the SG and DG bias, to enable the transport of one single carrier, the access resistance is fixed. The conductivity is then controlled by the CG, and the bands resemble more the ones of a regular planar MOSFET. As the device is turned on, the conductivity of the ungated regions changes more drastically compared to the high- $V_T$  case. This

shows how the central gate has a stronger effect on these regions than SG or DG. The use of these tools can be useful

in the development of compact models that can be evaluated in SPICE simulations [18]. Alternatively, extended datasets can effectively be generated using the TCAD tool to generate Verilog-A table models. These outputs can be further applied to effectively extract important Key Performance Indicators (KPI) from complex analog and digital circuits [19], [20].

### IV. GEOMETRY EXPLORATION

Since this device was purposedly fabricated in a bigger scale to account for the design rule constraints of the underlying baseline technology [21], it is interesting to show in advance some estimates of the performance when certain elements are scaled down to find optimal design choices not yet possible in fabrication.

Fig. 4. TCAD simulation fitting to experimental transfer curves at different drain voltages in the low- $V_T$  regime. In this case, the bias of SG and DG gates is fixed, whereas the CG is swept. The impact of the Schottky barrier, direct tunnelling and bulk traps is considered.

Fig. 5. Band diagrams of the n-type (top) and p-type (bottom) low- $V_T$  transport modes, in on-state (solid) and off-state (dashed). The band profile is more similar to the one of regular planar MOSFETs.

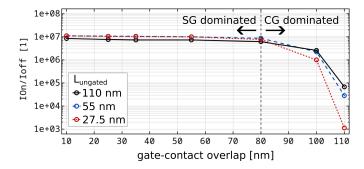

Fig. 6. Ion/Ioff ratio in the nbranch, high- $V_T$  operation mode vs. gate-contact overlap ( $L_{contact}$ ) for different ungated regions lengths ( $L_{ungated}$ ). The dotted line highlight the transition point at which the access resistance control is not dominated any more by the SG.

Here we investigate how the on- and off-current performance are affected by the scaling of the ungated region length (L<sub>ungated</sub>) along with the overlapping of the source/drain contacts with SG/DG (L<sub>contact</sub>). For this analysis, we consider the n-type, high-V<sub>T</sub> operation mode. We evaluate the I<sub>on</sub> current for all gates biased positively to 1.8 V. The Ioff current is extracted for the case that SG voltage is set to 0.0 V. The results depicted in Fig. 6 show how the I<sub>on</sub>/I<sub>off</sub> currents ratio can be improved as the ungated regions are made shorter. When they are short enough, the top gates can generate a high enough electrostatic doping in these regions, minimizing the series resistance and increasing the on-current. Since this is a Schottky-barrier device, the total resistance of the system is still mainly dominated by the access resistance, and hence an improvement in the conductivity of the ungated regions can have only a marginal benefit over the Ion current. However, the shortening of the ungated regions can offer other benefits, such as less exposure to oxide-semiconductor interface traps that limit the electrostatic control of the gates over the channel. It also provides a better control of the fringing fields in the ungated region.

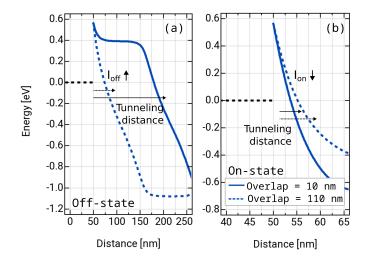

At the same time, placing the contacts too deep (> 80 nm) beneath the SG/DG significantly increases the off-current. This is due to lowered electrostatic coupling with the source gate, which reduces the tunnelling distance in the off-state. It can be better appreciated in Fig. 7a, where the conduction band near the source contact is plotted for two different contact overlap distances, 10 and 110 nm. Notice that the bands have been shifted to align with the source contact position, so the differences can be better appreciated. In this case, it is possible to see how SG is effectively suppressing the I<sub>off</sub> tunnel current when there is a moderate contact-gate overlap. This effect becomes even more pronounced with shorter ungated regions. Similarly, the impact of the contact-gate overlap can be seen by analyzing the conduction band in the on-state, depicted in Fig. 7b. It is shown that there is a slight increase in the screening length, which has an impact in the final Ion. This difference in the bands, despite small, made that the Ion changed by a factor of 15 for the plotted conditions.

Fig. 7. Band profiles along the channel departing from the source contact position for the n-branch high- $V_T$  operation mode in (a) off-state and (b) on-state. Comparison of the bands for two different contact overlap with the source gate, 10 nm (solid lines) and 110 nm (dashed). Both cases are for the longest (110 nm) ungated regions.

$\begin{tabular}{l} TABLE\ I\\ SIMULATION\ PARAMETERS\ FOR\ THE\ HIGH-V_T\ TIG-RFET \end{tabular}$

| Parameter                                   | Value      |

|---------------------------------------------|------------|

| S/D metal work function (eV)                | 4.61       |

| Si electron affinity (eV)                   | 4.05       |

| Si bandgap energy (eV)                      | 1.12       |

| Tunneling effective mass: $m_e / m_h (m_0)$ | 0.1 / 0.08 |

### V. CONCLUSIONS

We have calibrated a semi-classical TCAD simulation flow with experimental measurements of FDSOI TIG-RFET devices for both n- and p-branches in high- $V_T$  and low- $V_T$  operation modes. The simulations show the impact of the Schottky barrier and the ungated regions on the transport, and correctly captures the different behaviour in all the studied transport regimes. This flow can be used to study and optimize key parameters that determine the device performance, such as the gate-contact overlap or the length of the ungated regions.

## VI. ACKNOWLEDGEMENT

This work was partially funded by the European Union under the grant agreement Horizon Europe, SENSOTERIC, GA no. 101135316. Views and opinions expressed are, however, those of the authors only and do not necessarily reflect those of the EU or the EC. Neither the EU nor the granting authority can be held responsible for them.

# REFERENCES

- L. Wind, A. Fuchsberger, O. Demirkiran, L. Vogl, P. Schweizer, X. Maeder, M. Sistani, and W. M. Weber, "Reconfigurable si field-effect transistors with symmetric on-states enabling adaptive complementary and combinational logic," *IEEE TED*, vol. 71, p. 1302–1307, Feb. 2024.

- [2] G. Galderisi, T. Mikolajick, and J. Trommer, "The rgate: An 8-in-1 polymorphic logic gate built from reconfigurable field effect transistors," *IEEE Electron Device Letters*, vol. 45, pp. 496–499, Mar. 2024.

- [3] M. Simon, H. Mulaosmanovic, V. Sessi, M. Drescher, N. Bhattacharjee, S. Slesazeck, M. Wiatr, T. Mikolajick, and J. Trommer, "Three-to-one analog signal modulation with a single back-bias-controlled reconfigurable transistor," *Nature Communications*, vol. 13, p. 7042, Nov. 2022.

- [4] M. Schwarz, T. Vethaak, V. Derycke, A. Francheteau, B. Iniguez, S. Kataria, A. Kloes, F. Lefloch, M. Lemme, J. Snyder, W. Weber, and L. Calvet, "The Schottky barrier transistor in emerging electronic devices," *Nanotechnology*, vol. 34, p. 352002, Aug. 2023.

- [5] E. Bestelink, G. Galderisi, P. Golec, Y. Han, B. Iniguez, A. Kloes, J. Knoch, H. Matsui, T. Mikolajick, K. M. Niang, B. Richstein, M. Schwarz, M. Sistani, R. A. Sporea, J. Trommer, W. M. Weber, Q.-T. Zhao, and L. E. Calvet, "Roadmap for schottky barrier transistors," *Nano Futures*, vol. 8, p. 042001, Dec. 2024.

- [6] J. Trommer, A. Heinzig, T. Baldauf, S. Slesazeck, T. Mikolajick, and W. M. Weber, "Functionality-enhanced logic gate design enabled by symmetrical reconfigurable silicon nanowire transistors," *IEEE Trans*actions on Nanotechnology, vol. 14, no. 4, pp. 689–698, 2015.

- [7] J. Romero-González and P.-E. Gaillardon, "An efficient adder architecture with three- independent-gate field-effect transistors," in 2018 IEEE International Conference on Rebooting Computing (ICRC), pp. 1–8, 2018.

- [8] T. F. Canan, S. Kaya, A. Karanth, H. Xin, and A. Louri, "Ambipolar sb-finfets: A new path to ultra-compact sub-10 nm logic circuits," *IEEE Transactions on Electron Devices*, vol. 66, no. 1, pp. 255–263, 2019.

- [9] M. Reuter, A. Kramer, T. Krauss, J. Pfau, J. Becker, and K. Hofmann, "Reconfiguring an rfet based differential amplifier," in 2022 IEEE 40th CONCAPAN, p. 1–6, IEEE, Nov. 2022.

- [10] P.-E. Gaillardon, R. Magni, L. Amaru, M. Hasan, R. Walker, B. S. Rodriguez, J.-F. Christmann, and E. Beigne, "Three-independent-gate transistors: Opportunities in digital, analog and rf applications," in 2016 17th Latin-American Test Symposium (LATS), p. 195–200, IEEE, Apr. 2016.

- [11] G. D. Jayakumar, G. Babu B., K. Reddy R., and R. Srinivasan, "Vertically stacked three-gate reconfigurable nanosheet and reconfigurable nanowire transistors," *Semiconductors*, vol. 58, pp. 894–902, Nov. 2024.

- [12] N. Bhattacharjee, Y. He, G. Galderisi, V. Havel, S. Slesazeck, V. Sessi, M. Drescher, M. Zier, M. Simon, K. Ruttloff, K. Li, A. Zeun, A.-S. Seidel, C. Metze, M. Grothe, S. J. J. Hoentschel, T. Mikolajick, and J. Trommer, "Multiple-independent-gate reconfigurable fets processed on industrial 300 mm fdsoi," *IEEE Electron Device Letters*, 2025.

- [13] J. Zhang, P.-E. Gaillardon, and G. De Micheli, "Dual-threshold-voltage configurable circuits with three-independent-gate silicon nanowire fets," in 2013 IEEE International Symposium on Circuits and Systems (IS-CAS), pp. 2111–2114, 2013.

- [14] A. Wettstein, A. Schenk, and W. Fichtner, "Quantum device-simulation with the density-gradient model on unstructured grids," *IEEE TED*, vol. 48, pp. 279–284, Feb. 2001.

- [15] Global TCAD Solutions, Minimos-NT. Accessed: May 2025. [Online]. Available: http://www.globaltcad.com/minimos-nt.

- [16] C. B. Duke. Solid state physics, Academic Press, 1969.

- [17] L.-C. Hung, G. Rzepa, M. Kampl, C.-M. Tsai, F. Schanovsky, O. Baumgartner, Z. Stanojević, and M. Karner, "Hierarchical transport modeling for path-finding dtco," *SISPAD*, Sept. 2024.

[18] M. Reuter, J. Wilm, A. Kramer, N. Bhattacharjee, C. Beyer, J. Trommer,

- [18] M. Reuter, J. Wilm, A. Kramer, N. Bhattacharjee, C. Beyer, J. Trommer, T. Mikolajick, and K. Hofmann, "Machine learning-based compact model design for reconfigurable fets," *IEEE Journal of the Electron Devices Society*, vol. 12, pp. 310–317, 2024.

- [19] A. A. Deshpande, S. Semwal, J.-P. Raskin, and A. Kranti, "Insights into parasitic capacitance and reconfigurable fet architecture for enhancing analog/rf metrics," *IEEE Transactions on Electron Devices*, vol. 70, pp. 5983–5990, Nov. 2023.

- [20] C. Navarro, L. Donetti, J. Padilla, C. Medina-Bailon, J. Galdon, C. Marquez, C. Sampedro, and F. Gamiz, "3d-tcad benchmark of twogate dual-doped reconfigurable fets on fdsoi28 technology," *Solid-State Electronics*, vol. 200, p. 108577, Feb. 2023.

- [21] R. Carter, J. Mazurier, L. Pirro, J.-U. Sachse, P. Baars, J. Faul, C. Grass, G. Grasshoff, P. Javorka, T. Kammler, A. Preusse, S. Nielsen, T. Heller, J. Schmidt, H. Niebojewski, P.-Y. Chou, E. Smith, E. Erben, C. Metze, C. Bao, Y. Andee, I. Aydin, S. Morvan, J. Bernard, E. Bourjot, T. Feudel, D. Harame, R. Nelluri, H.-J. Thees, L. M-Meskamp, J. Kluth, R. Mulfinger, M. Rashed, R. Taylor, C. Weintraub, J. Hoentschel, M. Vinet, J. Schaeffer, and B. Rice, "22nm fdsoi technology for emerging mobile, internet-of-things, and rf applications," in 2016 IEEE International Electron Devices Meeting (IEDM), pp. 2.2.1–2.2.4, 2016.