# Driving Four Decades of TCAD Innovation: From Physical Simulation to AI-Powered Digital Twins

Eric Guichard<sup>1</sup>, Josef Weinbub<sup>2</sup>, Jin Cho<sup>1</sup>, Bogdan Tudor<sup>1</sup>, Christian Caillat<sup>1</sup>, Slim Chourou<sup>1</sup>, Thomas Jokinen<sup>1</sup>, Seth Veitzer<sup>1</sup>, Stefania Carapezzi<sup>3</sup>, Philippe Blaise<sup>3</sup>, Derek Kimpton<sup>1</sup>, Andreas Hössinger<sup>2</sup>, Mark Townsend<sup>1</sup>

<sup>1</sup>Silvaco, Inc., Santa Clara, California, 95054, USA

<sup>2</sup>Silvaco Europe Ltd., St Ives, Cambridgeshire, PE27 5JL, UK

<sup>3</sup>Silvaco France, Montbonnot-Saint-Martin, 38330, FR

eric.guichard@silvaco.com

Abstract—To this day, Technology Computer-Aided Design (TCAD) remains to be a key driver for sustaining the high pace of the semiconductor industry. However, the continued progress led to massively increased equipment, simulation, and fab process complexities and vast optimization spaces to be mastered, putting immense pressure on fabs and design houses and especially on the workforce. In this work, we give a short historical perspective on the roots of TCAD, provide an overview of essential new functionalities of modern TCAD, and discuss co-optimization and Digital Twins as solutions to the mounting modeling and simulation pressure experienced in the industry.

Keywords— TCAD, physical simulation, process, device, quantum, photonics, materials, AI, ML, DTCO, FTCO, Digital Twins

#### I. INTRODUCTION

TCAD has been key to the success of the microelectronics industry since its foundation in the 1980s and throughout its history played an integral part in reducing time-tomarket and cost whilst maximizing production scale. The role of modern TCAD remains unchanged, i.e., aid in designing new device designs and technologies, pathfinding, identify issues with manufacturing, interpret experimental results, provide physical insights and predictions on reliability issues, and estimate the valueproposition of future device technologies [1, 2]. However, compared to the beginnings, a TCAD simulation engineer's job has exploded in complexity. TCAD relies in its core on physical simulations as a means to accurately describe fabrication processes and device characteristics. As device designs and fabrication processes significantly evolved over the years, so have the physical models and computational methods to keep up. This has led to massively increased tool complexities and vast optimization spaces. Both need to be mastered on a rolling basis in fabs and design houses by simulation engineers. Recruiting such experts becomes more and more an issue, which is why workforce development is increasingly important [3] and educational efforts like nanoHUB play a vital complementary role [4]. Traditional co-optimization workflows, such as Design Technology Co-Optimization (DTCO) [5], can help but nowadays must require an additional layer of abstraction to overcome these challenges. This is provided by artificial intelligence, allowing to implement a Fab Technology Co-Optimization<sup>TM</sup> (FTCO<sup>TM</sup>) with which to train Digital Twins (DTs) for analyzing and optimizing processes,

designs, and yields: The core advantage being that once a DT is trained by a simulation engineer, it can be used on a standalone basis by non-simulation engineers, such as fab engineers. In Section II, we give a short overview of the TCAD evolution to set the stage. Finally, in Section III, we discuss DTCO and introduce FTCO<sup>TM</sup> by giving representative examples.

#### II. TCAD EVOLUTION

## A. Historical Perspective

The raising complexity in electronic devices in the 1960s and 1970s resulted in analytical models for device and process modeling to start hitting their limit. The introduction of digital computers enabled numerical solutions vastly beyond the limits of analytical models, which resulted in extended research on numerical methods and physical models. The reader is referred to excellent reviews on the TCAD history for further details, e.g., [1, 2, 6, 7, 8, 9]. For device modeling, among the key very early TCAD drivers was the Scharfetter-Gummel method published in 1969. For process modeling, major advances were made in the late 1970s on numerical modeling of ion implantation, diffusion, oxidation, deposition, etching, and lithography which led to the developments of iconic simulation tools, such as SUPREM-II.

The numerical and physical modeling advances both on the device and process side made in academia came at the right time to meet the design challenges of the ramping up microelectronics industry. This led to interest in commercialization and the cementing of industrial TCAD as key enabler for optimizing microelectronic devices and systems in the 1980s. A particular milestone was the foundation of Technology Modeling Associates (TMA) and the commercialization of the process simulator SUPREM-III and device simulator PISCES (commercial name MEDICI). After TMA, other vendors licensed these tools as well and created new commercial TCAD products: Silvaco offered ATHENA and ATLAS and Integrated Systems Engineering (ISE) offered DIOS and DESSIS.

### B. Classical TCAD

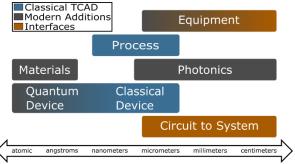

To this day, the core *classical* capabilities of TCAD are based on process and device simulations, albeit offering a wide range of new features compared to the early days of industrial TCAD. Historically, the feature dimensions were in the order of micrometers, which was expanded towards the double-digit nanometer regime over the years (Fig.1).

Fig.1: A classical and modern multi-scale view of the different types of TCAD simulations, including interfaces to other types of simulations. The classical set of TCAD tools consists of process and device simulations, with interfaces to equipment (e.g., reactor) and circuit simulations. Nowadays, this multi-scale setting is massively expanded due to (i) the emergence of novel design materials, (ii) the need for full quantum transport models to accurately describe ultra-scaled devices, and (iii) the expansion towards photonics.

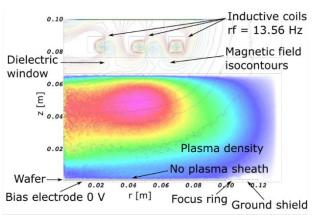

Process TCAD simulations focus on describing fabrication processes on the feature-scale to virtually construct a component (e.g., a single transistor): The focus is thus on a specific region of the wafer surface. The construction mimics the fabrication steps in a fab, allowing to focus on topographical details and changes at every step. It is important to highlight that modern devices/structures can require hundreds of processing steps, introducing a plethora of complexity rendering full physical predictive simulations essential for optimizing fabrication processes in the fab. The involved process gas species are modeled via defining angular and energetic distributions on a virtual source plane. Conventionally, these are modeled by analytical models, but can be linked to reactor-scale simulations for increased accuracy, such as inductively coupled plasma (ICP) simulations (Fig.2). Today's modeling capabilities have to cover deposition, epitaxy, oxidation, etching, ion implantation, diffusion, activation, photolithography, and stress and strain, in the context of many materials and a large variety of specialized processing equipment (Fig.3).

The virtually constructed component generated by process TCAD can either be further analyzed on its own, according to structural properties, to optimize processing steps or can be forwarded to a device TCAD simulator to determine the electrical characteristics (e.g., IV, CV) by solving a transport problem, historically the famous semiconductor equations using the drift-diffusion model. But many more exist, offering higher accuracy for certain scenarios at the cost of increased computational complexity [9]. Nowadays, key features and extensions must cover DC, AC, transient analysis, stress-dependent models, high precision numerics (particularly relevant for power and cryogenic devices), self-heating, radiation, electrochemical reactions, and light-absorption and photo-generation.

With the availability of the device characteristics as provided by device TCAD simulations, a SPICE model can be generated (aka *extracted*), allowing to use the simulated device in higher level simulations, reaching from SPICE circuit simulations and even further up to system level. Another type of circuit simulation, and particularly relevant for, e.g., back end of line (BEOL) structures, is interconnect simulation which solves the electromagnetic field problem to yield the resistance and capacitance, allowing to evaluate parasitic effects.

Dual frequency 200V low/50V high Fig.2: Inductively coupled plasma (ICP) simulations of a reactor chamber containing a wafer at the bottom which is placed on top of an electrode. The wafer is exposed to a plasma generated by inductive coils. Top: The electrode is biased at 0V: no plasma sheath is formed.

Bottom: The electrode is biased, resulting in the formation of a desired plasma sheath.

## C. Modern TCAD

The challenge of TCAD workflows has massively increased, particularly in the last 15 years, due to additional complexities (see Fig.1 and also [1, 2]) introduced by (1) 3D device designs with intricate shapes (e.g., GAA-FETs, memory), (2) novel materials (e.g., 2D materials), (3) exploitation of electronic phenomena (e.g., quantum effects), (4) multi-scale simulations (e.g., from atoms to system level), (6) photonics simulations, and (7) workforce challenges.

Reg. (1), 3D simulations are the de-facto standard today, particularly for advanced designs. Although the availability of a third design dimension gives flexibility in device designs (e.g., better channel field control by gate-all-around designs) it also significantly increases the computational burden on process and device simulations. Reg. (2), progress in computational materials science has led to the emergence of several simulation methods with which to calculate material properties (e.g., bandgap) and to design novel materials with desired target properties in mind. First principles (ab initio) tools, such as those based on density functional theory (DFT),  $\mathbf{k} \cdot \mathbf{p}$  perturbation theory or the tight-binding model, are broadly available today and their availability led to an explosion of new design materials [10]. These tools allow for a natural TCAD interface: Considering an example for device TCAD, the calculated band structures can be fed into device simulations, and for process TCAD, DFT can be linked to diffusion modeling.

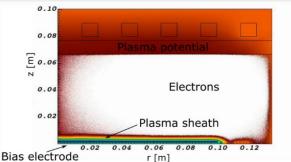

Fig.3: Stress simulation example based on a BEOL structure, showcasing a large-scale 3D physical simulation calculating displacement and von Mises stress: structure base area  $13\mu m \times 13\mu m$ , 9 metal levels, 3D Delaunay volume mesh with 11M nodes, 65M elements. Top left: Perspective view of general structure. Top right: Only copper vias are shown and highlighted in main structure. Bottom: The solved displacement and von Mises stress is shown.

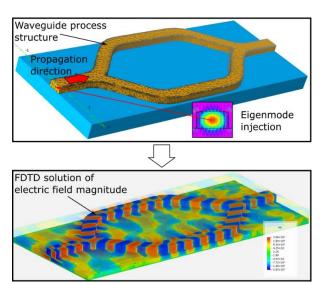

Reg. (3), cutting-edge ultra-scaled device technologies contain highly confined short-channels in the single-digit nanometer regime, which introduce quantum effects to the electron transport. A full quantum transport description is thus required, which is able to handle realistic boundary conditions (e.g., for the contacts) and various scattering models as provided by, for instance, a non-equilibrium Green's function approach [11]. Naturally, such a quantum transport description requires severe computational effort which even with highly parallel solution approaches would not be practical in an industrial setting without complexityreducing algorithms such as low-rank approximation (LRA). Reg. (4), as indicated before, modern TCAD workflows demand the interaction between different methods and tools each operating on different length scales, the workflows truly multi-scale in nature. Naturally, this introduces challenges with respect to interfaces but more importantly, the overall simulation runtime of the entire workflow is determined by its slowest part. Although advancements have been made with accelerating extremely demanding tools, such as DFT and NEGF, by parallelization, they are still confined to atomistic regimes (e.g., DFT) and only some can reach single-digit nanometer regimes (e.g., NEGF). This challenging situation seems to steadily improve as application of machine learning techniques for acceleration is widely researched [12, 13]. Reg. (6), depending on the definition, photonics can cover a wide range of applications, ranging from image sensors, lasers, displays, LEDs, and photovoltaics to integrated Si photonics platforms (Fig.4), with additional applications in photolithography, plasmonics, and optical metrology. Integrated Si photonics is a particularly interesting field of application, due to astonishing advancements in communication technologies and its compatibility with established fabrication flows in the semiconductor industry

Fig.4: 3D photonics simulation of a beam-splitting waveguide structure. Top: The wave guide is virtually constructed by process TCAD. A pre-calculated Eigenmode solution is injected at the left opening of the waveguide. Bottom: The solution is based on applying the finite difference time domain (FDTD) method, describing the propagated Eigenmode's electric field magnitude in the waveguide.

[14]. The underlying methods can be categorized in Eigenmode and wave propagation solvers (e.g., finite difference time domain (FDTD), discontinuous Galerkin time domain (DGTD)). Reg. (7), as previously indicated, (1-6) result in a drastic increase in design parameters and increased need for specialized simulation tools and optimization workflows. This together with the fact that simulation engineers are expected to be proficient in all here mentioned areas, not only increases the innovation pressure on TCAD vendors but also adds further pressure on recruiting and on the already over-strained workforce. It is thus of paramount importance for TCAD vendors to provide levels of abstraction and automation to their tools to hide complexity and to make modern TCAD workflows as accessible as possible to non-simulation experts. As we will see in the next section, artificial intelligence (AI) in general and machine learning (ML) in particular play a vital role in achieving this critical goal.

# III. CO-OPTIMIZATION AND DIGITAL TWINS

A key step towards overcoming the growing optimization complexities is based on automated, efficient, and iterative optimization flows, connecting process TCAD with device and circuit TCAD, called DTCO, see Section III.A. Recently, the concept was extended to FTCO<sup>TM</sup>, by adding AI/ML to the workflow, allowing to train a nonlinear model to become a DT, see Section III.B. Both have in common, that physical simulation is the foundation for being able to accurately describe fabrication process steps and device characteristics.

## A. Design Technology Co-Optimization

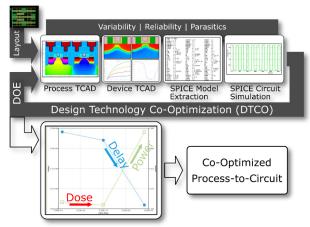

Already more than 10 years ago the challenge of a rapidly growing optimization space spanning a plethora of design and manufacturing dimensions was apparent and since then DTCO was key to tackling this challenge [5]. Fig. 5 showcases a DTCO application example, in which a ring-oscillator is co-optimized with respect to process and circuit parameters. DTCO allows to cross-correlate various parameters, allowing to navigate a vast optimization space.

Fig.5: A ring-oscillator is optimized using DTCO, allowing to consider various aspects of variability, reliability, and parasitics. Layout data of an NFET and PFET is input into a physical process TCAD simulation and the devices are virtually fabricated. The electrical characteristics is determined by a device TCAD simulation and the SPICE model parameters are extracted. The circuit is simulated and efficient design of experiments (DOE) algorithms are used to explore the optimization space: Relationships between process and circuit parameters are established. By way of example, the *dose* process parameter is linked to *delay* and *power* circuit parameters: The result shows that when increasing the dose, the delay can be reduced but power is increased.

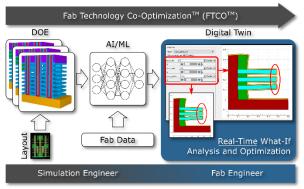

# B. Fab Technology Co-Optimization<sup>TM</sup> for Digital Twins

The ever-growing complexities involved in modern technologies and the need to minimizing cost, time-tomarket and maximizing production scale by reducing physical wafer learning cycles requires to conduct cooptimization workflows by fab and design houses in large scale. Although DTCO provides in principle the means to do that, it still requires a knowledgeable simulation engineer and significant amount of time to setup and execute. This serious challenge can be overcome by creating a DT. A DT is trained with AI/ML methods and an optimized DOE based on physical TCAD simulations and complementing experimental fab data and is made accessible to non-simulation experts, such as fab engineers. As such, the complexities of the TCAD workflow are abstracted, yielding an intuitive and interactive DT which can be used to analyze and optimize processes, designs, and yields in real time. Fig.6 depicts an exemplary FTCO<sup>TM</sup> flow applied to a NAND device related manufacturing sequence, showcasing how a DT is created and a nonsimulation expert can use the DT for analysis and optimization.

## IV. SUMMARY

TCAD evolved with the challenges of a high-pacing semiconductor industry and remains indispensable today. Co-optimization workflows using physical TCAD simulations, such as DTCO, are key for cutting-edge analyses and optimizations. Moving forward, an additional layer of abstraction is necessary to deal with ever-raising complexities. By applying FTCO<sup>TM</sup> workflows built on machine learning, DTs can be generated, allowing non-simulation experts, such as fab engineers, to analyze and optimize processes, designs, and yields in real time.

Fig.6: An example process FTCO flow applied to stress/strain modeling in NAND tier formation. After virtually fabricating the structure with process TCAD, a DOE is performed on key process parameters. Structural changes and critical metrics (e.g., angles) are modeled as function of key process parameters and AI/ML is used to train a nonlinear model which ultimately becomes the DT. The DT can be used to analyze and optimize in real-time the deformation of tiers as a function of key process parameters. Red arrows indicate real-time rendering of structure changes.

### V. References

- S. Cea, S. Berrada, K. Ghosh, S. Hasan, P. Keys, R. Mehandru, B. Obradovic, V. Tiwari, C. Weber and M. Stettler, "TCAD for logic technology process development," in SISPAD, 2021.

- [2] M. Stettler, S. Cea, S. Hasan, L. Jiang, A. Kaushik, P. Keys, R. Kotlyar, C. Landon, D. Pantuso, A. Slepko, S. Smith, V. Tiwari, C. Weber and J. R. Weber, "State-of-the-art TCAD: 25 years ago and today," in *IEEE IEDM*, 2019.

- [3] R. Rao, "4500 Fab Jobs Could Go Unfilled in U.S. by 2030," IEEE Spectrum, 2024.

- [4] "nanoHUB," [Online]. Available: https://nanohub.org/. [Accessed 23 06 2025].

- [5] G. Yeric, B. Cline, S. Sinha, D. Pietromonaco, V. Chandra and R. Aitken, "The past present and future of design-technology co-optimization," in *IEEE CICC*, 2013.

- [6] D. C. Cole, E. M. Buturla, S. S. Furkay, K. Varahramyan, J. Slinkman, J. A. Mandelman, D. P. Foty, O. Bula, A. W. Strong, J. W. Park, T. D. Linton Jr., J. B. Johnson, M. V. Fischetti, S. E. Laux, P. E. Cottrell, H. G. Lustig, F. Pileggi and D. Katcoff, "The use of simulation in semiconductor technology development," *Solid-State Electronics*, vol. 33, no. 6, pp. 591-623, 1990.

- [7] D. Esseni, C. Jungemann, J. Lorenz, P. Palestri, E. Sangiorgi and L. Selmi, "Technology Computer Aided Design," in *Guide to State-of-the-Art Electron Devices*, Wiley, 2013.

- [8] M. E. Law, "20 years of SISPAD: Adolescence of TCAD and further perspective," in SISPAD, 2016.

- [9] J. Cervenka, R. Kosik, M. Jech, M. Vasicek, M. Gritsch, S. Selberherr and T. Grasser, "Macroscopic Transport Models for Classical Device Simulation," in *Springer Handbook of Semiconductor Devices*, 2022, p. 1335–1381.

- [10] C. Klinkert, A. Szabo, C. Stieger, D. Campi, N. Marzari and M. Luisier, "2-D Materials for Ultrascaled Field-Effect Transistors: One Hundred Candidates under the Ab Initio Microscope," ACS Nano, vol. 14, no. 7, pp. 8605-8615, 2020.

- [11] P. Blaise, U. Kapoor, M. Townsend, E. Guichard, J. Charles and D. Lemus, "Nanoscale FET: How To Make Atomistic Simulation Versatile, Predictive, and Fast at 5nm Node and Below," in SISPAD, 2020.

- [12] M. H. Rahman and A. Mannodi-Kanakkithodi, "Defect modeling in semiconductors: the role of first principles simulations and machine learning," *JPhys Materials*, vol. 8, p. 022001, 2025.

- [13] T. Wang, Z. Wang, J. He, H. Wang and S. Chang, "Graph Representation Framework for Accelerating Atomic-Level Semiconductor Device Simulation," *IEEE Transactions on Electron Devices*, vol. 72, no. 5, pp. 2625-2632, 2025.

- [14] S. Shekhar, W. Bogaerts, L. Chrostowski, J. E. Bowers, M. Hochberg, R. Soref and B. J. Shastri, "Roadmapping the next generation of silicon photonics," *Nature Communications*, vol. 15, p. 751, 2024.