# Transport characterization and quantum dot coupling in commercial 22FDX®

<sup>1</sup>G.A. Elbaz, <sup>1</sup>P.-L. Julliard, <sup>2</sup>M. Cassé, <sup>2</sup>H. Niebojewski, <sup>2</sup>B. Bertrand, <sup>2</sup>G. Roussely, <sup>2</sup>V. Labracherie, <sup>1</sup>M. Vinet, <sup>1</sup>B. C. Paz, <sup>1</sup>T. Meunier <sup>1</sup>Quobly, Grenoble, France <sup>2</sup>Université Grenoble Alpes, CEA-LETI, Grenoble, France bruna.cardoso-paz@quobly.io

Abstract—Different groups worldwide have been working with the GlobalFoundries<sup>TM</sup> 22nm platform (22FDX®) with the hopes of industrializing the fabrication of Si spin qubits. To guide this effort, we have performed a systematic study of six of the foundry's processes of reference (POR). Using effective mobility as a figure of merit, we study the impact of gate stack, channel type and back bias as a function of temperature. This screening process selected qubit devices that allowed us to couple quantum dots along both the length and width of the Si channel. Simulations provide insights into potential technology optimizations and the advantages of leveraging forward body bias within an FDSOI qubit platform.

## Keywords—FDSOI, forward back biasing, TCAD, quantum dot.

#### I. INTRODUCTION

Significant advances have been made in the field of quantum computing, with the largest test platforms now surpassing a thousand physical qubits [1]. Many of these experimental platforms however are based on technologies that suffer from poor scalability. Leveraging CMOS manufacturing would enable the rapid scale-up of quantum computing hardware. As such, there has been considerable effort in the last 12 years [2] to develop the Si spin qubit and bring it to the 300mm scale. Among the commonly explored Si-based technologies, Fully Depleted Silicon-On-Insulator (FDSOI) has proven to be a promising forerunner [3]. FDSOI has a unique local back gate which offers very strong control over the transistor threshold voltage (V<sub>TH</sub>). In qubits, this back gate can also control the vertical position along the Si channel in which a quantum dot (QD) is formed, drawing it away from inherent defects at the front-gate Si/SiO2 interface and reducing the charge-noise associated with interface traps [4]. While some progress has been made to bring FDSOI spin qubits to the commercial scale [5-7], the deep cryogenic temperatures and long measurement protocols necessary to fully characterize qubits can be prohibitive in determining the efficacy and variability of a new process split. Rigorous characterization routines must be developed to screen potential qubit technologies and aid process development. Effective electron mobility is sensitive to many variables within the process flow and can shed light on both material and interface defects [8].

In this work, we present a detailed study on the effective mobility of six process splits from the GlobalFoundries<sup>TM</sup> 22nm platform (22FDX®), varying channel type, front-gate stack and front-gate equivalent oxide thickness (EOT). We use both temperature and back gate bias along with TCAD simulations to inform our understanding of the process splits and choose the best split and back bias conditions for forming QDs within the integrated qubit structures. Together, our data supports the selection of a thicker gate oxide in NMOS qubit arrays, which displays improved QD coupling relative to what has been reported for thinner gate oxides in 22nm FDSOI [6].

# II. DEVICES AND METHODOLOGY

All devices were fabricated using the commercially available 22FDX® platform from GlobalFoundries<sup>TM</sup> with their processes

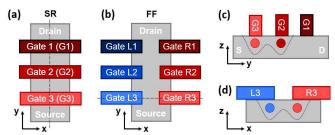

of reference (POR). The buried oxide and silicon channel in this technology are 20nm and 6nm thick, respectively. The commissioned wafers were designed with a wide range of inwafer and in-die process splits as well as integrated test structures which allowed us to screen several potential front and back gate stacks. The process splits discussed in this study are outlined in Table I. The first is focused on gate stack materials (GS-1 vs. GS-2), the second between thin (EOT-1 = 1.25 nm) and thick (EOT-2 = 3.4 nm) gate oxides. These were then tested on both n-type and p-type Si channels. Split C-V test structures were  $9\mu m \times 10\mu m$  transistors with a local back gate. Two styles of qubit devices were measured in this study: one which contains several gates in series (SR), with a similar design as in [9], and a second 2xN array of split gates in series, often called face-to-face (FF) gates [10].

|       | I ABLE I.       | IN DIE PROCESS SPLITS |              |

|-------|-----------------|-----------------------|--------------|

| Split | Gate Stack (GS) | Oxide (EOT)           | Carrier type |

| A     | GS-1            | Thin (EOT-1)          | PMOS         |

| В     | GS-2            |                       |              |

| C     |                 | Thick (EOT-2)         |              |

| D     | GS-1            | Thin (EOT-1)          | NMOS         |

| E     | GS-2            |                       |              |

| F     |                 | Thick (EOT-2)         |              |

Variable temperature I-V and C-V measurements were collected in a cryogenic Probe Station, using a commercial Semiconductor Device Parameter Analyzer and LCR-meter. QD experiments were carried out in a dilution refrigerator at 100mK. Simulations were carried out by Sentaurus TCAD from Synopsys Inc. Metal gate work functions and gate oxide dielectric constants were calibrated on experimental CV measurements. Density correction based on a quantum correction model was employed with the values calibrated in [11].

## III. QUBIT PROCESS-SPLIT PRE-SCREENING

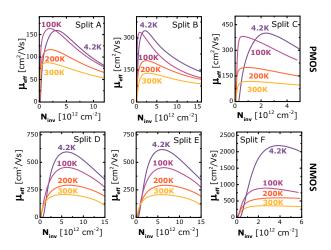

Carrier mobility is an important indicator for high-quality materials and therefore qubits. Using split C-V we screen the six potential process splits by studying the behavior of 22FDX® MOSFETs with lowering temperatures and back bias. Figure 1 plots the effective carrier mobility,  $\mu_{eff}$  as a function of temperature at zero body bias (ZBB,  $V_{BG} = 0$ ). As expected, the mobility of each device increases with decreasing temperature. However, some differences between PMOS and NMOS emerge. If we first compare gate stacks, this has a negligible effect on NMOS, while in PMOS the first gate stack (GS-1), consistently shows ~50% lower mobility than GS-2. If instead we compare the effects of equivalent oxide thickness, NMOS proves itself to be more sensitive. While PMOS EOT-2 does benefit from slight improvements in mobility (ex. – 334 vs. 401 cm<sup>2</sup>/Vs maximum at 4.2K), NMOS mobilities for EOT-2 are significantly larger than EOT-1 at every temperature, increasing from 1.7x to 3.6x greater at 300K and 4.2K respectively. This is in line with published results showing that mobility reduces with decreasing EOT for high-k gate oxides due to increased optical phonon scattering, whereas the quality of the high-k gate oxide determines the amount of remote charge scattering [12].

This work was supported in by the European Research Council (ERC) Synergy QuCube (grant number 810504), European Innovation Council (EIC) MCSQUARE (grant number 101136414), and the French National Research Agency under the program "France 2030" (PEPR PRESQUILE - ANR-22-PETQ-0002).

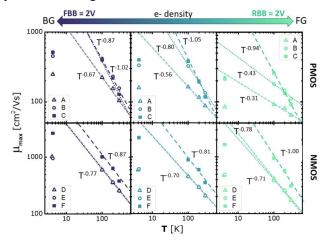

Fig. 1. Effective carrier mobility ( $\mu_{\rm eff}$ ) vs. the inversion charge density ( $N_{\rm inv}$ ) as a function of temperature for both front gate stacks and equivalent oxide thicknesses when  $V_{\rm BG} = 0V$  (ZBB).

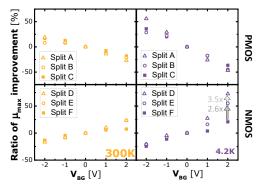

Fig. 2. Ratio of maximum effective mobility ( $\mu_{max}$ ) improvement w.r.t.  $V_{BG}$  = 0  $\nu s$ . the back gate voltage ( $V_{BG}$ ) at (left) 300K and at (right) 4.2K for the six process splits: GS-1 (triangle) and GS-2 (circle, square), EOT-1 (open markers) and EOT-2 (closed markers).

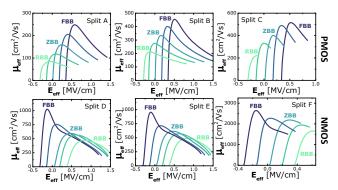

Irrespective of temperature, the back gate has a significant impact on the maximum  $\mu_{eff}$  ( $\mu_{max}$ ). In Fig. 2 we plot the relative change in  $\mu_{max}$  with applied back bias of  $\pm 1$ ,  $\pm 2V$  as compared to ZBB and look at how this difference is modified with temperature. To consistently compare NMOS and PMOS, we refer to these values as forward body biasing (FBB) and reverse body biasing (RBB), as the back bias polarity is inverted for the two channel types. In all cases, FBB (RBB) improves (decreases) the  $\mu_{max}$  but the FBB effect is notably strong at 4.2K for Splits D and E (EOT-1.) To take a closer look at the back-bias dependence at 4.2K, we plot  $\mu_{eff}$  vs. the effective electric field,  $E_{eff}$ , and  $V_{BG}$  in Fig. 3. The NMOS EOT-2 reaches a  $\mu_{max}$  of 2645cm<sup>2</sup>/Vs under FBB, at 4.2K. This maximum is on par with comparable FDSOI transistors with thicker gate oxides (EOT = 6nm) and no high-k [13]. This is significant because high-k materials are a known source of defects which degrade mobility by introducing more scattering centers when compared to SiO<sub>2</sub>. Moreover, the mobility for all NMOS under a FBB = 2V displays a change in slope at  $E_{eff} \approx 0MV/cm$  to 0.2MV/cm, which is indicative of two-channel conduction and suggests the presence of intersubband scattering (ISS) [14].

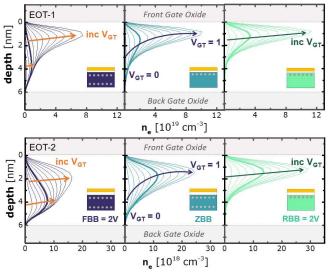

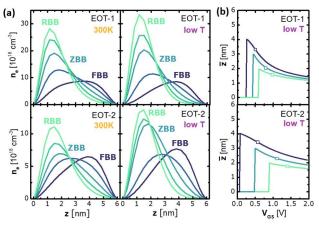

To confirm this, we performed TCAD simulations on NMOS EOT-1 and EOT-2. Fig. 4 and 5 show the relative electron density  $(n_e)$  as a function of position within the height of the channel ranging from a depth of 0 nm (front gate) to 6 nm (back gate), for both EOTs. In Fig. 4 we show the low temperature (low T) evolution of this density as a function of applied  $V_{GS}$ , starting from  $V_{GT}=0V$  and increasing to  $V_{GT}=1V$  while in Fig. 5a, we show the densities calculated at the applied- $V_{GS}$  where  $\mu_{max}$  occurs in the two devices at 300K and low T. In Fig. 5b we plot the mean

Fig. 3. Effective carrier mobility ( $\mu_{\rm eff}$ ) vs. the effective electric field ( $E_{\rm eff}$ ), as a function of applied back gate voltage ( $V_{\rm BG}$ ) at intervals of 1V (max =  $\pm 2$ V) for both front gate stacks and equivalent oxide thicknesses at 4.2K.

location of the normalized electron (ē) density within the channel ( $\bar{z}$ ) at low T as a function of  $V_{GS}$ .

From Fig. 5a we see that at ZBB the e<sup>-</sup> density is more evenly distributed within the channel for EOT-2; at  $\mu_{max}$  EOT-2 displays 9% and 5.5% more e<sup>-</sup> density than EOT-1 in the bottom half of the channel at 300K and low T, respectively. In agreement with experimental results, this decreases significantly for RBB (V<sub>BG</sub> = -2V), where 88-95% of the e<sup>-</sup> density is centered in the first 3nm of the channel in both device types. In comparison, more than half of the e<sup>-</sup> density can be found at the back interface (> 3nm) at  $\mu_{max}$ for FBB ( $V_{BG} = 2V$ ) at both temperatures and EOTs. In Fig. 4, we see that EOT-2 maintains a large e density at the back interface under FBB and high V<sub>GT</sub>. In fact, 40% of the e<sup>-</sup> density can be found at z > 3nm when  $V_{GT} = 1$ . This is in contrast to EOT-1 which only has 16%  $e^-$  density at its back interface at  $V_{GT} = 1$ . As seen in Fig. 5b, the average  $e^-$  position  $(\bar{z})$  for EOT-2 does not decrease below 3nm and move towards the front gate conduction channel until  $V_{GS} > 0.9V$  (i.e.  $V_{GT} > 0.7V$ ).

To fully understand the implications of these results, we return to the experimental data in Fig. 6 and plot  $\mu_{max}$  vs. temperature on a log-log scale as a function of gate stack and back gate bias ( $V_{BG}$ ). All devices above 100K display a power law  $T^{\gamma}$ , which has been shown to be primarily correlated with the mechanism for phonon scattering ( $\mu_{ph}$ ) within the device [15]. Combining these results with simulation, the differences observed in  $\gamma$  with back bias paint a clear picture. In EOT-1, the gate oxide is thin and the carriers thus experience more Coulomb scattering from the high-k above

Fig. 4. Low temperature simulation of electron density as a function of depth within the Si channel for NMOS EOT-1 (top) and EOT-2 (bottom) with  $V_{GT} = V_{GS} - V_{TH}$  ranging 0V to 1V (intervals of 100 mV).  $V_{GT}$  corresponding to  $\mu_{max}$  is shown in bold. Results are plotted for  $V_{BG} = 0V$  and  $\pm 2V$ , at 20K.

Fig. 5. (a) TCAD simulations of electron density ( $n_e$ ) vs. Si channel depth (z) at  $\mu_{max}$  for EOT-1 and EOT-2 at 300K and low temperature prior to any ISS as a function of applied back bias (intervals of 1V). (b) mean location of  $n_e$  ( $\overline{z}$ ) as a function of  $V_{GS}$  for forward (dark purple), zero (blue) and reverse (light green) body bias ( $V_{BG}$ = 0,  $\pm 2$ V). Open square marker corresponds to  $\mu_{max}$ .

when traveling near the top surface, as occurs with ZBB and RBB. The effect of this scattering is reduced under FBB, as the carriers are pulled down towards the back gate and  $\mu_{max}$  corresponds to an e<sup>-</sup> distribution primarily in the middle of the Si channel, particularly at warmer temperatures, leading to an increase in  $\gamma$ . In this regime, the quality of the BOX interface starts to have a stronger influence. In comparison, the thicker oxide of EOT-2 shifts the baseline conduction pathway of the carriers such that, under both ZBB and FBB, most of the carriers are found in the middle and back half of the channel respectively when  $\mu_{max}$  occurs, leading to  $\gamma$ -0.9 in EOT-2 under FBB. However, under RBB, while most of the carriers are drawn to the front interface for all  $V_{GS}$ , EOT-2 has much less Coulomb scattering, as the oxide used is thick enough to shield the carriers from the high-k above it, leading to an observed  $\gamma$ -1 for both carrier types.

Meanwhile, at carrier densities higher than that of  $\mu_{max}$ , the oscillations observed in electron carrier mobility under FBB along with the strong evidence for two-channel conduction suggest that the electron mobility in both EOT-1 and EOT-2 is degraded by ISS when operated at high inversion densities. The mobility improvements observed under FBB could therefore be limited by the interaction between front and back channels in ultrathin silicon films. This interaction, and subsequent ISS, may be ameliorated in thicker Si films, where the two conduction channels would be better physically separated, and should be considered for future quantum technologies.

Fig. 6. Maximum effective carrier mobility ( $\mu_{max}$ ) vs. temperature on log-log scale for GS-1 (triangle) and GS-2 (circle, square), EOT-1 (open markers) and EOT-2 (closed markers) for three  $V_{BG}$  values (0V,  $\pm 2$ V). A power law with temperature is shown for each case.

### IV. SPLIT F QUBIT LINEAR AND BILINEAR ARRAYS

With the insights from Section III, we selected Split F (NMOS, GS-2, EOT-2) operated under FBB as the best candidate for qubits. Schematics of our qubit devices can be found in Fig. 7. In SR devices (1xN arrays), QDs are coupled along the direction of the Si channel length (y-axis), as shown in Fig. 7c. In FF devices (2xN arrays), the coupling is opened to two dimensions and lateral coupling across the width of the Si channel (x-axis) is now feasible (Fig. 7d). The two-dimensional nature of this coupling makes our arrays compatible with the two most prevalent readout techniques for Si spin qubits today: RF-reflectometry [8] and nearby SET charge detection [15].

Fig. 7. (a) – (b) Top-down schematic of our qubit designs consisting of (a) three gates in series (SR device) and (b) three face-to-face or split gates (FF device). Gate pitch: 90nm, width: (a) 40nm (b) 70nm. (c) – (d) Cross-section schematic of two adjacent QDs coupled in (c) an SR device, along the y-axis and (d) an FF device, along the x-axis.

## A. SR devices: QDs coupled along the y-axis

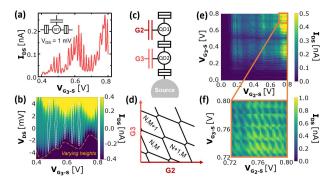

Operation in the SET regime requires a  $V_{DS}$  significantly smaller than the energy separation between subbands. The spaces between gates then act as barriers and promote 3D confinement. We therefore used  $V_{DS}=1 \mathrm{mV}$  and swept individual gates while operating the remaining front gates in the strong inversion regime. This configuration forms a single QD under the swept gate, while the other gates operate as extensions of the "reservoirs" (i.e., source and drain). Fig. 8a shows the results from one such set of sweeps as a function of G3 at  $V_{BG}=2V$ . The resulting  $I_{DS}$ - $V_{GS}$  displays many well-defined Coulomb peaks, with each peak corresponding to the addition of a single electron to the QD. The many equally spaced peaks indicate that a "true QD" has been created within our qubit device and the signal is not due to a dopant or other defect displaying quantum confinement-like behavior.

Next, we repeat this experiment varying V<sub>DS</sub>, and present the data in Fig. 8b. As expected for a QD SET, a diamond-like pattern is observed, (referred to as Coulomb diamonds), where a given diamond represents a stable N-electron configuration; within a diamond, no additional electrons can tunnel into the QD due to Coulomb blockade. From the heights and widths of the Coulomb diamonds, we can extract two important parameters for the QD: the charging energy,  $E_C$ , and the lever arm,  $\alpha$ . For G3, we calculate a range of charging energies, with E<sub>C</sub> varying between 2.0 and 4.5meV. This range stems from the irregularity of the Coulomb diamond heights and reveals some variability in the size of the QD. The source of this variability is likely due to a localized defect which is exerting unwanted electrostatic force on the QD. The lever arm  $(\alpha)$  is a measure of the electrostatic capacitive control the gate exerts on the QD and was found to range from 0.2 and 0.4 eV/V for the many Coulomb diamonds in Fig. 8b, which is on par with other CMOS-based QDs [16].

To couple multiple QDs, we repeat the  $I_{DS}$ - $V_{GS}$  under FBB (2V) at very low  $V_{DS}$  (1 mV) but as a function of two front gates rather than one (with the other front gate(s) still operated in the strong inversion regime.) In this case, two QDs are formed, one under each swept gate, as shown schematically in Fig. 8c. For two

Fig. 8. Process split F 1x3 (SR) qubit device operated under FBB in (a) – (b) the SET regime displaying characteristic (a) Coulomb peaks (b) Coulomb diamonds while sweeping G3. Several Coulomb diamonds are outlined in white to guide the eye. (c) Electronic schematic of two adjacent QDs coupled along the length of the Si channel (y-direction). (d) Theoretical stability diagram with the honeycomb pattern predicted for two coupled QDs. (e) and (f) Stability diagrams of two coupled quantum dots under FBB, located underneath gates G2 and G3, in an SR qubit device.

quantum dots capacitively and tunnel coupled, the 2D  $I_{DS}$ - $V_{GS}$  map of the two swept gates (*i.e.*, the stability diagram) should display a "honeycomb" pattern as depicted in Fig. 8d, which represents the equilibrium charge states of the coupled QDs. An angled slope of the vertical and horizonal lines indicates that the dots are capacitively coupled [17].

In Fig. 8e and 8f we show this stability diagram for our SR qubit device with two QDs formed under gates G2 and G3. In the many-electron regime, we see a clear honeycomb pattern in Fig. 8f, indicating that the two adjacent QDs are indeed capacitively and tunnel coupled. The barrier between the two QDs defines their coupling and is primarily determined by the gate pitch and  $V_{BG}$ . A gate spacing of 60nm is therefore large enough to form barriers within 22FDX® and define the quantum wells. To further fine tune this coupling and have individual control over this barrier, a second level of gates could be integrated. Alternatively, as demonstrated in [7], control over the barrier can be reached in linear arrays if the QDs are formed between the gates.

# B. FF devices: QDs coupled along the x-axis

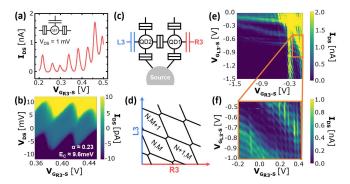

Many Si spin qubit devices rely on having a 2xN array-like structure such that one side of the array can be used to sense the other and read-out its state. Moreover, in this type of array, each qubit can have more closest "neighbors" (i.e., more entangled qubits). Therefore, it is also important to be able to couple QDs in the x-direction. We use our FF qubit device to probe this functionality in 22FDX®. As in the SR device, we observe many characteristic Coulomb peaks (Fig. 9a) and Coulomb diamonds (Fig. 9b), shown here for the bottom-right gate, R3. From the Coulomb diamonds we extract charging energy of 9.6meV and a lever arm of 0.23 eV/V. The larger  $E_C$  measured for the QD under gate R3 in this device implies that this quantum dot is smaller than the one measured in the SR qubit device. This is consistent with the difference in the gate areas between the two device styles, which changes from 1200nm<sup>2</sup> to 300nm<sup>2</sup> for SR and FF, respectively. The modification of the QD size with changing gate size is a good confirmation that the QDs that we are measuring are electrostatically defined underneath the front gates as desired.

To couple QDs in a face-to-face configuration, we again repeat the  $I_{DS}$ - $V_{GS}$  under FBB with very low  $V_{DS}$  but as a function of two parallel front gates. The resulting stability diagrams can be seen in Fig. 9e and 9f, where the quintessential angled honeycomb pattern is again observed, this time for the bottom left and right gates (L3 and R3).

Fig. 9. Process split F 2x3 (FF) qubit device operated under FBB in (a) - (b) the SET regime displaying characteristic (a) Coulomb peaks (b) Coulomb diamonds while sweeping R3. (c) Electronic schematic of two adjacent QDs coupled along the x-direction in an FF qubit device. (d) Theoretical stability diagram with the honeycomb pattern predicted for two laterally coupled QDs. (e) and (f) Stability diagrams of two coupled QDs under FBB, located underneath gates L3 and R3, in an FF qubit device.

Recent work in 22FDX® has been published on similar qubit layouts with the same reported gate stack as Split E: GS-2 and EOT-1 [6]. Under similar FBB values, the stability diagrams of these devices seem noisier and no clean double QD feature is observed. Comparison with these results further supports the selection of EOT-2 for 22FDX® qubits and suggests that our screening process is indeed working as advertised.

#### V. CONCLUSION

Using effective carrier mobility as a figure of merit, we screened six potential processes of reference from GlobalFoundries<sup>™</sup> and identified Split F (NMOS, GS-2, EOT-2) and FBB as the best conditions for 22FDX® qubits. Our commercially fabricated qubits formed capacitively- and tunnel-coupled QDs both along the Si channel as well as across it. This is evidenced by the characteristic honeycomb pattern clearly observed in the presented stability diagrams.

Our mobility results show that FBB is highly effective at reducing the scattering associated with the front gate, irrespective of EOT and gate stack materials. TCAD simulations confirm that this is due to the location within the channel that the carriers sit under bias. Moreover, the oxide in EOT-2 is more effective at shielding carriers from high-*k* defects, and with FBB allows one to achieve the same maximum effective mobility as similar devices with a thicker SiO<sub>2</sub> gate oxide. These improvements with FBB however may be limited by intersubband scattering, suggesting that even greater mobility improvements could be seen with FBB of thicker Si channel devices. Overall, this MOSFET screening process represents a viable characterization protocol that can be applied to future qubit nodes.

## REFERENCES

- [1] D. Castelvecchi, Nature, vol. 624, pp. 238, Dec. 2023.

- [2] J.J. Pla et al., Nature, vol. 489, pp. 541–545, Sep. 2012.

- [3] M. Urdampilleta et al., Nature Nanotech., vol. 14, pp. 737–741, May 2019.

- [4] C. Spence et al., Phys. Rev. Appl., vol. 19, pp. 044010, Apr. 2023.

- [5] I. Kriekouki et al., Sol. State Elec., vol. 194, No. 108355, Apr. 2022.

- [6] S. Bonen et al., *IEEE EDL*, vol. 45, No. 10, Oct. 2024.

- [7] S.V. Amitonov et al., arXix, Dec. 2024; DOI: 10.48550/arXiv.2412.08422.

- [8] M. Cassé et al., IEEE TED, vol. 53, No. 4, Apr. 2006.

- [9] R. Maurand et al., Nature Comm., vol. 7, No. 13575, Nov. 2016.

- [10] D.J. Niegemann et al., PRX Quantum., vol. 3, No. 040335, Dec. 2022.

- [11] N. Pons et al., 2013 SISPAD, pp. 184-187, Sep. 2013.

- [12] B. H. Lee et al., Materials Today, vol. 9 No. 6, pp. 32-40, Jun 2006.

- [13] G.A. Elbaz *et al.*, *ESSDERC 2023*, pp. 5-8, Sep. 2023.

- [14] M. Cassé et al., IEEE TED, vol. 67, No. 11, pp. 4636–4640, Nov. 2020.

- [15] S. Takagi et al., IEEE TED, vol. 41, No. 12, pp. 2357–2362, Dec. 1994.

- [16] B. Klemt et al., npj Quantum Info., vol. 9, No. 107, Oct. 2023.

- [17] W. G. van der Wiel et al., Rev. Mod. Phys., vol. 75, No. 1, Dec. 2002.