# Characteristic Variability of GAA Si NS CFETs Induced by Process Variation Effect and Intrinsic Parameter Fluctuation

Min-Hui Chuang

Institute of Communications Engineering and

Parallel and Scientific Computing Laboratory,

National Yang Ming Chiao Tung Univeristy,

Hsinchu 300093, Taiwan.

mhchuang@mail.ymlab.org

Sekhar Reddy Kola Parallel and Scientific Computing Laboratory, National Yang Ming Chiao Tung Univeristy, Hsinchu 300093, Taiwan sekhar.kola@mail.ymlab.org Yiming Li

Institue of Communications Engineering and

Parallel and Scientific Computing Laboratory,

National Yang Ming Chiao Tung Univeristy,

Hsinchu 300093, Taiwan

ymli@mail.ymlab.org

Abstract— We simultaneously estimate impacts of process variation effect (PVE) consisting of three major variations and intrinsic parameter fluctuation (IPF) including two crucial random factors on electrical characteristics of gateall-around silicon nanosheet complementary field-effect transistors (GAA Si NS CFETs). The combined influence of PVE and IPF on both N-/P-FETs in GAA Si NS CFETs results in significant fluctuation of the off-state current. This variability to PVE factors is particularly pronounced in the P-type device due to the parasitic nature of its bottom channel. Furthermore, compared with the magnitudes of dynamic and short circuit powers, the static power is marginal, but it possesses the largest fluctuation (about RSD of 82%). Notably, the statistical sum of each factors of fluctuation overestimates the total variability owing to ignoring the correlation effects among all random factors, compared with the full estimation at the same time.

Keywords—GAA NS CFETs, Process Variation Effects, Intrinsic Parameter Fluctuation, Power Fluctuation. Deviation.

## I. INTRODUCTION

The aggressive scaling of devices has led to pronounced short-channel effect (SCE) and reduced gate control, resulting in significant leakage currents [1], [2]. To address this issue, semiconductor industry has focused on GAA structures, including nanowire (NW) and nanosheet (NS) MOSFETs [3]-[5]. These devices are particularly noteworthy for their ability to lower supply voltages, maintain strong gate control, and achieve high performance at advanced technology nodes [6]. Currently, GAA NS MOSFETs are being developed as promising solutions for logic and memory devices beyond 2 nm technology nodes [7]. However, as these devices are scaled down, they encounter inherent physical challenges associated with the complexities of device fabrication [8]. Recent advancements in emerging VLSI technologies have introduced the concept of GAA NS CFETs [1], [9], [10]. However, their fabrication process of CFETs possesses less repeatability during channel etching and gate metal deposition [1], [9]. Various variation factors of PVE and IPF including work function fluctuation (WKF), random dopant fluctuation (RDF), and interface trap fluctuation (ITF) are critical factors in VLSI devices [11]-[13]; in particular, for emerging CFET devices [1], [14]. Recent studies have investigated these factors in planer MOSFETs, FinFETs, GAA NW and NS MOSFETs [11], [12], [15]. However, the influence of PVE and IPF factors on electrical characteristics and power analysis of CFET devices and circuit has not received sufficient attention.

In this work, we comprehensively undertake a computational analysis of the combined PVE and IPF on characteristics fluctuation including power consumption of GAA Si NS CFETs. To provide engineering reasonable

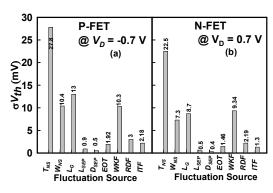

Fig. 1. Comparative analysis of fluctuation sources, including PVE, WKF, RDF and ITF, at  $|V_{\rm D}|=0.7$  V. The results lead to the conclusion that the variation in  $V_{\rm th}$  caused by ITF is significantly lesser than that induced by PVE, WKF, and RDF. Consequently, the subsequent discussion neglects the ITF effect. (a) P-FET and (b) N-FET.

Fig. 2. (a) A scattering plot of  $I_{off}$ - $I_{on}$  with respect to six PVE factors, WKF, RDF, and ITF in (a) N-FET and (b) P-FET. The significant variation and random factors can be observed.

accuracy of device simulation, not shown here, we do calibrate our calculation with measured data first [9], [16], [17]. We then evaluate overall fluctuations induced by PVE and IPF by estimating the relative standard deviation (RSD) which is the ratio of standard deviation to the mean value (i.e., RSD =  $(\sigma/\mu)$  x 100%) for each figure of merit.

# II. II THE STATISTICAL SIMULATION OF PVE AND IPF

Figures 1(a)-(b) illustrate the standard deviation of  $V_{th}$  for primary fluctuation sources, including six individual PVE factors, as well as WKF, RDF, and ITF for both N- and P-FETs. Notably, among the PVE factors,  $T_{NS}$ ,  $W_{NS}$ , and  $L_G$ ,

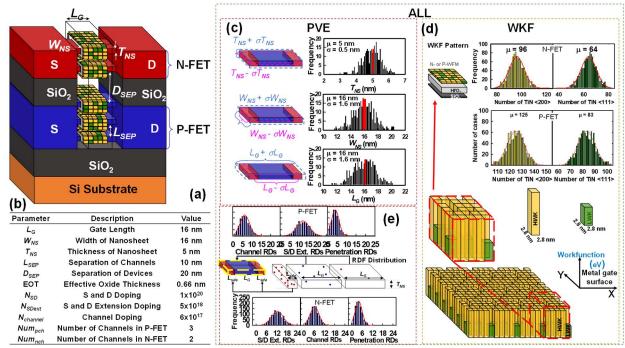

**Fig. 3.** (a) A 3-D schematic plot of the GAA Si NS CFET. (b) Partially list of the nominal values of parameters. (c) Illustration of the fluctuation sources and the Gaussian distribution histogram of the generated random cases. (c) PVE factors variation. (d) For WKF, each GAA channel's N-/P-work function metal (WFM) is discretized into small metal grains. (e) For RDF, the mean value of the number of S/D extension. channel. and penetration RDs are equivalent to the nominal doping concentration.

**Table 1.** List of RSD of DC/AC characteristics with individual PVE and IPF, and combined variation sources.

| RSD (%)               |       | T <sub>NS</sub> | W <sub>NS</sub> | L <sub>G</sub> | WKF  | RDF  | ALL  | SUM   |

|-----------------------|-------|-----------------|-----------------|----------------|------|------|------|-------|

| Ion                   | N-FET | 9.35            | 6.4             | 1.6            | 3.9  | 1.3  | 10.8 | 12.2  |

|                       | P-FET | 14.4            | 10.4            | 3.27           | 2.3  | 2    | 13   | 18.3  |

| I <sub>off</sub>      | N-FET | 50.4            | 30.1            | 37.5           | 60.5 | 10.1 | 65   | 92.8  |

|                       | P-FET | 123             | 45.3            | 57.4           | 48.4 | 21.7 | 131  | 152.6 |

| V <sub>th</sub>       | N-FET | 3.3             | 3.1             | 2.4            | 4.9  | 8.0  | 4.9  | 7.14  |

|                       | P-FET | 4.6             | 3.8             | 3.5            | 3.4  | 1.1  | 6.1  | 7.79  |

| DIBL                  | N-FET | 14.4            | 12.7            | 5.6            | 16.6 | 5.82 | 17.7 | 26.6  |

|                       | P-FET | 16.5            | 13.5            | 8.2            | 9.8  | 5.89 | 20.7 | 25.5  |

| ss                    | N-FET | 1.05            | 0.95            | 1.0            | 23.7 | 26.4 | 1.1  | 35.5  |

|                       | P-FET | 4.8             | 2.8             | 1.94           | 42.6 | 21.8 | 4.5  | 48.2  |

| <b>g</b> <sub>m</sub> | N-FET | 7.5             | 9.76            | 3.4            | 45.2 | 11   | 9.3  | 48.2  |

|                       | P-FET | 16.9            | 10.2            | 5.43           | 42.6 | 16.2 | 78   | 50.0  |

| C <sub>G</sub>        | N-FET | 5.0             | 7.9             | 9.7            | 1.78 | 5.8  | 12.9 | 14.8  |

|                       | P-FET | 6.0             | 9.9             | 10.5           | 1.58 | 8.1  | 14.4 | 17.7  |

along with IPF factors such as WKF and RDF, exhibit significant variations in V<sub>th</sub>. As shown in Fig. 2, we first examine the main variation sources and find that the oxide thickness, channel separation, device separation, and ITF are marginal to CFET characteristic variation [17]; therefore, we will mainly focus on the three key variation components of PVE, i.e., thickness of nanosheet  $(T_{NS})$ , width of NS  $(W_{NS})$ and channel length  $(L_G)$  and two IPF: WKF and RDF. The numeric range of these parameters varies within the constraints of  $\pm \sigma$ , following the guidelines of the 2022 IRDS roadmap [18]. Figure 3(a) shows a 3-D schematic illustration of the GAA Si NS CFET structure. This configuration features two GAA channels for bottom P-FET, along with one parasitic channel. On the other hand, the top N-FET is designed with two GAA channels, ensuring  $I_{on}$  characteristics match for both the devices. To ensure precision and accuracy, we have meticulously calibrated our device simulation using measured data as reported in our recent work [19]. The parameters adopted for device simulation follow rigorous calibration with

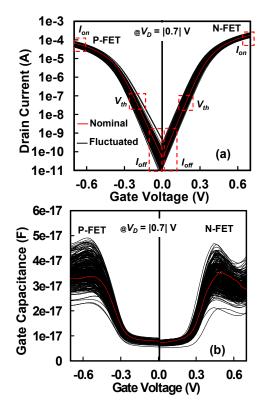

**Fig. 4.** (a) The  $I_D$ - $V_G$  curves exhibit fluctuations for both N-FETs and P-FETs of CFET devices resulting from the combined impact of PVE and IPF. (b) AC curves operating at a signal frequency of 1 GHz serves as the basis for assessing the gate capacitance ( $C_G$ ).

measured I-V curves of CFET, as shown in Fig. 3(b). The 3-D device simulation is realized by solving the quantum-mechanically corrected drift-diffusion model. We have similarly applied these calibration methodologies and models

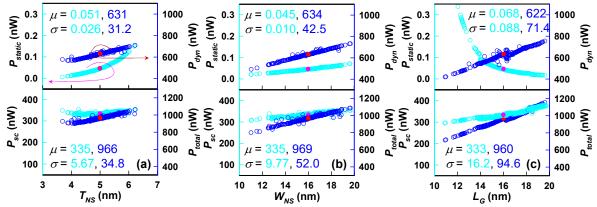

Fig. 5. Variations in  $P_{static}$ ,  $P_{dyn}$ ,  $P_{sc}$ , and  $P_{total}$  with respect to three major PVE factors: (a)  $T_{NS}$ , (b)  $W_{NS}$ , and (c)  $L_G$  for N- and P-FETs of CFET.  $P_{sc}$  and  $P_{dyn}$  increase when all factors increase.  $P_{static}$  is inversely proportional to  $L_G$  owing to the variation of  $I_{off}$ .

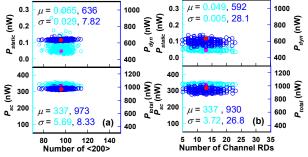

**Fig. 6.** Power variations with respect to two key IPF factors: WKF and RDF. Power variation vs. (a) the number of <200> and (b) the number of channel RDs in P-FET.

**Fig. 7.** Power variations with respect to two key IPF factors: WKF and RDF. Power variation vs. (a) the number of <200> and (b) the number of channel RDs in N-FET.

**Table 2.** Comparison of RSD of power components between the simultaneously simulation (*ALL*) and statistical estimation (*SUM*) based on the independent and identically distributed assumption. The overestimation of *SUM* occurs because factor by factor calculation ignores their possible interactions.

| RSD<br>(%)          | TNS  | W <sub>NS</sub> | <b>L</b> G | WKF  | RDF  | ALL  | SUM  |  |  |  |  |

|---------------------|------|-----------------|------------|------|------|------|------|--|--|--|--|

| P <sub>static</sub> | 48.7 | 21.4            | 101        | 34.6 | 10.6 | 82.1 | 120  |  |  |  |  |

| P <sub>dyn</sub>    | 4.92 | 6.65            | 11.7       | 1.23 | 4.73 | 13.0 | 15.1 |  |  |  |  |

| Psc                 | 1.70 | 2.91            | 6.10       | 1.69 | 1.10 | 6.15 | 7.26 |  |  |  |  |

| Ptotal              | 3.61 | 5.23            | 9.61       | 0.86 | 2.88 | 10.3 | 11.9 |  |  |  |  |

to simulate the impact of PVE and IPF. Our mobility models incorporate various critical elements, such as the Philips unified model and a high-field saturation model dependent on surface orientation, which addresses phonon and Coulomb scatterings at the channel/insulator interface. To account for quasi-ballistic effects, we have included the low-field ballistic mobility model. In addition, our analysis considers Hurkx band-to-band tunneling and the Shockley-Read Hall

**Fig. 8.** (a)  $P_{static}$  and  $P_{dyn}$  and (b)  $P_{sc}$  and  $P_{total}$  versus the normalized factors of PVE and IPF are shown. They consider the combination of PVE and IPF factors at the same time. Notably, the trend of  $P_{static}$  follows the trend of  $L_G$  in Fig. 5(c).

recombination mechanism. A substantial dataset of 300 samples has been randomly generated, adhering to a Gaussian distribution, to comprehensively assess the influence of PVE and IPF on device characteristics. For WKF, we employ TiN and TiN is assigned with probabilities of 60% for <200>orientation and 40% for <111>-orientation. Furthermore, the work function of TiN <200> and <111> is 4.53 eV (high work function; HWK) and 4.33 eV (low work function; LWK), respectively, resulting in an effective work function of 4.45 eV. On the other hand, for P-FET, we utilize TiN doped with aluminum (Al), as shown in Fig. 3(c). About RDF, we randomly generate dopants which contribute to equivalent doping concentrations of  $8\times10^{17}$ ,  $2\times10^{19}$ , and  $3.4\times10^{17}$  cm<sup>-3</sup> for the channel, source (S)/drain (D) extension ( $S_{ext}/D_{ext}$ ), and penetration from the S/D extensions into the channel (PE), as depicted in Fig. 2(c). The statistical simulation follows one of our earlier works in [15].

### III. RESULTS AND DISCUSSION

Figs. 4(a)-(b) show the fluctuation of  $I_D$ - $V_G$  and  $C_G$ - $V_G$  affected by the PVE and IPF at the same time. The red curves of Fig. 4 are the nominal devices without any factors of PVE and IPF. Fluctuations in the off-state current are observed for both N-/P-FETs. Particularly, the P-FET has noticeable

fluctuation than that of N-FET due to the bottom parasitic channel leakage. The statistical *RSD<sub>SUM</sub>* (denoted as *SUM*) of the RSD variation of individual random source is given by

$$RSD_{SUM} = \sqrt{\sum RSD_i^2}\,, \qquad i \in \{PVE, IPF\},$$

where the PVE has the components:  $T_{NS}$ ,  $W_{NS}$ , and  $L_G$ , and the IPF has factors of WKF and RDF. The largest RSD variation occurs in  $I_{off}$  of P-FET and is found to be 131%, which indicates that PVE sources have a more dominant influence on characteristics fluctuation compared to combined random sources. The majority of carrier's transport is governed by a large GAA channel that controls the majority of carrier's flow. Due to the fact that plenty of carrier's transport is controlled by the GAA along the channel direction, it is possible to control the scattering of carrier by adjusting the effects of three sensitive PVE factors on  $I_{off}$ . Notably, when considering their interaction through individual statistical summation, it becomes evident that all outcomes for various physical quantities are overestimated compared to the simultaneous consideration of all factors due to their mutual annihilation and enhancement effect. The  $C_G$ , a key AC characteristic, is directly extracted from the C-V curves under the strong inversion region for both N- and P-FETs. Fig. 4(b) portrays the fluctuation of  $C_G$ - $V_G$  characteristics due to the combined influence of PVE and IPF. The RSD variations of  $C_G$  for P-FET is 14%. Tab. I lists the extracted DC/AC characteristics. By assuming independent and identical distribution of PVE and IPF factors, Tab. I show their statistically calculated RSD<sub>SUM</sub> via the equation which is about 50% overestimation, compared with results of PVE and IPF simultaneously. Among all characteristics, the RSD<sub>SUM</sub> shows the most severe overestimation (32 times) in SS of N-FET. Notably, in most situations,  $RSD_{SUM}$  is larger than  $RSD_{ALL}$ , only for the  $g_m$  of P-FET, it is lower. **ALL** denotes the simulation by considering all variation factors and random sources simultaneously.

Fig. 5 is the power fluctuations caused by the PVE factors. Since  $T_{NS}$  is below 10 nm, where the quantum effect occurs, the PVE on the static power ( $P_{static}$ ) shows a larger influence compared with  $W_{NS}$  while they have similar performance on the other power components.  $L_G$  shows an opposite influence on  $P_{static}$  due to the increased gate leakage from short-channel effect; in addition, it exhibits the most significant variation on  $P_{static}$ . The power fluctuation caused by the WKF and RDF of the P- and N-FETs is shown in Figs. 6 and 7. Tab. II lists the RSD values for different fluctuation sources. The RSDs of  $P_{static}$ ,  $P_{dyn}$ ,  $P_{sc}$ , and  $P_{total}$  are 82.1%, 13.0%, 6.15%, and 10.3%, respectively. Comparison of RSD of power components between **ALL** and **SUM** is shown. Notably, the overestimation of SUM occurs because factor by factor calculation ignores their possible interactions. Thus, to estimate truly impact of PVE and IPF on the variability of CFETs, ALL simulation is indispensable approach. Notably, the statistical RSD<sub>SUM</sub> of  $P_{static}$  results in significant overestimation, compared with RSD<sub>ALL</sub>. Fig. 8 is the scattering plot of power components considering all the fluctuation sources simultaneously.

## IV. CONCLUSIONS

In summary, we have studied the PVE and IPF on the explored devices; in particular, for P-FETs, 131% variation in  $I_{off}$  under the influence of these combined random sources was observed.  $P_{static}$  shows the most significant variation, reaching up to RSD of 82% during the off-state operation of CFETs, among all power components. Notably, there is a large

overestimation in RSD of  $P_{static}$  by implementing the statistical  $RSD_{SUM}$  to the results from the individual fluctuation factors.

### ACKNOWLEDGMENT

This work was supported in part by the National Science and Technology Council (NSTC), Taiwan, under grants NSTC 112-2221-E-A49-171, NSTC 113-2221-E-A49-094, and NSTC 113-2218-E-006-019-MBK.

### REFERENCES

- B. Vincent et al., "A Benchmark Study of Complementary-Field Effect Transistor (CFET) Process Integration Options Done by Virtual Fabrication," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 668–673, 2020.

- [2] N. Aruna Kumari et al., "Design and Analysis of dual-k spacer CombFET for Digital and Synaptic Applications," *IEEE Access*, pp. 1– 10, 2024.

- [3] S. Chang et al., "First Demonstration of CMOS Inverter and 6T-SRAM Based on GAA CFETs Structure for 3D-IC Applications," in *IEDM*, pp. 254–257, 2019.

- [4] S. R. Kola et al., "A Unified Statistical Analysis of Comprehensive Fluctuations of Gate-All-Around Silicon Nanosheet MOSFETs Induced by RDF, ITF, and WKF Simultaneously," in Int. Symp. Qual. Electron. Des., pp. 1–6, 2022.

- [5] V. B. Sreenivasulu *et al.*, "Exploring the Performance of 3-D Nanosheet FET in Inversion and Junctionless Modes: Device and Circuit-Level Analysis and Comparison," *IEEE Access*, vol. 11, pp. 90421–90429, 2023.

- [6] N. Seoane et al., "Simulations of statistical variability in n-Type FinFET, nanowire, and nanosheet FETs," *IEEE Electron Device Lett.*, vol. 42, no. 10, pp. 1416–1419, 2021.

- [7] S. R. Kola et al., "Statistical 3D Device Simulation of Full Fluctuations of Gate-All-Around Silicon Nanosheet MOSFETs at Sub-3-nm Technology Nodes," 2022 Int. Symp. VLSI Technol. Syst. Appl. VLSI-TSA 2022, pp. 2021–2022, 2022.

- [8] X. Shi et al., "A Simulation Study of Junctionless Forksheet on Sub-2 nm Node Logic Applications," *IEEE Trans. Electron Devices*, vol. PP, pp. 1–6, 2023.

- [9] C. Y. Huang *et al.*, "3-D self-aligned stacked NMOS-on-PMOS nanoribbon transistors for continued moore's law scaling," in *IEDM*, pp. 20.6.1-20.6.4, 2020.

- [10] X. R. Yu et al., "Integration Design and Process of 3-D Heterogeneous 6T SRAM with Double Layer Transferred Ge / 2Si CFET and IGZO Pass Gates for 42 % Reduced Cell Size," in IEDM, pp. 487–490, 2022.

- [11] Y. Li et al., "A unified 3D device simulation of random dopant, interface trap and work function fluctuations on high-κ/metal gate device," in *IEDM*, pp. 107-110, 2011.

- [12] Y. Li and C. H. Hwang, "The effect of the geometry aspect ratio on the silicon ellipse-shaped surroundinggate field-effect transistor and circuit," Semicond. Sci. Technol., vol. 24, 2009.

- [13] Y. Li, C. H. Hwang, and H. M. Huang, "Large-scale 'atomistic' approach to discrete-dopant-induced characteristic fluctuations in silicon nanowire transistors," *Phys. Status Solidi Appl. Mater. Sci.*, vol. 205, pp. 1505–1510, 2008.

- [14] X. Yang et al., "Impact of Process Variation on Nanosheet Gate-All-Around Complementary FET (CFET)," IEEE Trans. Electron Devices, vol. 69, no. 7, pp. 4029–4036, 2022.

- [15] Y. Li et al., "Process variation effect, metal-gate work-function fluctuation and random dopant fluctuation of 10-nm gate-all-around silicon nanowire MOSFET devices," in *IEDM*, pp. 887–890, 2015.

- [16] R. Butola et al., "Estimating the Process Variation Effects of Stacked Gate All Around Si Nanosheet CFETs Using Artificial Neural Network Modeling Framework," in Proc. IEEE Conf. Nanotechnol., pp. 170– 173, 2022.

- [17] S. R. Kola, Y. Li, and M.-H. Chuang, "Intrinsic Parameter Fluctuation and Process Variation Effect of Vertically Stacked Silicon Nanosheet Complementary Field-Effect Transistors," in *Int. Symp. Qual. Electron. Des.*, pp. 383–390, 2023.

- [18] "IRDS 2022: Executive Summary," 2022.

- [19] S. R. Kola and Y. Li, "Electrical Characteristic and Power Fluctuations of GAA Si NS CFETs by Simultaneously Co•nsidering Six Process Variation Factors," *IEEE Open J. Nanotechnol.*, vol. 4, pp. 229–238, 2023