# An Improved Overlap Capacitance Model for LDMOS Transistors based on the BSIM-BULK Framework

# Ayushi Sharma

Electrical Engineering Department

Indian Institute of Technology

Kanpur, India

sayushi@iitk.ac.in ©

Ravi Goel *DES*

Infineon Technologies AG Germany

Munich, Germany

Ravi.Goel@infineon.com

Ahtisham Pampori *EECS*

University Of California, Berkeley California, Berkeley pampori@berkeley.edu <sup>©</sup>

Ahmed Mahmoud *PSS*

Infineon Technologies AG Germany Munich, Germany Ahmed.Mahmoud@infineon.com Mingchun Tang DES

Infineon Technologies AG Germany Munich, Germany MingChun.Tang@infineon.com

Volker Kubrak

DES

Infineon Technolgies AG Germany Munich, Germany Volker.Kubrak@infineon.com

Chenming Hu *EECS*

University Of California, Berkeley California, Berkeley hu@eecs.berkeley.edu • Yogesh Singh Chauhan

Electrical Engineering Department

Indian Institute of Technology

Kanpur, India

chauhan@iitk.ac.in ©

Abstract—The gate-drain capacitance ( $C_{GD}$ ) affects the input and output impedance of transistors, necessitating designers to consider it for proper matching and interfacing with other circuit elements. For Laterally Diffused Metal-Oxide-Semiconductor (LDMOS) transistors, the drift region overlap capacitance is a key contributor to  $C_{GD}$ .  $C_{GD}$  gradually decreases with drain voltage ( $V_D$ ) and eventually saturates. However, before saturating, we observe a stepped decline in  $C_{GD}$  at higher  $V_D$ . This article provides physical insights into this step reduction of capacitance using Technology Computer-Aided Design (TCAD) simulations. Using the industry-standard BSIM-BULK model as a framework, we present an improved overlap capacitance model and validate it against measured LDMOS characteristics.

Index Terms—BSIM-BULK, overlap, C<sub>GD</sub>, and LDMOS.

### I. INTRODUCTION

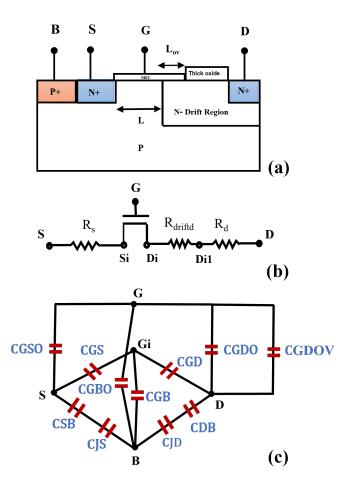

LDMOS transistors are fundamental to circuits such as power amplifiers, switch-mode power supplies, and other electronic applications [1]–[4]. Fig. 1 (a) shows a simple schematic of an n-LDMOS transistor where a lightly doped n-drift region is connected between the gate edge and the drain terminal to sustain a high drain voltage ( $V_D$ ). In BSIMBULK, the drift region is modeled as a bias-dependent drift resistance ( $R_{drift}$ ) connected between nodes  $D_i$  and  $D_{i1}$  as shown in the equivalent circuit diagram Fig. 1 (b) [5].  $R_d$  and  $R_s$  are the drain and source contact resistances respectively. The drift region has two distinct regions: one under the thin gate oxide ( $L_{ov}$ ) and the other under a thick oxide. The BSIM-BULK model, based on a physical charge-based

core, calculates the capacitance of the intrinsic MOSFET and gate overlap drift region separately [6]. The capacitance equivalent of the LDMOS transistor is shown in Fig. 1 (c). In the absence of an inversion layer in the OFF state, the contribution of the intrinsic capacitance becomes negligible, and the overlap capacitance dominates. CGSO and CGDO denote the overlap capacitance contribution of the Lightly Doped Source/Drain (LDD) region, while CGDOV is the overlap capacitance contribution from the gate overlap on the drift region under the thin gate oxide. The gate-to-drain overlap capacitance in LDMOS transistors impacts the highfrequency response, the linearity of the power amplifiers, and the switching speed of the device. Therefore, accurate modeling of the overlap capacitance is essential for state-ofthe-art technology [7], [8]. The existing BSIM-BULK model accurately captures the overlap capacitance due to the LDD region in low voltage MOSFETs [9]. Still, the existing overlap capacitance model of the drift region in BSIM-BULK does not capture the measured characteristics. With the application of V<sub>D</sub>, C<sub>GD</sub> gradually decreases and eventually saturates in the case of an LDD MOSFET. In our previous work [10], we provided a physical explanation and presented a compact model that accurately captures the capacitance under different bias conditions. However, in the case of an LDMOS transistor, the applied V<sub>D</sub> is high, and we observe a step-like behavior in C<sub>GD</sub> before it gets saturated. Numerous studies have focused on the capacitance behavior of the LDMOS transistor without

Fig. 1. (a) Simple schematic of an n-LDMOS transistor, (b) Its equivalent circuit. (c) Capacitance equivalent of an LDMOS transistor for both intrinsic and extrinsic MOSFET.

discussing the step behavior in  $C_{GD}$  or the underlying physics that explains the phenomenon [11]–[13]. In [14], the step behavior is modeled by limiting the applied  $V_{DG}$ . An overlap capacitance model is presented in [15], but the step behavior in  $C_{GD}$  is not discussed. To bridge this gap, we present an improved gate overlap drift region capacitance model that accurately captures the capacitance behavior at high voltages under the BSIM-BULK framework.

### II. ANALYSIS OF THE EXISTING MODEL

The gate-drain capacitance contribution due to the drift region is determined by the gate overlap drift length  $(L_{ov})$ , which undergoes accumulation, depletion, or inversion depending on the applied gate and drain voltage. The overlap charge due to drift region is given by (1) [6], [9]. In BSIMBULK,  $L_{ov}$  is defined as a model parameter LOVER,  $C_{ox}$  is the oxide capacitance, and  $V_t$  is the thermal voltage.  $q_{drift}$  is the inversion and accumulation charge below the gate overlap of the drift region that is determined, as in the core BSIM-BULK model, by analytically solving  $\Psi_{p,drift}$  from (2).  $\Psi_{p,drift}$  is the flatband

voltage of the drift region, and VFBOV is a model parameter to tune  $V_{\text{fb,drift}}$ .

$$Q_{\text{GDOV}} = W \cdot LOVER \cdot C_{\text{ox}} \cdot V_{\text{t}} \cdot q_{\text{drift}} \tag{1}$$

$$V_{\text{fb, drift}} = \Psi_{p,drift} - \gamma \cdot \sqrt{e^{-\Psi_{p,drift}} - 1 + \Psi_{p,drift}}$$

(2)

$$V_{\text{fb, drift}} = \frac{V_{\text{G, D}} - VFBOV}{V_t} \tag{3}$$

$$\gamma = \frac{2 \cdot q \cdot \epsilon \cdot NDR}{C_{ox} \cdot \sqrt{V_t}} \tag{4}$$

$$q_{\text{drift, inv}} = 2 \cdot n_{\text{q}} \cdot q_{\text{inversion}}$$

(5)

$$q_{\rm drift, \ acc} = V_{\rm fb, \ drift} - \Psi_{p, drift} - 2 \cdot n_{\rm q} \cdot q_{\rm inversion} \tag{6}$$

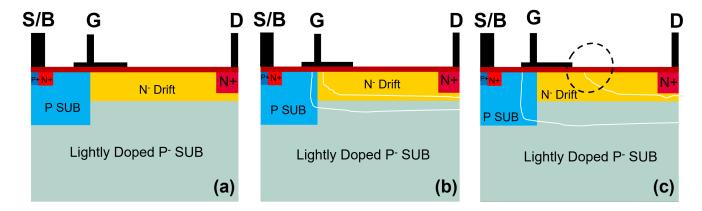

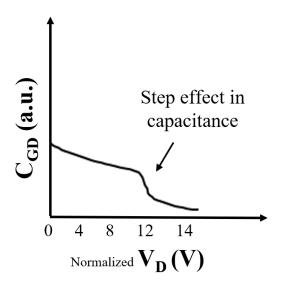

The inversion, depletion and accumulation charge is then given by (5) and (6). From the above equations, we conclude that the depletion charge in the drift region increases with V<sub>D</sub>, the rate of change of Q<sub>GDOV</sub> slows down, and C<sub>GD</sub> gradually decreases with V<sub>D</sub>. But, the existing model does not have the step decline in C<sub>GD</sub> with V<sub>D</sub> as observed in the measured data. We performed 2-D numerical device simulations using TCAD on the LDMOS FET structure, as shown in Fig. 2 (a), to understand the physics behind the abrupt change in C<sub>GD</sub>. In Fig. 2 (b), a depletion region forms below the gate at the N-drift and P-substrate junction at moderate V<sub>D</sub>. If the applied V<sub>D</sub> is further increased, the drift region is depleted and extends beyond the gate overlap length, as shown in Fig. 2 (c). From TCAD analysis, we infer that the depletion charge moves beyond the gate overlap as V<sub>D</sub> increases. This reduces the contribution of the accumulation region (under the overlap gate length (LOVER)) to the gate-drain capacitance. As a result, we see a sudden drop in C<sub>GD</sub> with a steep slope as shown in Fig. 3.

### III. MODELING OF STEP CAPACITANCE BEHAVIOR

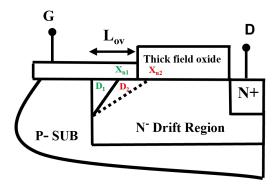

Fig. 4 schematically highlights the depletion region under the gate overlap length. When a moderate  $V_D$  is applied, the depletion region  $D_1$  below the gate overlap extends up to  $X_{n1}$ . Further increase in  $V_D$  extends the depletion region  $D_2$  beyond gate overlap length upto  $X_{n2}$ . The depletion width  $W_{\text{dep,dr}}$  can be expressed as (7), where  $N_{Dr}$ ,  $N_{\text{sub}}$  are the drift and substrate region doping concentration, respectively.  $V_{\text{bi,dr}}$  is the built-in voltage for the drift and substrate junction,  $\epsilon_s$  is the silicon permittivity, and q is the electronic charge. With the doping concentration in the drift region being less than the substrate, the depletion width primarily extends in the drift region and moves beyond the gate overlap length (LOVER) with increasing  $V_D$ .

$$W_{\text{dep,dr}} = \sqrt{\frac{2 \cdot \varepsilon_s \cdot (V_D + V_{\text{bi,dr}})}{q} \cdot \left(\frac{1}{N_{\text{Dr}}} + \frac{1}{N_{\text{sub}}}\right)}$$

(7)

This reduces the effective contribution of the accumulation region (LOVER) to the gate-drain capacitance. We then model the modified overlap gate length as (8), correctly

Fig. 2. Shows 2-D Numerical device simulation contour plots (a) LDMOS FET structure on which TCAD simulations are performed, (b) Moderate  $V_D$  is applied in OFF state, due to which depletion region is generated at the P substrate and N drift junction, (c) as higher  $V_D$  is applied, further depletion occurs in the lightly doped N drift region which goes beyond gate overlap length on the drift side.

Fig. 3. Shows the step behavior observed during TCAD analysis in the  $C_{GD}$  vs.  $V_D$  at high  $V_D$  as soon as the depletion region goes beyond the gate overlap length.

Fig. 4. Shows the schematic of depletion region extension in the drift region as the applied drain bias is increased.

explaining the charge contribution under the gate overlap length.

$$L_{\text{ov,new}} = LOVER - W_{\text{dep,dr}} \tag{8}$$

$$L_{\text{ov,new}} = LOVER \cdot (1 - LOVER1 \cdot \sqrt{V_{\text{D}} + V_{\text{bi,dr}}}) \quad (9)$$

The coefficient of the depletion width extension is defined by the model parameter LOVER1. After rearranging (8) and (9), the new gate overlap length, which is restricted to be a positive value, is given by (10). Parameter LOVER2 is introduced to make the model flexible enough to capture  $C_{GD}$  across varying LDMOS structures.

$$L_{\text{ov,new}} = LOVER \cdot (1 - (LOVER1 \cdot \sqrt{V_{\text{D}} + V_{\text{bi,dr}}} - LOVER2))$$

(10)

The modified gate-to-drain overlap charge that accurately captures the capacitance is given as:

$$Q_{\text{GDOVnew}} = W \cdot L_{\text{ov new}} \cdot C_{\text{ox}} \cdot V_{\text{f}} \cdot q_{\text{drift}}$$

(11)

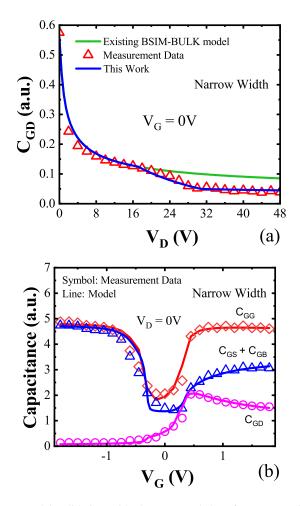

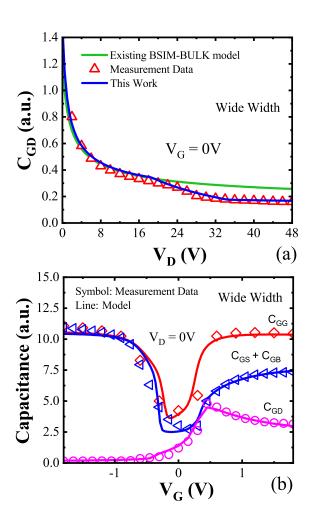

The developed model accurately captures the measurement characteristics of two different width devices as shown in Fig. 5 and Fig. 6

## Conclusions

We observed the step behavior in the capacitance of LD-MOS transistors when operated at very high drain voltages. TCAD analysis is performed to study the underlying physics. We then presented a physics-based compact model under the BSIM-BULK framework, accurately capturing the measurement results.

## ACKNOWLEDGMENT

We thank Infineon Technologies for providing us with the measured data. We also thank Science and Engineering Research Board (SERB), Department of Electrical Engineering and the Dean of Academic Affairs for supporting our work.

Fig. 5. Model validation with the measured data for narrow width device (a) shows  $C_{GD}$  vs normalized  $V_D$  in OFF state for both existing (green) and proposed model (blue) and, (b) shows all Capacitance vs  $V_G$  at  $V_D = 0V$ .

# REFERENCES

- [1] A. Wood, C. Dragon, and W. Burger, "High performance silicon ldmos technology for 2 ghz rf power amplifier applications," in *International Electron Devices Meeting. Technical Digest*, 1996, pp. 87–90.

- [2] Y. Chauhan, "Compact modeling of high voltage mosfets," Ph.D. dissertation, 07 2007.

- [3] V. Subramanian and F. Enablement, "High voltage mosfet technology, models, and applications." [Online]. Available: https://www.mos-ak.org/ india/presentations/VSubramanian\_MOS-AK\_India12.pdf

- [4] A. Sharma, Y. H. Zarkob, G. Pahwa, C. K. Dabhi, R. Goel, H. Agarwal, V. Kubrak, M. Tang, M. Treiber, C. Hu, and Y. S. Chauhan, "Compact modeling of impact ionization and conductivity modulation in Idmos transistors," *IEEE Transactions on Electron Devices*, pp. 1–7, 2024.

- [5] G. Pahwa, A. Sharma, R. Goel, G. Gill, H. Agarwal, Y. S. Chauhan, and C. Hu, "Robust compact model of high-voltage mosfet's drift region," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 42, no. 1, pp. 337–340, 2023.

- [6] H. Agarwal, C. Gupta, R. Goel, P. Kushwaha, Y.-K. Lin, M.-Y. Kao, J.-P. Duarte, H.-L. Chang, Y. S. Chauhan, S. Salahuddin, and C. Hu, "Bsim-hv: High-voltage mosfet model including quasi-saturation and self-heating effect," *IEEE Transactions on Electron Devices*, vol. 66, no. 10, pp. 4258–4263, 2019.

- [7] "International roadmap for devices and systems," 2023.

- [8] E. Griffith, S. Kelly, J. Power, D. Bain, S. Whiston, P. Elbert, and M. O'Neill, "Capacitance modelling of ldmos transistors," in 30th European Solid-State Device Research Conference, 2000, pp. 624–627.

Fig. 6. Model validation with the measured data for wide width device (a) shows  $C_{GD}$  vs normalized  $V_D$  in OFF state for both existing (green) and proposed model (blue) and, (b) shows all Capacitance vs  $V_G$  at  $V_D = 0V$ .

- [9] A. Sharma et al., "Bsim-bulk107.1.0." 2022.

- [10] A. Sharma, R. Goel, and Y. S. Chauhan, "Analysis and modeling of off-state capacitance in ldd mosfets," in 2023 7th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), 2023, pp. 1–3.

- [11] K. N. Kaushal and N. R. Mohapatra, "Unified theory of the capacitance behavior in Idmos devices," *IEEE Transactions on Electron Devices*, vol. 69, no. 1, pp. 39–44, 2022.

- [12] S. Frere, P. Moens, B. Desoete, W. D, and A. Walton, "An improved ldmos transistor model that accurately predicts capacitance for all bias conditions," in *Proceedings of the 2005 International Conference on Microelectronic Test Structures*, 2005. ICMTS 2005., 2005, pp. 75–79.

- [13] W. Yao, G. Gildenblat, C. C. McAndrew, and A. Cassagnes, "Sp-hv: A scalable surface-potential-based compact model for ldmos transistors," *IEEE Transactions on Electron Devices*, vol. 59, no. 3, pp. 542–550, 2012.

- [14] X. Jie, R. v. Langevelde, K. Xia, L. Chao, C. C. McAndrew, Q. Zhang, M. Bacchi, and W. Li, "Accurate gate charge modeling of hv ldmos transistors for power circuit applications," in 2023 35th International Conference on Microelectronic Test Structure (ICMTS), 2023, pp. 1–5.

- [15] H. J. Mattausch, M. Miyake, T. Iizuka, H. Kikuchihara, and M. Miura-Mattausch, "The second generation of hisim hv compact models for high voltage mosfets," *IEEE Transactions on Electron Devices*, vol. 60, no. 2, pp. 653–661, 2013.