# A Multiscale Simulation Approach for Program Noise and Cross-temperature Effects in 3D NANDs

Keng-Hua Lin Synopsys Taiwan Co., Ltd. Hsinchu Hsien, Taiwan kenghua@synopsys.com

Andrew R. Brown

Synopsys Northern Europe, Ltd

Glasgow, G3 8HB UK

andrew.brown@synopsys.com

Anders Blom Synopsys, Inc Sunnyvale, CA, USA andersb@synopsys.com Salvatore Maria Amoroso Synopsys Northern Europe, Ltd Glasgow, G3 8HB UK salvatore.amoroso@synopsys.com

Plamen Asenov Synopsys Northern Europe, Ltd Glasgow, G3 8HB UK plamen.asenov@synopsys.com

Victor Moroz Synopsys, Inc Sunnyvale, CA, USA victor.moroz@synopsys.com

Abstract—In this work, by means of a multiscale simulation approach, we study noise-related phenomena in 3D NANDs, which are ruled by the stochastic behavior of polysilicon grain boundary defects. Ab-initio simulation is, firstly, carried out to gain a physics-based understanding of the polysilicon bands and its traps properties. In particular, we have assessed the stability of our results against several configurations of most structurally diverse defects in amorphous silicon. The defect energies are then used to inform 3D TCAD to enable a Kinetic Monte Carlo simulation of the program noise and the evaluation of cross-temperature effects in the read operation.

Keywords—3D NAND, Memories, Ab-initio simulation, TCAD, Variability, Reliability.

# I. INTRODUCTION

NAND technology keeps reaching unprecedented levels of bit density, mainly thanks to 3D stacking – with most players delivering today more than 200 layers in a four-bit-per-cell technology [1,2]. With densities of billions of cells per chip, variability from both process variations [3] and intrinsic statistical variations [4-6] becomes a fundamental design concern. Moreover, the polysilicon channel material adopted in 3D NANDs adds new reliability aspects to the cross-temperature effect [7]. This issue appears when the NAND memory is read at a different temperature from that at which it was programmed. This was previously known in 2D NANDs, but 3D NANDs exacerbate this effect because the polysilicon trap occupancy (and the associated variability) is modulated by the temperature [8-9].

Numerical simulation is a powerful tool to investigate such phenomena. However, the variability response to temperature depends on the trap energy distributions in the polysilicon bandgap, which is typically approximated by empirical distributions and calibrated to hardware data [5]. In this paper, for the first time to the best of our knowledge, we obtain a deeper physics-based understanding of polysilicon grain boundaries and its defects by *ab-initio* simulations. We then use *ab-initio*-calculated trap properties to inform 3D TCAD, showcasing an example of multiscale approach to the statistical simulation of 3D NAND cells.

Po-Chou Chen Synopsys Taiwan Co., Ltd. Hsinchu Hsien, Taiwan pochou@synopsys.com

U. G. Vej-Hansen Synopsys Denmark Aps Fruebjergvej 3, DK-2100 Copenhagen, Denmark ulrik.vej-hansen@synopsys.com

Chih-Chiang Wang Synopsys Taiwan Co., Ltd. Hsinchu Hsien, Taiwan ccwang@synopsys.com Yueh-Ying Tseng Synopsys Taiwan Co., Ltd. Hsinchu Hsien, Taiwan yytseng@synopsys.com

Xi-Wei Lin Synopsys, Inc Sunnyvale, CA, USA xiwei@synopsys.com

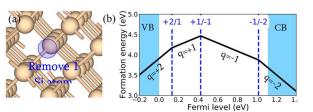

Figure 1: (a) Defect by removing one Si atom in c-Si. (b) *Ab-initio*-calculated defect formation energies at different charge states and (c) trap energy levels in c-Si with different simulation supercell sizes vs. different experimental results [19, 22-23].

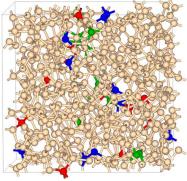

Figure 2: Amorphous Si with the 10 (red atoms), 20 (red and blue atoms), and 30 (red, blue and green atoms) most structurally diverse sites to generate defects.

### II. AB-INITIO SIMULATION

We calculate the trap energy levels in amorphous Si (a-Si) from *ab-initio* simulations since the atomic structures at grain boundaries (GBs) of the polysilicon channel are like a-Si with defects. Before that, we validate the computational settings against the experimental trap energy levels in c-Si with lattice defects. The key defect in a-Si that produces a midgap state is the threefold-coordinated Si atom with sp³ dangling bond [10], and therefore, we remove one Si atom from both the fully coordinated c-Si and a-Si to generate the dangling bonds and investigate the resulted trap energy levels with atomistic software, QuantumATK [11].

In this work, the *ab-initio* defect geometry optimization and total energy calculations are conducted with HSE06 hybrid functional with the Fock exchange fraction,  $\alpha = 0.23$ , to make the bandgap of c-Si equal to 1.12 eV. The k-point densities are 4 Å along a-, b-, and c-axis for c-Si and only  $\Gamma$  point is used for a-Si. During the geometry optimization, both the lattice vectors and the atomic positions are relaxed until the atomic forces are smaller than 0.01 eV/Å. After that, the formation energy of the defect at a given charge state  $E_f^{X,q}$  is calculated as [12]:

$$E_f^{X,q} = E_{tot}^{X,q} - E_{bulk} - \sum_i n_i \mu_i + q(E_V + E_F) + E_{corr}$$

where  $E_{tot}^{X,q}$  and  $E_{bulk}$  are the total energies of defect and the pristine bulk, respectively; q is the charge;  $\mu_i$  is the chemical potential of each element i;  $E_F$  is the Fermi level referencing to valence band edge,  $E_V$ ;  $E_{corr}$  includes the short range potential energy correction term,  $q \cdot \delta_{q/b}$ , and the long range energy correction term,  $E_{lat}^q$ .

Fig. 1 shows the defect structure in c-Si, *ab-initio*-calculated defect formation energies at different charge states, and the resulted trap energy levels with respect to different simulation supercell sizes. Even though we apply the energy correction terms to remove the spurious defect-defect interaction across the periodic boundaries, we still require a supercell containing at least 512 atoms to obtain the trap energy levels comparable to the experimental results [10, 13-14].

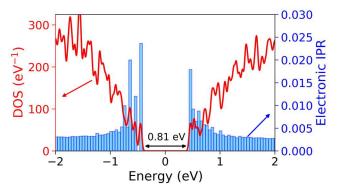

Figure 3: Density of states (red line referring to the left y-axis) and electronic inverse participation ratio (blue bar referring to the right y-axis) of a-Si.

Next, we investigate the trap energy levels in a-Si containing 512 atoms as shown in Fig. 2. The a-Si is generated with molecular dynamics Tersoff forcefield [15-16] by melting the structure at 2500 K for 10 ps and then quenching it to 500 K with the quench rate of -1E11 K/s under NVT Nose

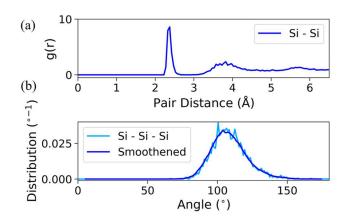

Figure 4: (a) Radial distribution function and (b) angular distribution function of the generated a-Si.

Figure 5: Four under-coordinated Si atoms after removing one Si atom in the a-Si. The green isosurfaces correspond to the electron densities of the dangling bonds.

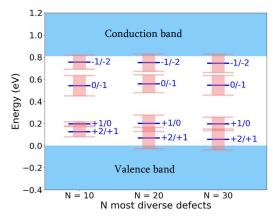

Figure 6: Average trap energy levels (blue lines) and their energy distributions (pink bars) of the 10, 20, and 30 most structurally diverse defects in the a-Si.

Hoover ensemble. Then the structure is further relaxed with *ab-initio* HSE06 hybrid functional until the atomic forces are smaller than 0.01 eV/Å. The bandgap of the generated a-Si is 0.81 eV, as shown from the density of states (DOS) in Fig. 3, and the conduction/valence band edge states possess higher electronic inverse participation ratio, indicating their localized nature. In addition, we confirm the amorphous nature of the generated a-Si from its radial distribution function in Fig. 4(a) and observe the strain defects from the large deviation in the bond angle in Fig. 4(b). These strain defects are associated with the localized conduction/valence band edge states in Fig. 3. To consider the effects of local structural/chemical variation

in a-Si, we calculate the trap energy levels by removing one Si atom at a time from the 10, 20, and 30 most structurally diverse Si sites, as indicated in Fig. 2, in a-Si. The resulted defects after geometry optimization are usually the undercoordinated Si atoms with dangling bonds, as shown in Fig. 5. The average trap energy levels converge when the defect sample number, N, exceeds 20 in Fig.6, and the acceptor traps with charge transitions -1/-2 and 0/-1 are  $0.06 \pm 0.08$  eV and  $0.25 \pm 0.08$  eV below the conduction band edge, respectively.

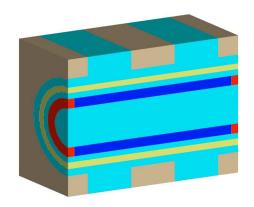

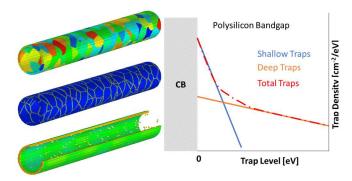

### III. 3D STATISTICAL TCAD

To correctly capture the fringing effects in the intercell regions, we focus on a single NAND cell including one half neighbor cell per side (Fig. 7, Vpass=6V). The Macaroni structure [17] dimensions are listed in the table. Sentaurus Process [18] and Sentaurus Device [19] are employed for processing the typical cell structure and Garand VE [20] for studying the statistical behavior of the cell. The stochastic nature of polycrystalline silicon is accounted for by means of random grains having average size Dg = 30 nm and with traps located at their GBs (Fig.8). For the initial effort presented in this work, we are still using a double exponential distribution [21-23], but the average parameters are adjusted according to

| L        | 35 nm | $r_f$     | 20 nm |

|----------|-------|-----------|-------|

| $t_{ch}$ | 10 nm | $t_{box}$ | 6 nm  |

| $t_n$    | 6 nm  | $t_{tox}$ | 8 nm  |

Figure 7: Cross-section schematic of the Macaroni device structure (red = highly doped silicon; blue = polysilicon, cyan = oxide, yellow = nitride, brown = WLs).

Figure 8: Example of polysilicon channel grain structure and traps generated with Garand VE and approximated double-exponential energy distribution of polysilicon defects

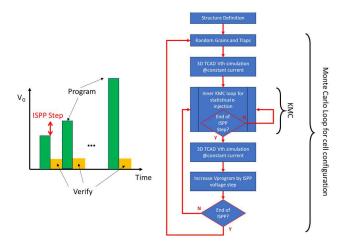

Figure 9: 3D TCAD statistical simulation for the NAND ISPP algorithm.

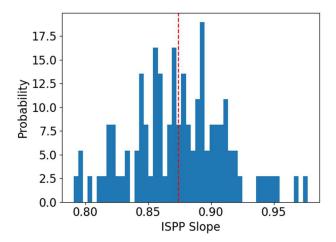

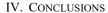

the *ab-initio* simulation (shallow traps at 60meV, deep traps 250meV, accordingly to the results with the 20 most structurally diverse defects in a-Si). The natural extension of this work will be to make full use of the properties extracted from ab-initio into TCAD. The rest of the structural parameters are as in [24]. Here, to simulate the Incremental Step Pulse Programming (ISPP) algorithm we have implemented a stochastic Kinetic Monte Carlo engine (Fig.9), following [25]. We first performed the stochastic ISPP simulation at a temperature of 348K on 100 statistical device instances, with an ISPP staircase from 16.2V to 22.6V (step 400mV, pulse width 15µs). Fig.10 shows the stochastic dispersion of the ISPP slope: as commonly reported in chargetrapping memories, the average slope is < 1.0, here  $\sim 0.875$ . The ISPP slope variability is due to variability of nitride traps and variability of charge injection (i.e. variability in tunnelling field, in supply function in the channel and the single electron statistics). Given this slope, the average  $\Delta VT$  between two consecutive ISPP steps is expected to be on average ISPP slope×ISPP step (here 0.875×0.4V=0.35V), as indeed shown in Fig.11. It is worth noting that the ISPP slope range of variation is between 0.75 and 1.0, whilst the variability of the  $\Delta VT$  between two consecutive steps goes beyond  $1.0 \times \text{Vstep}(=0.4 \text{V})$  and below  $0.75 \times \text{Vstep}(=0.3 \text{V})$ , mainly because of the extra variability contribution coming from the discrete polysilicon traps in the channels, whose occupancy is not constants between two ISPP steps.

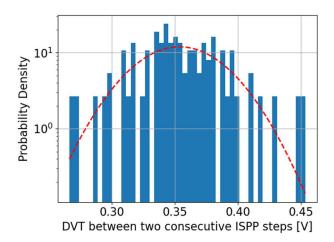

Fig.12 shows the cross-temperature simulation results: here we have performed the ISPP Program/Verify at T=348K (x-axis) then read again the array at T=248K (y-axis). A program level placement of 4.6V is arbitrarily chosen as the target. We observe that the accuracy on the x-axis is ~0.4V (i.e. as accurate as the ISPP step), however the read operation at a different temperature will introduce 1) an average shift in the y-axis and 2) a worsening in the variability (~500mV). This is mainly due to polysilicon trap occupancy being different at different temperatures. This highlights that a calibration of the polysilicon trap densities can only give a partial understanding of variability/reliability phenomena in 3D NANDs and that gaining knowledge of the trap energy distributions is fundamental to describe temperaturemodulated effects. For this we seek a multi-physics approach down to atomistic scale.

Figure 10: ISPP slope statistical distribution from 3D TCAD simulation

In this paper we have showcased a multiscale simulation approach to study the statistical variability in modern NAND memories. The defect formation energies and trap energy levels of polysilicon grain boundary are derived from *ab-initio* simulation, by adopting an amorphous silicon system with 512 atom for reliable results. We have also showed robustness of results against variation in the number of the most structurally diverse defects in amorphous silicon. These trap energy levels are then used to inform 3D TCAD Kinetic Monte Carlo simulation, which enables the study of the program noise and the evaluation of cross-temperature noise in the read operation.

Figure 11: Statistical distribution of the  $\Delta VT$  between two consecutive ISPP steps.

Figure 12: Cross-temperature effect simulated with an ISPP target level of 4.6V @348K and a read again operation @248K.

## REFERENCES

- [1] M. Kim et al., ISSCC Dig. Tech. Papers, 2022, pp.136-137;

- [2] T. Pekny et al., ISSCC Dig. Tech. Papers, 2022, pp.132-133;

- [3] D. Lee and C. Shin, Micromachines, vol. 13, p.1139, 2022;

- [4] K. Nam et al., IEEE TED, vol. 69, pp. 3681-3687, 2022;

- [5] G. Nicosia et al., IEEE TED, vol. 65, pp.3207-3213, 2018;

- [6] D. Verreck et al., IEDM Tech. Dig., 2019, pp.755-758;

- [7] K. Cho, et al., Adv. Intell. Syst., 5: 2300400, 2023;

- [8] C. Zambelli et al., IEEE IIRW 2018;

- [9] Y. Guo et al., IEEE EDTM 2023;

- [10] D. A. Drabold and T. A. Abtew, Theory of Defects in Semiconductors, pp. 245-268, Springer, Berlin, Heidelberg;

- [11] S. Smidstrup et al., J. Phys.: Condens. Matter, vol. 32, pp.015901, 2020;

- [12] QuantumATK V-2023.12 Documentation: Charged Point Defects;

- [13] M. L. Ciurea et al., Romanian Reports in Physics, vol. 60, No. 3, pp. 735-748, 2008;

- [14] M. J. Puska, J. Phys: Condens. Matter, vol. 1, pp. 7347-7366, 1989;

- [15] J. Tersoff, Phys. Rev. B, vol. 38, pp. 9902-9905, 1988;

- [16] J. Tersoff, Phys. Rev. B, vol. 37, pp. 6991, 1988

- [17] Y. Fukuzumi et al., IEDM Tech. Dig., 2007, pp.449-452;

- [18] Sentaurus Process User Guide V-2024.03, Synopsys

- [19] Sentaurus Device User Guide V-2024.03, Synopsys

- [20] Garand VE User Guide supplement for 3D-NAND V-2024.03, Synopsys

- [21] M. D. Jacunski et al., IEEE TED, vol. 43, pp.1433-1440, 1996;

- [22] M. Valdinoci et al., Solid State Electronics 41, pp.1363-1369, 1997:

- [23] J. Werner and M. Peisl, Phys. Rev B 31, 6881-6883, 1985;

- [24] S. M. Amoroso et al., IEEE SISPAD 2023;

- [25] S. M. Amoroso et al. IEEE IEDM Tech Dig. 2010.