# Superconducting route to quantum computing

1st Eisuke Abe

RIKEN Center for Quantum Computing Wako, Saitama 351-0198, Japan eisuke.abe@riken.jp, https://orcid.org/0000-0001-7993-3660

Abstract—The basics of the hardware for superconducting quantum computing are described.

Index Terms—quantum computing, superconducting qubit, circuit quantum electrodynamics, CMOS technology

# I. INTRODUCTION

Once thought nightmare [1], quantum computers are now being developed under various physical platforms of both natural (photons, ions, ultracold atoms, and Rydberg atoms) and artificial (semiconductor and superconducting devices) systems. Quantum bits (qubits) realized there by a variety of encoding schemes are not just 0 or 1 but can take a quantum mechanical superposition of 0 and 1 as well as an entangled state with multiple gubits. With each physical system having its pros and cons, we still do not know how quantum computers will look like twenty or thirty years later. But at this moment, one of the leading platforms is the system based on superconducting quantum circuits. The 53qubit Sycamore processor from Google demonstrated quantum supremacy in the sampling of random quantum circuits, which the state-of-the-art classical counterpart would require 10,000 years to solve [2]. Even though the problem setting itself will not have practical applications and the claim is debatable [3], it has certainly intensified worldwide efforts to further unlock the potential of quantum computers, leading to more recent demonstrations using the large(er) number of superconducting qubits such as error suppression of a single logical qubit encoded using 49 physical qubits (including auxiliary qubits) [4], generation of a 51-qubit cluster state [5], and simulation of the magnetization of a spin system using 127 qubits and post-processing [6].

A salient feature of superconducting quantum circuits that has attracted quantum hardware developers is that one can engineer, or even create, the properties of qubits by a judicious design of the circuit parameters. Essentially, the individual hardware developers, whether in academic or in industry, have their own favorite superconducting qubits. It is not the intent of this talk to cover such a wide range of qubit architectures. Here, the author takes the system developed at RIKEN (national research institute in Japan) as a concrete example and describes how it works. It should be noted, however, that even in this example the qubit design, fabrication process, and control electronics have undergone continuous updates.

This work was supported by MEXT Q-LEAP (No. JPMXS0118068682).

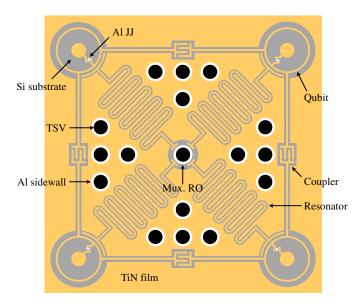

Fig. 1. Schematic layout of a quantum processor consisting of four qubits at the corners and a multiplexed readout (Mux. RO) structure at the center. JJ: Josephson junction. TSV: through-silicon via.

#### II. HARDWARE-CHIP, WIRING, AND ELECTRONICS

Figure 1 shows a schematic layout of four superconducting qubits integrated with multiplexed readout. The circularshaped qubits, or concentric transmons, are located at the four corners (a transmon is a type of superconducting qubit designed to be immune to the charge fluctuations). The neighboring qubits are coupled via the arms that run the side and meet at the middle to form an interdigit capacitor. The inner and outer circles of the qubit are shunted by the Josephson junction, two layers of superconductors interrupted by a thin insulating layer, which from the viewpoint of circuit design acts as a nonlinear and dissipationless inductor. The nonlinearity is an essential ingredient of a superconducting qubit. A linear LC circuit, when quantized, is a harmonic oscillator with the energy levels equally spaced by  $\omega_{i,i+1} \equiv$  $\omega_{i+1} - \omega_i = 1/\sqrt{\text{LC}}$  (*i* = 0, 1, 2, ...). Such harmonic oscillator states are indeed formed in the readout resonators, the meander lines capacitively coupled to the qubits. The equally spaced levels mean that the drive frequency tuned to  $\omega_{01}$  is likewise on resonance with other transitions  $\omega_{i,i+1}$ , precluding the distinction of the qubit subspace from higher levels. The cosine potential that the Josephson junction provides makes  $\omega_{01}$  larger than the others, allowing us to define the ground

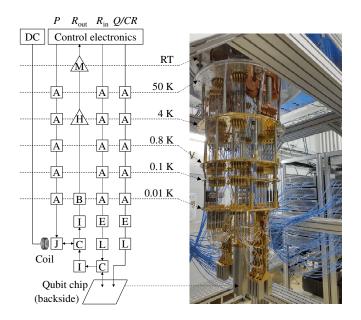

Fig. 2. (Left) Schematic of control and measurement chains from control electronics at room temperature (RT) to the qubit chip at 10 mK. *Q*: qubit control. *CR*: cross-resonance.  $R_{in}$ : readout (input).  $R_{out}$ : readout (output). *P*: pump for Josephson parametric amplifier (JPA, J). A: attenuator. E: eccosorb infrared filter. L: low-pass filter. C: circulator. I: isolator. B: band-pass filter. H: HEMT cryogenic amplifier. M: microwave amplifier. JPAs are flux-biased by passing currents to coils placed nearby. (Right) Photo of a dilution refrigerator and control electronics. A 64-qubit chip is installed inside of the magnetic shield (the silver cylinder at the bottom).

state as qubit  $|0\rangle$  and the first excited state as qubit  $|1\rangle$ . The parameter  $\alpha$  defined as  $\omega_{12} - \omega_{01}$  characterizes the degree of nonlinearity of a qubit. In reality, the higher levels are still not negligible. The excitation to them, called leakage, is a significant source of quantum logic errors in superconducting quantum processors.

The abilities to perform single- and two-qubit gates and a readout of the qubit state are mandatory to any quantum processors. In the design of Fig. 1, all these are realized by applying microwave pulses. To this end, coaxial cables are in contact with the backside of the chip via pogo pins, aligned perpendicular to it; see the schematic of Fig. 2. Each qubit has its own control wiring right behind the inner circle, and the four readout resonators are joined together at the central port, to which the readout microwave pulses are applied. A singlequbit gate is a properly timed microwave pulse on resonance with the given qubit, driving the qubit onto anywhere in the Bloch sphere, or an arbitrary superposition of  $|0\rangle$  and  $|1\rangle$ including the relative phase.

The readout scheme is based on the concept of circuit quantum electrodynamics [7]. The readout resonator is detuned from the qubit and couples to it dispersively such that the resonance frequency is dependent on the qubit state. The signal reflected from the resonator then carries the information of the qubit state in its frequency and phase. This dispersive readout is one realization of quantum nondemolition measurements required for quantum error correction. But the Purcell effect can still induce the qubit dephasing, and on-chip filters (Purcell filters) are often used concomitantly [8].

There are various ways to perform two-qubit gates. The cross-resonance (CR) gate [9] adopted in the present design is advantageous in avoiding the introduction of additional RF or DC wiring to the chip. The same wiring that is used for the single-qubit gate can be used. When the neighboring two qubits, say Q1 and Q2, have different frequencies  $\omega_{q1}$  and  $\omega_{q2}$ , applying  $\omega_{q2}$  on Q1 does nothing (ideally) to Q1.  $\omega_{q2}$  can drive Q2 via the coupler, but the way it does is dependent on the state of Q1. One can thus realize a conditional gate between two nearest-neighbor qubits.

The qubit layout in Fig. 1 constitutes a unit cell extendible to a larger lattice of qubits by simply repeating it twodimensionally. The side length of the unit cell is about a quarter of a centimeter and that the wiring comes out of plane. Therefore, there is enough room for introducing a coaxial cable even to a qubit in the middle of a large lattice. In-plane wiring if used would have to employ air-bridges overarching multiple microwave lines, possibly increasing the crosstalk among them.

The qubit chip consists of multiple layers of materials. The substrate is a high-resistivity silicon (Si) wafer with the thickness of 300  $\mu$ m. Titanium nitride (TiN) films, which are superconductors resistant to oxidation and have large kinetic inductance [10], are deposited with the thickness of 100 nm on both sides of the wafer. Through-silicon vias (TSVs) are formed by the Bosch process and the sidewalls are covered with aluminum (Al). Al-covered TSVs electrically connect the front and back sides of the chip, effective in suppressing spurious electromagnetic modes such as the chip mode (the rectangular cavity mode arising from the size of the chip) and the slotline mode (the mode between unconnected ground planes) which otherwise can damage the qubit coherence. Josephson junctions made of Al and AlO<sub>x</sub> have 200 nm  $\times$ 200 nm in area. The RIKEN team now routinely fabricates chips containing 64 qubits of an  $8 \times 8$  lattice.

The fabricated circuits do not have any functionalities to tune the qubit frequencies *in situ*, whereas to perform accurate (high-fidelity) CR gates the qubit frequencies must be properly assigned within the lattice (in an extreme case, if nearestneighbor qubits share the same frequencies the CR pulse will drive the both qubits). However, the inevitable process inhomogeneity calls for methods to adjust the qubit frequencies after fabrication. One promising approach is laser annealing [11]–[13]. Illumination of laser focused onto a junction area increases its resistance, enabling independent trimming of the qubit frequencies.

The chip is mounted inside of a dilution refrigerator and is cooled down to 10 mK. While the superconducting transition temperature  $T_c$  of bulk Al is 1.14 K, the chip must be at temperatures well below  $T_c$ . The qubit frequencies typically fall on the 2-to-10 GHz range, chosen largely in light of the availability of high-frequency electronics. For instance, in one of our designs, the qubit (resonator) frequencies are set between 7.7–8.9 (10.1–10.4) GHz, with  $\alpha = -400$  MHz (negative due to the softening potential). 10 GHz corresponds to 0.48 K in temperature, and the thermal excitation to the higher levels must be suppressed. The suppression is not sufficient just by cooling the chip, because the signals come from room temperature (RT). The incoming signals are progressively attenuated and thermalized at multiple temperature stages (A in Fig. 2). For instance, a typical microwave power for readout is at the single photon level of -130 dBm. The noises outside of the operational frequency range are rejected by low-pass (L) and band-pass (B) filters. The eccosorb filters (E), which absorb photons in the infrared regime, are also employed. Such photons exist as stray light or black body radiation from the higher temperature stages and, with energies larger than  $2\Delta \approx 2 \times 1.76 k_{\rm B} T_{\rm c}$ , can break Cooper pairs. The broken Cooper pairs, or quasiparticles, wandering about inside a superconductor are harmful, as they exchange energies with qubits or cause parity switching by tunneling across the junction barrier [14].

The readout microwave pulse  $(R_{in})$  reflected at the chip is sent back to the electronics  $(R_{out})$  directed by circulators (C). Not to mention, the single-photon-level signal would die out without amplification. Quantum-limited amplifiers are desired as the first-stage amplification. Impedance-matched parametric amplifiers (IMPAs) [15], a type of Josephson parametric amplifiers (JPAs), are installed in the photo of Fig. 2 (inside of the rectangular, silver magnetic shields at the bottom). They are pumped parametrically at twice the readout frequencies (*P*). Other types of JPAs, such as Josephson traveling wave parametric amplifier (JTWPA), can also be used, and some are commercialized [16]. Additional amplifications are carried out at the 4-K stage by a high electron mobility transistor (HEMT, H) cryogenic amplifier followed by a low-noise microwave amplifier (M) at RT.

To estimate the number of coaxial cables needed to fully operate an *N*-qubit device, we count *N* for *Q/CR*, *N*/4 for  $R_{\rm in}$ ,  $R_{\rm out}$ , and *P*, thus  $1.75 \times N$  in total. For the 64-qubit setup in Fig. 2, this amounts to 112 coaxial cables, connected all the way from FPGA-based digital control electronics at RT to the 10-mK stage.

### III. REMARKS

Here, a few remarks that may be of interest to those in the semiconductor industry are made.

From manufacturing standard, the superconducting quantum circuits described above are fairly large. Why? One reason is that the  $\lambda/2$  coplanar waveguide resonators have dimensions largely dictated by the wavelength and the materials dielectric constant. Furthermore, to design a transmon, a small charging energy, or equivalently a large total capacitance, is required. In Fig. 1, the outer diameter of the concentric transmon is about 600  $\mu$ m. The use of an interdigit capacitor for instance should decrease the size of a transmon compared with a parallel planar capacitor. This is certainly true and in some part has been employed, but shrinking the size this way turns out to affect the coherence. This was not so obvious in early studies, but the community now understands that defects omnipresent at the metal–air and metal–substrate interfaces, or inside of the

junction that is typically amorphous, can act as microscopic two-level systems and absorb single-photon microwaves. This leads to the energy (dielectric) loss in the circuit, i.e., the relaxation of a qubit  $(T_1)$ . A miniaturized device concentrates the microwave intensity in a small region and is prone to the energy loss. Making a device larger dilutes the distribution of microwave across the device and extends  $T_1$  [17]. For this reason, over the years, transmons have become bigger and bigger. This, however, is not the end of the story. Recent studies have uncovered that when the dimension of a transmon matches with the wavelength of above-100-GHz photons, the transmon itself acts as a dipole antenna to absorb the resonant photons [14], [18]. This is somewhat similar to the chip mode mentioned earlier, but this time the relevant photons have the energies larger than  $2\Delta$  and generate quasiparticles.

In the face of such a size effect, it is worthwhile to revert to shrinking the size of transmons again, while of course preserving the coherence. Not to mention, a smaller footprint is advantageous for further integration of qubits. In a mergedelement transmon (MET), the Josephson junction is designed to serve as both a nonlinear inductor and a parallel shunt capacitor [19], [20]. This requires a micron-sized junction, but the overall footprint can be reduced. While the large junction indicates more defects in the amorphous barrier layer, but they can be traded by a reduced participation of the metal-air and metal-substrate interfaces. The coherence times comparable to standard transmons have been reported [20]. A FinMET is another emerging idea that combines the concepts of MET and FinFET, and complements the need of reducing defects in a large junction of MET [21]. An anisotropic etch of the Si substrate creates a thin wall of Si (fin). By depositing Al films on both sides, the Al/Si/Ai structure works as a tunnel barrier with reduced dielectric loss of crystalline Si. It is further hoped that this approach will be compatible with the industry-scale CMOS process.

In semiconductor qubits, it is a logical step toward largescale quantum processors to leverage the state-of-the-art CMOS fabrication facilities, as the fabrication processes are quite similar [22]. However, the fabrication of transmons is not necessarily compatible with the CMOS process. For instance, the double-angle Al evaporation is a key process to produce high-quality junctions without breaking a vacuum in between the depositions of two Al layers. On the other hand, overlap junctions, which require separate lithography steps for the two layers, are compatible with the CMOS process, but tend to have lower-quality junctions. Importantly, a recent report has shown that the manufacturing process using overlap junctions can produce high-quality transmons [23].

Lastly, a straightforward application of CMOS technology will be the use of cryogenic CMOS for the control of superconducting qubits to minimize the heat load from RT [24]. Cryogenic multiplexer will further reduce the number of required wiring [25]. Alternative ideas are to use singleflux quantum (SFQ) circuits [26], [27] or photonic links [28]. Such continuous technology development will bring largescale, fault-tolerant quantum computers closer to the reality.

## ACKNOWLEDGMENT

The author expresses his sincere thanks to the members of Superconducting Quantum Electronics Research Team, Superconducting Quantum Electronics Joint Research Unit, Superconducting Quantum Computing System Research Unit, and RIKEN RQC-FUJITSU Collaboration Center within RIKEN Center for Quantum Computing, as well as the collaborators inside and outside of RIKEN, for their contributions to the development of RIKEN's superconducting quantum computers.

#### REFERENCES

- S. Haroche and J.-M. Raimond, "Quantum Computing: Dream or Nightmare," Phys. Today, vol. 49, pp. 51-52, August 1996.

- [2] F. Arute, K. Arya, R. Babbush, D. Bacon, J. C. Bardin, R. Barends, R. Biswas, S. Boixo, F. G. S. L. Brandao, D. A. Buell, B. Burkett, Y. Chen, Z. Chen, B. Chiaro, R. Collins, W. Courtney, A. Dunsworth, E. Farhi, B. Foxen, A. Fowler, C. Gidney, M. Giustina, R. Graff, K. Guerin, S. Habegger, M. P. Harrigan, M. J. Hartmann, A. Ho, M. Hoffmann, T. Huang, T. S. Humble, S. V. Isakov, E. Jeffrey, Z. Jiang, D. Kafri, K. Kechedzhi, J. Kelly, P. V. Klimov, S. Knysh, A. Korotkov, F. Kostritsa, D. Landhuis, M. Lindmark, E. Lucero, D. Lyakh, S. Mandrà, J. R. McClean, M. McEwen, A. Megrant, X. Mi, K. Michielsen, M. Mohseni, J. Mutus, O. Naaman, M. Neeley, C. Neill, M. Y. Niu, E. Ostby, A. Petukhov, J. C. Platt, C. Quintana, E. G. Rieffel, P. Roushan, N. C. Rubin, D. Sank, K. J. Satzinger, V. Smelyanskiy, K. J. Sung, M. D. Trevithick, A. Vainsencher, B. Villalonga, T. White, Z. J. Yao, P. Yeh, A. Zalcman, H. Neven, and J. M. Martinis, "Quantum supremacy using a programmable superconducting processor," Nat., vol. 574, pp. 505–510, October 2019.

- [3] F. Pan, K. Chen, and P. Zhang, "Solving the Sampling Problem of the Sycamore Quantum Circuits," Phys. Rev. Lett., vol. 129, 090502, August 2022.

- [4] Google Quantum AI, "Suppressing quantum errors by scaling a surface code logical qubit," Nat., vol. 614, pp. 676–681, February 2023.

- [5] S. Cao, B. Wu, F. Chen, M. Gong, Y. Wu, Y. Ye, C. Zha, H. Qian, C. Ying, S. Guo, Q. Zhu, H.-L. Huang, Y. Zhao, S. Li, S. Wang, J. Yu, D. Fan, D. Wu, H. Su, H. Deng, H. Rong, Y. Li, K. Zhang, T.-H. Chung, F. Liang, J. Lin, Y. Xu, L. Su, C. Guo, N. Li, Y.-H. Huo, C.-Z. Peng, C.-Y. Lu, X. Yuan, X. Zhu, and J.-W. Pan, "Generation of genuine entanglement up to 51 superconducting qubits," Nat., vol. 619, pp. 738–742, July 2023.

- [6] Y. Kim, A. Eddins, S. Anand, K. X. Wei, E. van den Berg, S. Rosenblatt, H. Nayfeh, Y. Wu, M. Zaletel, K. Temme, and A. Kandala, "Evidence for the utility of quantum computing before fault tolerance," Nat., vol. 618, pp. 500–505, June 2023.

- [7] A. Blais, A. L. Grimsmo, S. M. Girvin, and A. Wallraff, "Circuit quantum electrodynamics," Rev. Mod. Phys., vol. 93, 025005, May 2021.

- [8] E. Jeffrey, D. Sank, J. Y. Mutus, T. C. White, J. Kelly, R. Barends, Y. Chen, Z. Chen, B. Chiaro, A. Dunsworth, A. Megrant, P. J. J. O'Malley, C. Neill, P. Roushan, A. Vainsencher, J. Wenner, A. N. Cleland, and John M. Martinis, "Fast Accurate State Measurement with Superconducting Qubits," Phys. Rev. Lett., vol. 112, 190504, May 2014.

- [9] C. Rigetti and M. Devoret, "Fully microwave-tunable universal gates in superconducting qubits with linear couplings and fixed transition frequencies," Phys. Rev. B, vol. 81, 134507, April 2010.

- [10] A. Shearrow, G. Koolstra, S. J. Whiteley, N. Earnest, P. S. Barry, F. J. Heremans, D. D. Awschalom, E. Shirokoff, D. I. Schuster, "Atomic layer deposition of titanium nitride for quantum circuits," Appl. Phys. Lett., vol. 113, 212601, November 2018.

- [11] J. B. Hertzberg, E. J. Zhang, S. Rosenblatt, E. Magesan, J. A. Smolin, J.-B. Yau, V. P. Adiga, M. Sandberg, M. Brink, J. M. Chow, and J. S. Orcutt, "Laser-annealing Josephson junctions for yielding scaled-up superconducting quantum processors," npj Quantum Inf., vol. 7, 129, August 2021.

- [12] E. J. Zhang, S. Srinivasan, N. Sundaresan, D. F. Bogorin, Y. Martin, J. B. Hertzberg, J. Timmerwilke, E. J. Pritchett, J.-B. Yau, C. Wang, W. Landers, E. P. Lewandowski, A. Narasgond, S. Rosenblatt, G. A. Keefe, I. Lauer, M. B. Rothwell, D. T. McClure, O. E. Dial, J. S. Orcutt, M. Brink, J. M. Chow, "High-performance superconducting quantum processors via laser annealing of transmon qubits," Sci. Adv., vol. 8, eabi6690, May 2022.

- [13] H. Kim, C. Jünger, A. Morvan, E. S. Barnard, W. P. Livingston, M. V. P. Altoé, Y. Kim, C. Song, L. Chen, J. M. Kreikebaum, D. F. Ogletree, D. I. Santiago, and I. Siddiqi, "Effects of laser-annealing on fixed-frequency superconducting qubits," Appl. Phys. Lett., vol. 121, 142601, October 2022.

- [14] J. Aumentado, G. Catelani, K. Serniak, "Quasiparticle poisoning in superconducting quantum computers," Phys. Today, vol. 76, pp. 34–39, August 2023.

- [15] J. Y. Mutus, T. C. White, R. Barends, Y. Chen, Z. Chen, B. Chiaro, A. Dunsworth, E. Jeffrey, J. Kelly, A. Megrant, C. Neill, P. J. J. O'Malley, P. Roushan, D. Sank, A. Vainsencher, J. Wenner, K. M. Sundqvist, A. N. Cleland, and J. M. Martinis, "Strong environmental coupling in a Josephson parametric amplifier," Appl. Phys. Lett., vol. 104, 263513, July 2014.

- [16] C. Macklin, K. O'Brien, D. Hover, M. E. Schwartz, V. Bolkhovsky, X. Zhang, W. D. Oliver, I. Siddiqi, "A near-quantum-limited Josephson traveling-wave parametric amplifier," Science, vol. 350, pp. 307–310, October 2015.

- [17] C. E. Murray, "Material matters in superconducting qubits," Mater. Sci. Eng. R, vol. 146, 100646, October 2021.

- [18] C.-H. Liu, D. C. Harrison, S. Patel, C. D. Wilen, O. Rafferty, A. Shearrow, A. Ballard, V. Iaia, J. Ku, B. L.T. Plourde, R. McDermott, "Quasiparticle Poisoning of Superconducting Qubits from Resonant Absorption of Pair-breaking Photons," arXiv:2203.06577, March 2022.

- [19] R. Zhao, S. Park, T. Zhao, M. Bal, C. R. H. McRae, J. Long, and D.P. Pappas, "Merged-Element Transmon," Phys. Rev, Appl., vol. 14, 064006, December 2020.

- [20] H. J. Mamin, E. Huang, S. Carnevale, C. T. Rettner, N. Arellano, M. H. Sherwood, C. Kurter, B. Trimm, M. Sandberg, R. M. Shelby, M. A. Mueed, B. A. Madon, A. Pushp, M. Steffen, and D. Rugar, "Merged-Element Transmons: Design and Qubit Performance," Phys. Rev, Appl., vol. 16, 024023, August 2021.

- [21] A. Goswami, A. P. McFadden, T. Zhao, H. Inbar, J. T. Dong, R. Zhao C. R. H. McRae, R. W. Simmonds, C. J. Palmstrøm, and D. P. Pappas, "Towards merged-element transmons using silicon fins: The FinMET," Appl. Phys. Lett., vol. 121, 064001, August 2022.

- [22] A. M. J. Zwerver, T. Krähenmann, T. F. Watson, L. Lampert, H. C. George, R. Pillarisetty, S. A. Bojarski, P. Amin, S. V. Amitonov, J. M. Boter, R. Caudillo, D. Corras-Serrano, J. P. Dehollain, G. Droulers, E. M. Henry, R. Kotlyar, M. Lodari, F. Lüthi, D. J. Michalak, B. K. Mueller, S. Neyens, J. Roberts, N. Samkharadze, G. Zheng, O. K. Zietz, G. Scappucci, M. Veldhorst, L. M. K. Vandersypen, and J. S. Clarke, "Qubits made by advanced semiconductor manufacturing," Nat. Electron., vol. 5, pp. 184–190, March 2022.

- [23] J. Verjauw, R. Acharya, J. Van Damme, Ts. Ivanov, D. P. Lozano, F. A. Mohiyaddin, D. Wan, J. Jussot, A. M. Vadiraj, M. Mongillo, M. Heyns, I. Radu, B. Govoreanu, and A. Potočnik, "Path toward manufacturable superconducting qubits with relaxation times exceeding 0.1 ms," npj Quantum Inf., vol. 8, 93, August 2022.

- [24] K. Kang, D. Minn, S. Bae, J. Lee, S. Kang, M. Lee, H.-J. Song, and J.-Y. Sim, "A 40-nm Cryo-CMOS Quantum Controller IC for Superconducting Qubit," IEEE J. Solid-State Circuits, vol. 57, pp. 3274– 3287, November 2022.

- [25] R. Acharya, S. Brebels, A. Grill, J. Verjauw, Ts. Ivanov, D. P. Lozano, D. Wan, J. Van Damme, A. M. Vadiraj, M. Mongillo, B. Govoreanu, J. Craninckx, I. P. Radu, K. De Greve, G. Gielen, F. Catthoor, A. Potočnik, "Overcoming I/O bottleneck in superconducting quantum computing: multiplexed qubit control with ultra-low-power, base-temperature cryo-CMOS multiplexer," arXiv:2209.13060, September 2022.

- [26] R. McDermott, M. G. Vavilov, B. L. T. Plourde, F. K. Wilhelm, P. J. Liebermann, O. A. Mukhanov, and T. A. Ohki, "Quantum-classical interface based on single flux quantum digital logic," Quantum Sci. Technol., vol. 3, 024004, January 2018.

- [27] C. H. Liu, A. Ballard, D. Olaya, D. R. Schmidt, J. Biesecker, T. Lucas, J. Ullom, S. Patel, O. Rafferty, A. Opremcak, K. Dodge, V. Iaia, T. McBroom, J. L. DuBois, P. F. Hopkins, S. P. Benz, B. L. T. Plourde, and R. McDermott, "Single Flux Quantum-Based Digital Control of Superconducting Qubits in a Multi-Chip Module," arXiv:2301.05696, January 2023.

- [28] F. Lecocq, F. Quinlan, K. Cicak, J. Aumentado, S. A. Diddams, and J. D. Teufel, "Control and readout of a superconducting qubit using a photonic link," Nat., vol. 591 pp. 575–579, March 2021.