# Performance Analysis and Comparison of Two 1T/1MTJ-based Logic Gates

Hiwa Mahmoudi, Thomas Windbacher, Viktor Sverdlov, and Siegfried Selberherr Institute for Microelectronics, TU Wien, Gußhausstraße 27–29/E360, A-1040 Wien, Austria, E-mail: {mahmoudi | windbacher | sverdlov | selberherr}@iue.tuwien.ac.at

*Abstract*—A performance analysis and comparison of two onetransistor/one-magnetic tunnel junction (1T/1MTJ)-based logic gates is presented. The energy consumption as well as the reliability of different Boolean logic functions utilizing the two circuit topologies are studied and the adequacy of their employment for specific non-volatile logic applications is discussed. It has been shown that the implication logic design exhibits a more reliable behavior compared to the reprogrammable logic design featuring conventional Boolean logic operations like (N)AND and (N)OR. Although the comparison between the two error optimized logic gate types shows that the fundamental logic operations with the reprogrammable gates require less energy than with the IMP gates, the situation reverses for more complex Boolean logic operations.

# I. INTRODUCTION

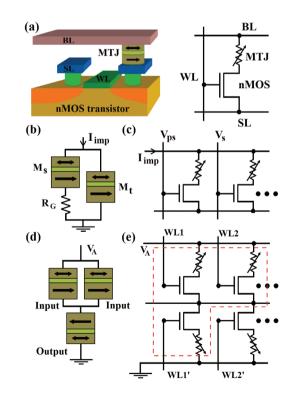

Because of scalability, unlimited endurance, fast switching speed, and CMOS compatibility [1], the spin-transfer torque magnetic tunnel junction (STT-MTJ) is a promising candidate for the replacement of the CMOS transistor, as the scaling of CMOS technologies becomes harder for every device generation [2], [3]. Recently, MTJ-based logic gates have been proposed which store logic variables as resistance states of the MTJs rather than voltage levels like in CMOS logic [4], [5], [6]. This extends non-volatile spintronics from sole memory applications to logic computation and provides zero-standby power computation. It also allows to shift away from the Von Neumann architecture by eliminating the need for data transfer between separate memory and logic units [7]. Due to easy integration with CMOS, MTJs can be placed within 1T/1MTJ cells (Fig. 1a) in an array to construct largescale circuits performing complex logic functions, in which all MTJs can be used arbitrarily as input or output for the computations [8].

In this work we present a performance analysis and comparison of implication [5] (Fig. 1b) and reprogrammable [6] (Fig. 1d) logic gates based upon the 1T/1MTJ structure as shown in Fig. 1c and Fig. 1e, respectively. The implication gate implements a fundamental Boolean logic operation called material implication (IMP) and the reprogrammable gate realizes the more common Boolean logic operations AND, OR, NAND, and NOR. For this type of MTJ-based logic gates the logic (resistance) states of the input MTJs act as the logic inputs and provide a state dependent (conditional) STT switching behavior on a target MTJ ( $M_t$  in Fig. 1b and the output MTJ in Fig. 1d).

# II. 1T/1MTJ CELL MODELING

Non-volatile MTJ-based logic relies on a conditional switching behavior of a target MTJ [5], [6]. Therefore, the reliability of an implemented logic operation is proportional to the product of the terms  $(1-E_i)$  of all MTJs in the respective logic gate.  $E_i$  denotes the error probability of the *i*<sup>th</sup> MTJ and is equal to the switching probability ( $S_i$ ) of the corresponding MTJ when its logic state has to be left unchanged (an undesired switching event). For example, any switching event in  $M_s$  in the implication gate or in an input MTJ in the reprogrammable gate is an undesired event. However, for a desired switching event we have  $E_i = 1 - S_i$ . An example of a desired switching in  $M_t$  when both  $M_s$  and  $M_t$  are initially in high resistance state (cf. Fig. 1b and Fig. 1c, [5]), according to the IMP truth table [9].

Fig. 1. (a) Structure and equivalent circuit of 1T/1MTJ cell. MTJ-based implication (b) [5] and reprogrammable (d) [6] logic gates. 1T/1MTJ-based realization of implication (c) and reprogrammable (e) logic gates.

For a given input combination, the error probability of the respective intrinsic logic operation (f) implemented using the implication or the reprogrammable gate is given by

$$E(f) = 1 - \prod_{i=1}^{n} [1 - E_i],$$

(1)

where n is the total number of the MTJs in the gate. Correct logic behavior of a logic operation is ensured, only when the logic gate has correct logic functionality for all possible input combinations. We further assume equal frequencies of occurrence for all input patterns, which allows us to use the average of E(f) in our simulations.

According to the theoretical model [10] and the measurements [11], the switching probability (S) of an MTJ in the thermally-activated switching regime is given by

$$S_{\rm i} = 1 - \exp\left\{-\frac{t}{\tau_0} \exp\left[-\Delta\left(1 - \frac{I_{\rm i}}{I_{\rm C0}}\right)\right]\right\},\tag{2}$$

where  $\Delta$  is the MTJs thermal stability factor (= $E/k_{\rm B}T$  and E denotes the energy barrier between the magnetization states),  $I_{\rm i}$  indicates the current flowing through the  $i^{\rm th}$  MTJ, t is the current pulse duration,  $\tau_0 \sim 1$ ns, and  $I_{\rm C0}$  represents the critical switching current extrapolated to  $\tau_0$  [12]. In order to calculate the current  $I_{\rm i}$  for each MTJ, (3) and (4) are used to take into account the channel resistance of the access transistor [13] and the voltage-dependent MTJ resistance (effective TMR model [14]), respectively:

$$R_{\rm on} = \frac{V_{\rm DS}}{\mu_{\rm n} C_{\rm ox} \frac{W}{L} \left[ (V_{\rm GS} - V_{\rm TH}) V_{\rm DS} - \frac{V_{\rm DS}^2}{2} \right]},\tag{3}$$

$$R_{\rm i} = (1 + \text{TMR}_{\rm eff}) R_{\rm P} = \left(1 + \frac{\text{TMR}_0}{1 + \frac{V_i^2}{V_h^2}}\right) R_{\rm P}.$$

(4)

Here,  $V_{\rm GS}$  ( $V_{\rm DS}$ ) is the voltage difference between the gate (drain) and the source of the access transistor,  $\mu_{\rm n}$  is the mobility of electrons,  $C_{\rm ox}$  is the oxide thickness, and W (L)

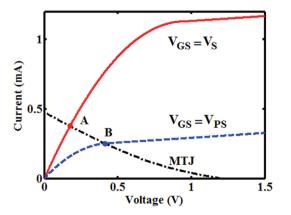

Fig. 2. Bias points of the access transistor in a 1T/1MTJ cell for the selecting (point A) and pre-selecting (point B) voltages applied to the word line of the cell.

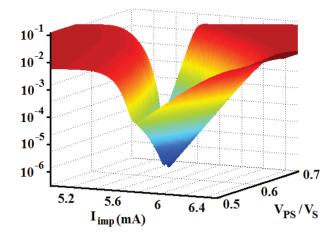

Fig. 3. Circuit parameters ( $I_{\rm imp}$ ,  $V_{\rm s}$ , and  $V_{\rm ps}$ ) optimization for minimum implication gate error probability with MTJs characterized by  $R_{\rm P} = 1.8 \mathrm{k}\Omega$ , TMR= 3, and  $\Delta = 70$ .

is the channel width (length). The transistors are supposed to operate in the triode (ohmic) region ( $V_{\rm GS}$  >  $V_{\rm TH}$  and  $V_{\rm DS} < V_{\rm GS} - V_{\rm TH}$ ). TMR<sub>0</sub> (TMR<sub>eff</sub>) is the tunnel magnetoresistance (TMR) ratio under zero (non-zero) bias voltage (Vi), and  $V_h$  is the bias voltage equivalent to  $TMR_{eff} = TMR_0/2$ . Although the ON resistance of the access transistors decreases the effective TMR of the 1T/1MTJ cell by about 10% [15], the structural asymmetry restriction of the implication gate (Fig. 1b) due to  $R_{\rm G}$  is lifted by the topology shown in Fig. 1c, where the access transistors are used as voltage-controlled resistors [8]. In fact, the IMP operation can be executed by applying the current  $I_{imp}$  to the common bit line (BL) and selecting and pre-selecting voltages ( $V_{\rm s}$  and  $V_{\rm ps}$ ) to two arbitrary word lines (WLs) simultaneously. As  $V_{\rm DS} < V_{\rm s}$ , the transistors have different bias points (Fig. 2) and thus exhibit different channel resistances. The circuit parameters  $I_{\rm imp}$ ,  $V_{\rm s}$ , and  $V_{\rm ps}$  in the implication gate and the voltage level  $V_{\rm A}$  in the reprogrammable gate can be optimized to minimize their error

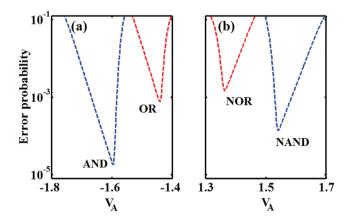

Fig. 4. Circuit parameter ( $V_A$ ) optimization for minimum reprogrammable gate error probability with MTJs characterized by  $R_P = 1.8$ k $\Omega$ , TMR= 3, and  $\Delta =$ 70.

Ì

probabilities (E(f)) of each intrinsic operation (f) as shown in Fig. 3 and Fig. 4. According to the logical definitions for the MTJs' high  $(R_{AP})$  and low  $(R_P)$  resistance states  $(R_{AP} \equiv "1"$ and  $R_P \equiv "0"$  or vice-versa), the intrinsic logic function executed by the implication gate is corresponding to the IMP or NIMP (negated IMP) operation [5]. In combination with low-to-high resistance switching, the implication operation forms a complete basis [9]. Therefore, any Boolean function can be implemented using implication logic without need for any other gate type. In order to be consistent with [6], we use the convention of Shannon  $(R_{AP} \equiv "1" \text{ and } R_P \equiv "0")$ . Thus, the low-to-high resistance switching is equivalent to the TRUE operation and the realized intrinsic function by the implication logic corresponds to the NIMP operation.

### **III. RESULTS AND DISCUSSION**

As mentioned before, the IMP/NIMP operation is the intrinsic function of the implication gate in one step. Other logic functions are implemented by using subsequent FALSE/TRUE and IMP/NIMP operations [16]. For example, NOT and NOR operations can be performed in two and three steps as

$$a_{2} \leftarrow \text{NOT} \ a_{1} \tag{5}$$

$$\equiv \{a_{2} \leftarrow 1, \ a_{2} \leftarrow a_{1} \text{ NIMP } a_{2}\},$$

$$a_{3} \leftarrow a_{1} \text{ NOR } a_{2} \tag{6}$$

$$\equiv \{a_3 \leftarrow 1, \ a_3 \leftarrow a_1 \text{ NIMP } a_3, \ a_3 \leftarrow a_2 \text{ NIMP } a_3\}.$$

For the reprogrammable gate the AND, OR, NAND, and NOR operations are the intrinsic logic functions implemented in two steps including a preset (TRUE or FALSE in the output MTJ) and a conditional switching provided by the voltage pulse  $V_A$ . Any other logic function can be performed by using subsequent TRUE, FALSE, and intrinsic operations. For example, NOT and NOR operation can be executed as:

$$b_1 \leftarrow \text{NOT } a_1 \tag{7}$$

$$\equiv \{a_2 \leftarrow 1, \ b_1 \leftarrow 0, \ b_1 \leftarrow a_1 \text{ NAND } a_2\}$$

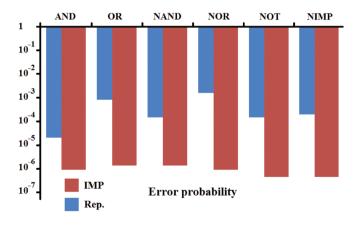

Fig. 5. Minimum error probability of the implication (IMP) and the reprogrammable (Rep.) based implementations of some basic Boolean logic operations.

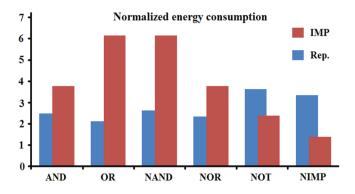

Fig. 6. Normalized energy consumption of the Boolean logic operations shown in Fig. 5. The energy is normalized by the amount of energy required for high-to-low MTJ resistance switching ( $\sim$ 18pJ for t = 50ns, based on physical devices characterized in [11]).

$$b_1 \leftarrow a_1 \text{ NOR } a_2 \tag{8}$$

$$\equiv \{b_1 \leftarrow 0, \ b_1 \leftarrow a_1 \text{ NOR } a_2\},$$

where  $a_j$  ( $b_j$ ) represents the logic data stored in the  $j^{\text{th}}$  1T/1MTJ cell in the input (output) array.

In order to perform a fair comparison, we assume the same device (MTJ and transistor) characteristics for both logic gates and calculate the optimum circuit parameters with respect to their minimum error probabilities of the intrinsic functions (Fig. 3 and Fig. 4). It can be shown that the error probability of a TRUE or FALSE operation is negligible compared to the error probabilities of the conditional switching events required for implementation of the intrinsic functions using implication or reprogrammable gate. Therefore, the same equation (1) is used to calculate the error probability of a more complex Boolean logic function in which  $E_i$  is the error probability of the  $i^{\text{th}}$  intrinsic functions and n is the total number of successive conditional switching events based on either implication or reprogrammable gates. Fig. 5 shows the error probabilities for some basic Boolean logic operations using implication and reprogrammable gates with optimized circuit parameters. It illustrates that, even for the intrinsic functions of the reprogrammable gate, the implication logic exhibits about 1-3 orders of magnitude higher reliability than the reprogrammable gate. It is worth mentioning that the AND and the NAND are the most reliable intrinsic functions when using reprogrammable gates.

Fig. 6 shows the energy consumptions of implication- and reprogrammable-based implementations calculated using the Spice model for the STT-MTJs from [12]. Due to the mismatch between the intrinsic logic functions of the gates, the IMP-based implementation requires more energy (by an average factor of  $\sim$ 1.4) as compared to the reprogrammable-based implementation for the basic Boolean logic operations.

In order to see the performance at larger circuits, we calculated the error probabilities and the energy consumptions of more complex Boolean functions comprising a XOR, a Half Adder, and a Full Adder implemented by implication and

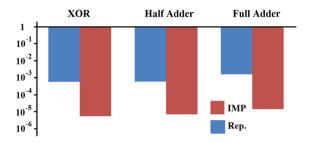

Fig. 7. Minimum error probability of the implication (IMP) and the reprogrammable (Rep.) based implementations of XOR, Half Adder, and Full Adder logic functions. In order to minimize the error probability of the reprogrammable-based implementation, the logic functions are based on AND and NAND operations.

reprogrammable gates. For the reprogrammable gate, we use only AND and NAND operations to provide the most reliable design. For example, although the number of required steps is increased, the following implementation is preferred over (8) in a reliability-based design of the NOR operation:

$$a_3 \leftarrow a_1 \text{ NOR } a_2 \tag{9}$$

$$\equiv \{b_1 \leftarrow \text{NOT } a_1, b_2 \leftarrow \text{NOT } a_2, \ a_3 \leftarrow b_1 \text{ AND } b_2\}.$$

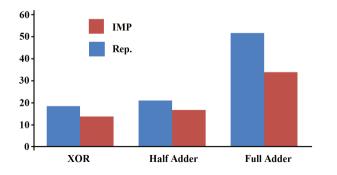

Fig. 7 shows that the implication-based implementation of more complex functions exhibits about two orders of magnitude higher reliability than the most reprogrammable gates design. Furthermore, for logic functions which are not inherently covered by the gates, e.g. (N)AND, (N)OR for the reprogrammable gate, the implication-based logic also performs better with respect to power consumption (Fig. 8).

#### IV. CONCLUSION

A performance analysis and comparison of 1T/1MTJ-based logic implication and reprogrammable logic gates has been presented. It has been shown that for the intrinsic (N)AND and (N)OR operations, the reprogrammable gate requires slightly less power than the corresponding IMP implementation. However, 1T/1MTJ-based implication logic enables a more reliable logic behavior as compared to the reprogrammable gates.

Fig. 8. Normalized energy consumption of the Boolean logic operations shown in Fig. 7.

Furthermore, the IMP implementation outperforms the reprogrammable gate for more complex logic functions and is thus the implementation of choice for large-scale logic circuits.

## ACKNOWLEDGMENT

The work is supported by the European Research Council through the grant #247056 MOSILSPIN.

#### REFERENCES

- C. Chappert, A. Fert, and F. N. V. Dau, "The Emergence of Spin Electronics in Data Storage," *Nat. Mater.*, vol. 6, pp. 813–823, 2007.

- [2] N. S. Kim, T. Austin, D. Baauw, T. Mudge, K. Flautner, J. S. Hu, M. J. Irwin, M. Kandemir, and V. Narayanan, "Leakage Current: Moore's Law Meets the Static Power," *Computer*, vol. 36, pp. 68–75, 2003.

- [3] W. Zhao, L. Torres, Y. Guillemenet, L. V. Cargnini, Y. Lakys, J.-O. Klein, D. Ravelosona, G. Sassatelli, and C. Chappert, "Design of MRAM Based Logic Circuits and its Applications," *Proceedings of the ACM Great Lakes Symposium on VLSI*, pp. 431–436, 2011.

- [4] A. Lyle, J. Harms, S. Patil, X. Yao, D. Lilja, and J. P. Wang, "Direct Communication Between Magnetic Tunnel Junctions for Nonvolatile Logic Fan-out Architecture," *Appl. Phys. Lett.*, vol. 97, p. 152504, 2010.

- [5] H. Mahmoudi, T. Windbacher, V. Sverdlov, and S. Selberherr, "Implication Logic Gates using Spin-Transfer-Torque-Operated Magnetic Tunnel Junctions for Intrinsic Logic-in-Memory," *Solid-State Electron.*, vol. 84, pp. 191–197, 2013.

- [6] A. Lyle, S. Patil, J. Harms, B. Glass, X. Yao, D. Lilja, and J. P. Wang, "Magnetic Tunnel Junction Logic Architecture for Realization of Simultaneous Computation and Communication," *IEEE Trans. Magn.*, vol. 47, pp. 2970–2973, 2011.

- [7] S. Matsunaga, J. Hayakawa, S. Ikeda, K. Miura, T. Endoh, H. Ohno, and T. Hanyu, "MTJ-Based Nonvolatile Logic-in-Memory Circuit, Future Prospects and Issues," *Proc. Des. Autom. Test Eur. Conf. (DATE)*, pp. 433–435, 2009.

- [8] H. Mahmoudi, V. Sverdlov, and S. Selberherr, "MRAM-based Logic Array for Large-Scale Non-Volatile Logic-in-Memory Applications," *IEEE/ACM International Symposium on Nanoscale Architectures* (NanoArch), Accepted-2013.

- [9] J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart, and R. S. Williams, "Memristive Switches Enable Stateful Logic Operations via Material Implication," *Nature*, vol. 464, pp. 873–876, 2010.

[10] Y. Higo, K. Yamane, K. Ohba, H. Narisawa, K. Bessho, M. Hosomi,

- [10] Y. Higo, K. Yamane, K. Ohba, H. Narisawa, K. Bessho, M. Hosomi, and H. Kano, "Thermal Activation Effect on Spin Transfer Switching in Magnetic Tunnel Junctions," *Appl. Phys. Lett.*, vol. 87, p. 082502, 2005.

- [11] M. Hosomi, H. Yamagishi, T. Yamamoto, K. Bessho, Y. Higo, K. Yamane, H. Yamada, M. Shoji, H. Hachinoa, C. Fukumoto, H. Nagao, and H. Kano, "A Novel Nonvolatile Memory with Spin Torque Transfer Magnetization Switching: Spin-RAM," *IEDM Tech. Dig.*, pp. 459–462, 2005.

- [12] J. D. Harms, F. Ebrahimi, X. F. Yao, and J. P. Wang, "SPICE Macromodel of Spin-Torque-Transfer-Operated Magnetic Tunnel Junctions," *IEEE Trans. Electron Devices*, vol. 57, pp. 1425–1430, 2010.

- [13] B. Razavi, Fundamentals of Microelectronics. Wiley, 2006.

- [14] Y. Zhang, W. Zhao, Y. Lakys, J. O. Klein, J. V. Kim, D. Ravelosona, and C. Chappert, "Compact Modeling of Perpendicular-Anisotropy CoFeB/MgO Magnetic Tunnel Junctions," *IEEE Trans. Electron De*vices, vol. 59, pp. 819–826, 2012.

- [15] R. Beach, T. Min, C. Horng, Q. Chen, P. Sherman, S. Le, S. Young, K. Yang, H. Yu, X. Lu, W. Kula, T. Zhong, R. Xiao, A. Zhong, G. Liu, J. Kan, J. Yuan, J. Chen, R. Tong, J. Chien, T. Torng, D. Tang, P. Wang, M. Chen, S. Assefa, M. Qazi, J. DeBrosse, M. Gaidis, S. Kanakasabapathy, Y. Lu, J. Nowak, E. O'Sullivan, T. Maffitt, J. Sun, and W. Gallagher, "A Statistical Study of Magnetic Tunnel Junctions for High-Density Spin Torque Transfer-MRAM (STT-MRAM)," *IEDM Tech. Dig.*, pp. 1–4, 2008.

- [16] H. Mahmoudi, V. Sverdlov, and S. Selberherr, "A Robust and Efficient MTJ-based Spintronic IMP Gate for New Logic Circuits and Large-Scale Integration," *Proceedings of the 17th International Conference* on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 225–228, 2012.