# A Robust and Efficient MTJ-based Spintronic IMP Gate for New Logic Circuits and Large-Scale Integration

Hiwa Mahmoudi, Viktor Sverdlov, and Siegfried Selberherr Institute for Microelectronics, TU Wien, Gußhausstraße 27–29/E360, A-1040 Wien, Austria E-mail: {mahmoudi | sverdlov | selberherr}@iue.tuwien.ac.at

Abstract— A novel circuit topology of a spintronic stateful implication (IMP) logic gate based on a spin transfer torqueoperated magnetic tunnel junction (STT-MTJ) is proposed and analyzed. It is demonstrated that the proposed topology reduces the IMP error and also the energy consumption by about 60% as compared to the conventional one. Stateful IMP-based logic uses the nonvolatile memory unit (MTJ device) as the main computing element (logic gate) unlike the previously proposed MTJ-based logic-in-memory circuits, where MTJs are only ancillary devices in logical computations. Since the MTJ devices are CMOS compatible, the generalization of the spintronic IMP gate to a large-scale nonvolatile logic-in-memory system is compulsory. As an example we consider an IMP-based implementation of a full adder. In contrast to an earlier proposed IMP-based full adder with 37 operations, our design involves only 27 subsequent FALSE and IMP operations.

Keywords- implication (IMP) logic; nonvolatile logic-inmemory; magnetic tunnel junction (MTJ); spin transfer torque (STT)

#### INTRODUCTION

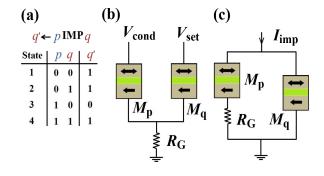

Material implication (IMP) is a fundamental Boolean logic operation on two variables p and q ('p IMP q' or 'if p, then q'), which is equivalent to '(NOT p) OR q' as shown in Fig. 1a. Although it is in common use by logicians, it is seldomly discussed in computing and electrical engineering communities. In combination with the FALSE operation (writing Logical 0), the IMP operation forms a complete logic basis in which any Boolean function can be computed.

Recently, the realization of the IMP operation in a simple circuit including a linear resistor and two titanium dioxide (TiO<sub>2</sub>) memristive switches was reported [1] to enable stateful logic operations, for which the memristive switches serve simultaneously as logic gates and latches. The resistance switching ratio of the TiO<sub>2</sub> memristive switches [2], [3] is about two orders of magnitude higher than the theoretical maximum of the magnetic tunnel junction (MTJ) switches [4], [5]. This high ratio guarantees the expected logic output by providing a high state dependent modulation (SDM) of the current or voltage required for switching.

In this work the realization of the IMP operation using spin transfer torque (STT)-operated MTJ devices based on a critical

current density required for STT switching and a positive feedback between the MTJ resistance changes during the switching and the current density above the threshold has been demonstrated in a new circuit topology (Fig. 1c) as compared to the conventionally used topology (Fig. 1b).

## MTJ-BASED IMP LOGIC GATES ANALYSIS

The MTJ contains two ferromagnetic layers separated by a thin non-conductive tunneling barrier. The electrical resistance of the device depends on the relative orientation of the magnetization directions of the ferromagnetic layers. The parallel (P) magnetization state results in a low-resistance state (R<sub>P</sub>; logical 1) across the barrier, while the antiparallel (AP) alignment places it in a high-resistance state (R<sub>AP</sub>; logical 0) and the resistance modulation is described by the tunnel magnetoresistance (TMR) ratio, defined as  $(R_{AP} - R_P)/R_P$ .

The magnetization of one layer (fixed layer) is pinned, while the magnetization of the second one (free layer) can be switched freely using an external magnetic field or (spin) current passing through the MTJ (STT effect [6], [7]). The STT technique [8] uses spin-polarized electrons to induce directly torque on the magnetization of the free layer and requires a critical current density for switching. With the MTJ-based IMP gate, the initial logic states of the MTJ devices  $(M_p \text{ and } M_q)$ provide a state dependent modulation of the voltage or current of the target MTJ  $(M_a)$  which is equivalent to the IMP operation.

Figure 1. (a) IMP truth table. Conventional (b) [1] and proposed (c) IMP circuit topologies.

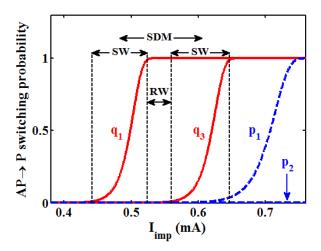

Figure 2. Switching probabilities of Mq and Mp for a 50ns IMP operation based on physical devices characterized in [8].

As shown in Fig. 1b, with the conventional topology performing the IMP operation involves simultaneously applying two voltage pulses,  $V_{SET}$  and the  $V_{COND}$ , to  $M_q$  and  $M_p$ respectively and the initial logic state of the source MTJ  $(M_p)$ provides a state dependent modulation of the voltage across the target MTJ  $(M_a)$  through  $R_G$ . In fact, when MP is in the parallel state (p=1; State 3 and State 4),  $q \leftarrow (p \text{ IMP } q) \equiv (0 \text{ OR } q) \equiv$ q, the pulse  $V_{COND}$  mostly drops on  $R_G$ , so the pulse  $V_{SET}$  cannot change q, and both  $M_p$  and  $M_q$  are left unchanged. But when  $M_p$ is in the antiparallel state (p = 0; State 1 and State 2),  $q \leftarrow (p = 0)$ IMP q)  $\equiv$  (1 OR q)  $\equiv$  1, the pulse  $V_{COND}$  generates a lower current so the common line voltage decreases and  $V_{SET}$  can switch  $M_q$  to the parallel state (q = 1) when it is in the antiparallel state. A positive feedback between the memristance  $M_a$  and the driving strength accelerates the switching in State 1. It increases the current passing through  $M_q$ , while it decreases the current of  $M_p$ , so  $M_q$  is set  $(q \leftarrow 1)$ , while p is left unchanged (p = 0).

With our proposed topology shown in Fig. 1c the initial logic state of  $M_p$  provides a state dependent modulation of the current through  $M_q$ , which results in a correct logic behavior of  $M_q$ . Because of  $R_G$ , the current through  $M_p$  is low enough to leave it unchanged. Therefore the current pulse  $I_{imp}$  can only switch  $M_q$ , when it is in the antiparallel state (q=0; State 1 and State 3). In State 1  $M_p$  is in the antiparallel state, therefore a major part of the  $I_{imp}$  will pass through  $M_q$  and switch it to the parallel state (q=1). In State 3  $M_p$  is in the parallel state, therefore more current will flow through  $M_p$  which reduces the current flowing through  $M_a$  making it below the critical current required for switching. Fig. 2 shows all possible AP $\rightarrow$ P switching probabilities of  $M_q$  and  $M_p$  as a function of the current  $I_{imp}$  for a given value of  $R_G$  and pulse duration. It illustrates how the state dependent modulation (SDM) opens a reliable window (RW) between the AP-P switching probability windows (SW) of the  $M_q$  in State 1 and State 3. In fact for a current  $I_{imp}$  in the interval RW the IMP gate shows a correct logical behavior for which only  $M_a$  will switch only in

## III. MODELING

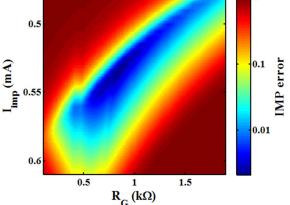

As described before, both, the conventional and the proposed topology enable stateful logic by performing the IMP operation. The IMP gate circuit parameters ( $R_G$ ,  $V_{SET}$ , and  $V_{COND}$  for the conventional and  $I_{imp}$  and  $R_G$  for the proposed topology) can be optimized to minimize the error for determined pulse duration and MJT device characteristics. An example of such an optimization is shown in Fig. 3 for the proposed topology. In order to analyze the reliability of the IMP gates, we use the theoretical expressions (1) and (1') [9] of the MTJ switching probability which has been experimentally proved in [8]:

$$P_{sw}^{qi} = 1 - \exp\left\{-\frac{t}{\tau_0} \exp\left[-\Delta_0 \left(1 - \frac{I_{qi}}{I_{C0}}\right)\right]\right\},\tag{1}$$

$$P_{sw}^{pi} = 1 - \exp\left\{-\frac{t}{\tau_0} \exp\left[-\Delta_0 \left(1 - \frac{I_{pi}}{I_{C0}}\right)\right]\right\}, \quad (1')$$

where  $P_{sw}^{qi}$  ( $P_{sw}^{pi}$ ) and  $I_{qi}$  ( $I_{pi}$ ) are the AP $\rightarrow$ P switching probabilities and the current flowing through  $M_q$  ( $M_p$ ) in State i (i=1, 2, 3, or 4 as shown in Fig. 1a),  $\Delta_0$  is the magnetic memorizing energy without any current and magnetic field,  $\tau_0$  is 1ns,  $I_{C0}$  is the critical switching current extrapolated to 1 ns, and t is the pulse width. According to the IMP truth table (Fig. 1a), we define the IMP error as:

$$E_{imp} = (1 - P_{sw}^{q1}) + P_{sw}^{q3} + P_{sw}^{p1} + P_{sw}^{p2}$$

(2)

In order to calculate  $I_{qi}$  and  $I_{pi}$  for each topology in each state we use the resistance model of the MTJ in the antiparallel state [7]

$$R_{AP} = R_{P} \left( 1 + TMR_{real} \right) = R_{P} \left( 1 + \frac{TMR_{0}}{1 + \frac{V_{bias}^{2}}{V_{h}^{2}}} \right)$$

(3)

Figure 3. The IMP error as a function of  $R_G$  and  $I_{imp}$  based on physical MTJ devices characterized in [8] for a pulse duration of 50ns.

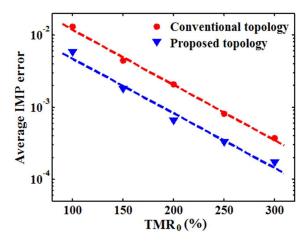

Figure 4. The average IMP error as a function of the  $TMR_0$  ratio for both conventional and proposed topologies.

where  $\text{TMR}_{\text{real}}$  and  $\text{TMR}_0$  are the TMR ratio under non-zero and zero bias voltage ( $V_{bias}$ ), respectively and  $V_h$  is the bias voltage equivalent to  $\text{TMR}_{\text{real}} = 0.5 \text{ TMR}_0$ .

## IV. SIMULATION RESULTS AND DISCUSSION

Reliable IMP logic behavior requires a wide enough SDM of voltage or current on the  $M_q$ . The most important parameter in robust IMP gate design is the TMR ratio. The difference between the initial voltage or current on  $M_q$  and  $M_p$  in different initial states increases with increasing TMR ratio of the MTJs devices. Therefore, increasing the TMR ratio enlarges the SDM and the RW windows shown in Fig. 2. Fig. 4 shows the minimum IMP error for different TMR $_0$  ratios with optimal circuit parameters ( $R_G$ ,  $V_{SET}$ , and  $V_{COND}$  for the conventional and  $I_{imp}$  and  $R_G$  for the proposed topology). It demonstrates that in both conventional and proposed topologies the IMP error decreases exponentially with increasing TMR ratio. At a fixed TMR the proposed topology provides a higher SDM, thus reducing the IMP error by about 60% as compared to the conventional one.

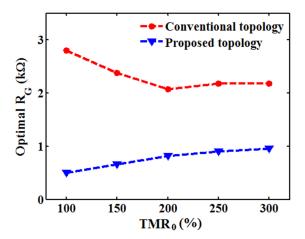

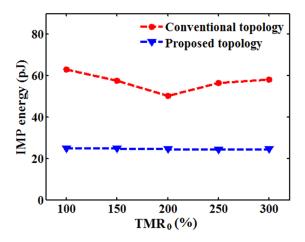

Fig. 5 shows the optimal value of  $R_G$  for different TMR<sub>0</sub> ratios with both topologies. It illustrates that the optimal  $R_G$  is lower in the proposed topology as compared to the conventional one. Since in the conventional topology all the current required for switching  $M_q$  will pass through  $R_G$ , higher  $R_G$  results in higher energy consumption for switching events of the IMP operation. Fig. 6 shows the IMP energy consumption calculated using the SPICE model of the MTJ [10]. It demonstrates that in the proposed topology, the IMP energy consumption is about 60% lower than in the conventional one.

# V. LARGE-SCALE INTEGRATION

Stateful IMP-based logic allows the cells to both store logic values and perform logic operations. Since the MTJ devices are CMOS compatible, the generalization of the spintronic IMP gate to a nonvolatile logic-in-memory system is compulsory.

Figure 5. The optimal value of  $R_G$  (corresponding to the minimum error design) depends on the TMR<sub>0</sub> ratio.

It can be shown that based on the 1T/1MTJ structure in the spin-RAM architecture [8], the proposed topology of an IMP gate can be achieved by applying a current pulse  $(I_{imp})$  to two bit lines simultaneously and connecting one source line directly to the ground (source line of  $M_q$ ) and connecting the second source line to the ground through  $R_G$  (source line of  $M_p$ ). Therefore, a large-scale logic-in-memory circuit can be achieved based on the existing magnetic memory technology for which the non-volatile memory element (MTJ) is used as the main computing element (logic gate) at the same time, in contrast to the previous logic-in-memory or MOS/MTJ-hybrid logic circuits [11]-[14] for which the non-volatile memory elements are used as ancillary devices for logical computations.

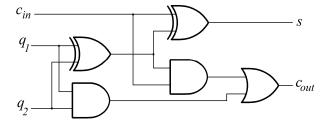

We consider an IMP-based implementation of a full adder which is a basic element of arithmetic circuits. As is well known, a full adder adds three binary inputs  $(q_1, q_2 \text{ and } c_{in})$  and produces two binary outputs, sum (s) and carry  $(c_{out})$  as shown in Fig. 7.

Figure 6. The IMP energy consumption depends on the  $TMR_0$  ratio for both conventional and proposed topologies.

Figure 7. A logic diagrame of a full adder.

Since IMP cannot fan out, some additional memory elements  $(a_1, a_2, \text{ and } a_3)$  are required to ensure that a logical value  $(q_1, q_2 \text{ and } c_{in})$  is still available, when it is needed as an input for subsequent IMP operations. We use two subsequent operations, FALSE  $(a_i \leftarrow 0)$  and IMP  $(a_i \leftarrow q_i \text{ IMP } a_i)$ , to write  $\overline{q_i}$  (NOT  $q_i$ ) in the additional cell  $a_i$  (i =1-3), in order to ensure that the logical value  $\overline{q_i}$  (therefore  $q_i$ ) will be available as an input for subsequent steps. As ' $q_1$  IMP  $q_2$ ' is equivalent to '(NOT  $q_1$ ) OR  $q_2$ ', some operations can be eliminated to minimize the total effort for performing a full adder. In contrast to the earlier proposed IMP-based full adder [15] with 19 and 18 operations (37 total) for generating s and  $c_{out}$ , respectively, and 4 additional bits, our design involves only 27 subsequent FALSE and IMP operations on inputs  $(q_1, q_2, \text{ and } c_{in})$  and 3 additional bits  $(a_1, a_2, \text{ and } a_3)$  as

$$a_{1} \leftarrow 0, a_{1} \leftarrow q_{1} \text{ IMP } a_{1}, a_{2} \leftarrow 0, a_{2} \leftarrow q_{2} \text{ IMP } a_{2},$$

$$a_{2} \leftarrow a_{1} \text{ IMP } a_{2}, a_{3} \leftarrow 0, a_{3} \leftarrow a_{2} \text{ IMP } a_{3}, a_{2} \leftarrow 0,$$

$$a_{2} \leftarrow q_{2} \text{ IMP } a_{2}, a_{1} \leftarrow a_{2} \text{ IMP } a_{1}, a_{3} \leftarrow a_{1} \text{ IMP } a_{3},$$

$$(a_{3} \leftarrow q_{1} \text{ XOR } q_{2})$$

$$a_{2} \leftarrow q_{1} \text{ IMP } a_{2}, q_{1} \leftarrow 0, q_{1} \leftarrow a_{3} \text{ IMP } q_{1},$$

$$q_{1} \leftarrow c_{in} \text{ IMP } q_{1}, q_{2} \leftarrow 0, q_{2} \leftarrow q_{1} \text{ IMP } q_{2}, q_{2} \leftarrow a_{2} \text{ IMP } q_{2},$$

$$(q_{2} \leftarrow c_{out})$$

$$a_{1} \leftarrow 0, a_{1} \leftarrow c_{in} \text{ IMP } a_{1}, q_{1} \leftarrow 0, q_{1} \leftarrow a_{3} \text{ IMP } q_{1},$$

$$q_{1} \leftarrow a_{1} \text{ IMP } q_{1}, a_{1} \leftarrow 0, a_{1} \leftarrow q_{1} \text{ IMP } a_{1},$$

$$c_{in} \leftarrow a_{3} \text{ IMP } c_{in}, c_{in} \leftarrow a_{1} \text{ IMP } c_{in},$$

$$(a_{3} \leftarrow q_{1} \text{ XOR } q_{2} \text{ XOR } c_{in}).$$

The MOS/MTJ-hybrid logic circuit presented in [11] uses 34 transistors and 4 MTJs for implementing an MTJ-based full adder, while our proposed spintronic stateful logic architecture uses 6 1T/1MTJ cells for a full adder for which the 1T/1MTJ cells serve simultaneously as logic gates and latches.

# VI. CONCLUSION

We have shown the possibility of the realization of a logic operation named material implication (IMP) in two different circuit topologies, each one including a conventional resistor and two MTJs. It has been demonstrated that the IMP error decreases exponentially with increasing the TMR ratio of the MTJ devices. Our proposed IMP circuit topology reduces the IMP error and energy consumption by about 60% as compared to the conventional one.

The generalization of these spintronic IMP gates to a nonvolatile logic-in-memory system enable extending nonvolatile electronics from memory to logical computing applications, for which the STT-MTJ cells serve simultaneously as logic gates and latches and are not ancillary devices for logical computations as compared to conventional logic-in-memory circuits [11], [13]. This can improve the conventional CMOS logic and also opens the door for a shift away from the Von Neumann architecture for innovation in computational paradigms.

#### ACKNOWLEDGMENT

This work is supported by the European Research Council through the grant #247056 MOSILSPIN.

#### REFERENCES

- J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart, and R. S. Williams, "Memristive switches enable stateful logic operations via material implication," Nature, vol. 464, no. 7290, pp. 873–876, 2010.

- [2] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," Nature, vol. 453, no. 7191, pp. 80–83, 2008.

- [3] M. D. Pickett, D. B. Strukov, J. L. Borghetti, J. J. Yang, G. S. Snider, D. R. Stewart, and R. S. Williams, "Switching dynamics in titanium dioxide memristive devices," J. Appl. Phys. vol. 106, p. 074508, 2009.

- [4] W. H. Butler, X.-G. Zhang, T. C. Schulthess, and J. M. MacLaren, "Spin-dependent tunneling conductance of Fe|MgO|Fe sandwiches," Phys. Rev. B, vol. 63, p. 054416, 2001.

- [5] J. Mathonand and A. Umersky, "Theory of tunneling magnetoresistance of an epitaxial Fe/MgO/Fe(001) junction," Phys. Rev. B, vol. 63, p. 220403, 2001.

- [6] J. C. Slonczewski, "Current-driven excitation of magnetic multilayers," J. of Magn. and Magn. Mater., vol. 159, pp. L1–L7, 1996.

- [7] L. Berger, "Emission of spin waves by a magnetic multilayer traversed by a current," Phys. Rev. B, Condens. Matter, vol. 54, pp. 9353–9358, 1996.

- [8] M. Hosomi, H. Yamagishi, T. Yamamoto, K. Bessho, Y. Higo, K. Yamane, H. Yamada, M. Shoji, H. Hachinoa, C. Fukumoto, H. Nagao, and H. Kano, "A novel nonvolatile memory with spin torque transfer magnetization switching: Spin-RAM," IEDM Tech. Dig., pp. 459–462, 2005

- [9] Y. Higo, K. Yamane, K. Ohba, H. Narisawa, K. Bessho, M. Hosomi, and H. Kano, "Thermal activation effecton spin transfer switching in magnetic tunnel junctions," Appl. Phys. Lett., vol. 87, p. 082502, 2005.

- [10] J. D. Harms, F. Ebrahimi, X. F. Yao, and J. P. Wang, "SPICE macro-model of spin-torque-transfer-operated magnetic tunnel junctions," IEEE Trans. Electron Devices, vol. 57, no. 6, pp. 1425–1430, 2010.

- [11] S. Matsunaga, J. Hayakawa, S. Ikeda, K. Miura, T. Endoh, H. Ohno, and T. Hanyu, "MTJ-based nonvolatile logic-in-memory circuit, future prospects and issues," Proc. Des. Autom. Test Eur. Conf. (DATE), pp. 433–435, 2009.

- [12] W. S Zhao, C. Chappert, V. Javerliac and J.-P. Noizière, "High speed, high stability and low power sensing amplifier for MTJ/CMOS hybrid logic circuits", *IEEE Trans. Magn.*, vol. 45, no. 10, pp. 3784 -3787, 2009.

- [13] Y. Gang, W. Zhao, J. O. Klein, C. Chappert, and P. Mazoyer, "A high-reliability, low-power magnetic full adder," IEEE Trans. Magn., vol. 47, no. 11, pp. 4611–4616, 2011.

- [14] Y. Lakys, W. Zhao, J.-O. Klein, and C. Chappert, "Low power, high reliability magnetic flip-flop," Electron. Lett., vol. 46, pp.1493-1494, 2010.

- [15] K. Bickerstaff and E.E. Swartzlander, "Memristor-based arithmetic,", In Proc. Conf. 44<sup>th</sup> Asilomar Conf. Signals Syst. Comput., pp. 1173 – 1177, 2010.