# Circuit-Simulation Model of Gate-Drain-Capacitance Changes in Small-Size MOSFETs Due to High Channel-Field Gradients

D. Navarro, K. Hisamitsu, T. Yamaoka, M. Tanaka, H. Kawano,

H. Ueno, M. Miura-Mattausch, H. J. Mattausch<sup>1</sup>,

S. Kumashiro<sup>2</sup>, T. Yamaguchi<sup>2</sup>, K. Yamashita<sup>2</sup>, and N. Nakayama<sup>2</sup>

Graduate School of Advanced Sciences of Matter, <sup>1</sup>Research Center for Nanodevices and Systems,

Hiroshima University 1-4-1, Kagamiyama, Higashi-Hiroshima, 739-8527, Japan

Phone: +81-824-24-7637 Fax: +81-824-22-7195 E-mail: navarro@hiroshima-u.ac.jp

<sup>2</sup>Semiconductor Technology Academic Research Center, 3-17-2, Shin Yokohama, Kanagawa, 222-0033, Japan

Abstract - The field gradient along the MOSFET channel is included in the modeling of the gate-drain capacitance  $(C_{\rm gd})$  by an induced capacitance approach. The new approach has been successfully implemented in surface-potential based model HiSIM (Hiroshima-university STARC IGFET Model) and is capable of reproducing measured effects, which are particularly significant for pocket-implant technology, accurately.

#### I. INTRODUCTION

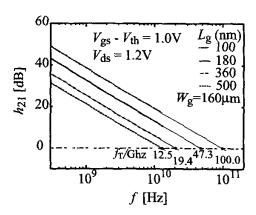

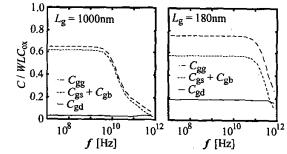

RF applications of MOSFETs with gate lengths  $(L_g)$ in the 100nm regime are realistic not only due to MOS-FET's low cost and high integration capabilities but mainly due to improved high frequency characteristics as shown in Fig. 1 [1]. For further improvement, it is desired that capacitances be reduced together with  $L_{g}$ . Among the gate capacitances, the  $C_{\rm gd}$  contribution becomes increasingly important with scaling, since  $C_{\rm gd}$  stays large in spite of the  $L_{\rm g}$  reduction as demonstrated in Fig. 2. This is mainly attributed to the overlap and fringing capacitance contributions [2]. An additional contribution was attributed to the charge associated with the channelside fringing field, later called the inner fringing capacitance. However, we have recognized that this contribution is negligibly small. For short-channel transistors, it has been shown that the velocity saturation affects the gate capacitances [3]. However, precise investigations are still missing.

In scaled MOSFETs, device characteristics are mostly determined by the field gradient near the drain, causing short-channel effects. This field is of course the origin of the velocity saturation. Working on measured  $C_{\rm gd}$  and 2D simulations of small-size MOSFETs, we have found that the field gradient along the channel itself is an increasingly important factor which determines the  $C_{\rm gd}$  value. Here we report an efficient surface-potential based MOSFET model of this effect for HiSIM [4]. In particular, the new  $C_{\rm gd}$  model allows an accurate reproduction of measured  $C_{\rm gd}$ - $L_{\rm g}$  characteristics for 100nm-scale MOSFETs with the pocket implant technology [5],[6]. Our in-

Fig. 1. Measured H-parameters  $(h_{21})$  as a function of frequency (f) for a pocket-implant technology. The cut-off frequency  $(f_c)$  reaches 100 Ghz for a 100nm gate length MOSFET.

Fig. 2. MEDICI simulation of gate capacitances as a function of frequency (f), where  $C_{\rm gg}{=}C_{\rm gs}{+}C_{\rm gb}{+}C_{\rm gd}$ .  $C_{\rm gd}$  remains significant at reduced  $L_{\rm g}$ .

vestigation also predicts a reduction of  $C_{\rm gd}$  with decreasing  $L_{\rm g}$  due to the steep potential gradient introduced by the pocket implantation.

## II. ANALYSIS OF 2D SIMULATION BY MEDICI

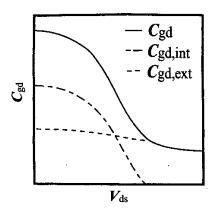

Generally,  $C_{\rm gd}$  consists of two components: the intrinsic  $(C_{\rm gd,int})$  and the extrinsic  $(C_{\rm gd,ext})$  components,

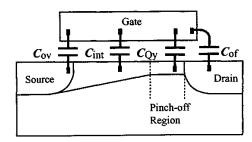

Fig. 3. Gate-drain capacitance components shown schematically.  $C_{\rm gd,ext}$  includes the overlap capacitance ( $C_{\rm ov}$ ) and the bias-independent outer-fringing capacitance ( $C_{\rm of}$ ).

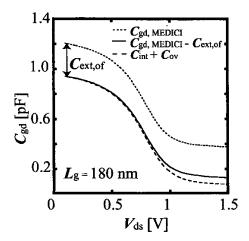

Fig. 4. Comparison of gate-drain capacitance calculated by MEDICI  $C_{\rm gd,MEDICI}$  and calculated by charge integration ( $C_{\rm int}+C_{\rm ov}$ ). The difference is visible in the saturation region owing to high-field gradient.  $C_{\rm of}$  is constant and bias-independent, and thus subtracted from  $C_{\rm gd,MEDICI}$ .

schematically shown in Fig. 3. The intrinsic component is due to the mobile and depletion charges within the channel, while the extrinsic components include the overlap  $(C_{\rm ov})$  and the outer-fringing  $(C_{\rm of})$  capacitances.  $C_{\rm ov}$  is bias-dependent and has been modeled separately [7]. Among the  $C_{\rm gd}$  components,  $C_{\rm of}$  is constant and bias-independent and thus can be neglected in the detailed simulation analysis. However, the sum of  $C_{\rm gd,int} + C_{\rm gd,ext}$  (=  $C_{\rm ov} + C_{\rm of}$ ) alone is not sufficient to reproduce the total  $C_{\rm gd}$ . The inclusion of an additional component coming from the charges induced by the field gradient is considered.

We have determined the field-gradient contribution to

Fig. 5. The new  $C_{\rm gd}$  model with  $C_{\rm Qy}$  added to the conventional components.

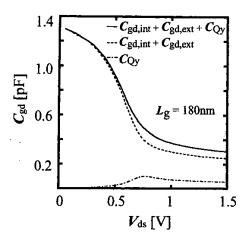

$C_{\rm gd}$  in the following way. First,  $C_{\rm gd}$  was simulated with the 2D device simulator MEDICI [8], which includes all inherent contributions. Then the intrinsic and extrinsic contributions to  $C_{\rm gd}$  were calculated by integrating the charges as provided by MEDICI along the vertical direction first, and then along the lateral direction bounded by  $L_{\rm g}$ . This integration thus includes all the bias-dependent components. A significant difference between these two  $C_{\rm gd}$  calculations was found. The difference as shown in Fig. 4 is visible in the saturation  $C_{\rm gd}$  which is explained by the lateral electric field  $(E_{\rm y})$  gradient along the channel. The space charge  $Q_{\rm y}$  caused by the electric field gradient is calculated following

$$Q_{y} = \epsilon_{Si} w \int x_{d}(y) \frac{dE_{y}(y)}{dy} dy$$

(1)

where w is the channel width,  $x_{\rm d}({\rm y})$  is the depletion width and y is along the channel direction. The capacitance  $C_{\rm Qy}$  due to this charge is given by  $C_{\rm Qy}{=}{\rm d}Q_{\rm y}/{\rm d}V$ , and is added to the conventional intrinsic and extrinsic components as shown in Fig. 5. The quantitative magnitude of  $C_{\rm Qy}$  for  $L_{\rm g}{=}180{\rm nm}$  is demonstrated in Fig 6. As expected, this new  $C_{\rm gd}$  component becomes important under the saturation region. More importantly in short-channel MOSFETs,  $E_{\rm y}$  becomes appreciable and thus influences stronger. It is therefore necessary to include this new component into the circuit simulation of small-size MOSFETs.

#### III. SURFACE-POTENTIAL BASED MODELING

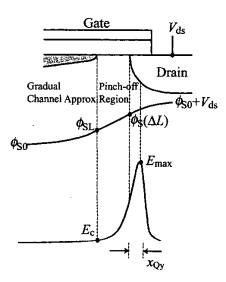

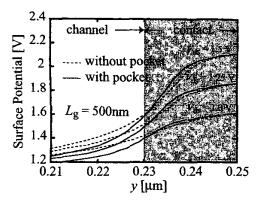

Since HiSIM is surface-potential based, having a quality-level comparable to a 2D device simulator, implementation of the proposed new  $C_{\rm gd}$  model is straightforward. HiSIM knows all the potential values necessary to describe the induced capacitance, especially near the drain junction where the maximum lateral field occurs. The surface-potential distribution as described by HiSIM is shown in Fig. 7. By applying the Gauss law in the region where the lateral field steeply increases [9],  $Q_{\rm y}$  is

Fig. 6.  $C_{\rm gd,int}+C_{\rm gd,ext}$  and  $C_{\rm Qy}$  contributions to the gatedrain capacitance as simulated in MEDICI.  $C_{\rm Qy}$  becomes significant in saturation  $C_{\rm gd}$ .

Fig. 7. Surface potential distribution of a MOSFET in saturation as modeled by HiSIM. Also depicted are the field points significant in  $C_{\rm gd}$  modeling.

expressed as

$$Q_{\rm y} = \epsilon_{\rm Si} w x_{\rm d} (E_{\rm max} - E_{\rm c}) \tag{2}$$

where

$$E_{\text{max}} = \frac{\phi_{\text{s0}} + V_{\text{ds}} - \phi_{\text{s}}(\Delta L)}{x_{\text{Qy}}}, \tag{3}$$

$\phi_{s0}+V_{ds}$  is the surface potential in the drain region,

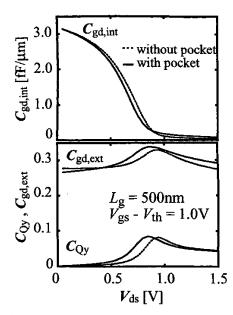

Fig. 8. Partitioned components of  $C_{\rm gd}$  for pocket and non-pocket cases. In  $C_{\rm gd,ext}$  the outer-fringing capacitance is excluded.

$\phi_{\rm s}(\Delta L)$  is the surface potential at the drain junction and  $E_{\rm c}$  is the electric field at the end of the gradual channel approximation. A parameter  $(x_{\rm Qy})$ , independent of  $L_{\rm g}$ , is introduced indicating the position of the maximum lateral field from the drain junction. The induced capacitance  $C_{\rm Qy}$  is then calculated as

$$C_{\mathrm{Qy}} = \epsilon_{\mathrm{Si}} w x_{\mathrm{d}} \left( \frac{\frac{\mathrm{d}\phi_{\mathrm{s0}}}{\mathrm{d}V_{\mathrm{ds}}} + 1 - \frac{\mathrm{d}\phi_{\mathrm{s}}(\Delta L)}{\mathrm{d}V_{\mathrm{ds}}}}{x_{\mathrm{Qy}}} - \frac{\mathrm{d}E_{\mathrm{c}}}{\mathrm{d}V_{\mathrm{ds}}} \right) \tag{4}$$

This induced capacitance is added to the conventional components as calculated by HiSIM.

### IV. MODELING RESULTS FOR A 100nm POCKET-IMPLANT TECHNOLOGY AND DISCUSSION

Fig. 8 compares MEDICI simulation results of with and without pocket implantation for the different  $C_{\rm gd}$  components. It is observed that the transition from the linear to the saturation region shifts to lower  $V_{\rm ds}$  for the pocket-implantation case. This shift, which is true to all the components, is explained by the steeper potential increase of the pocket implant case near and in the drain contact as shown in Fig. 9. To achieve the same amount of high field for inducing this transition, a lower  $V_{\rm ds}$  is thus sufficient for the pocket-implant case.

Fig. 9. Potential distribution for pocket and non-pocket cases. Pocket implantation results in steeper potential increase near the drain contact which extends into the overlap region.

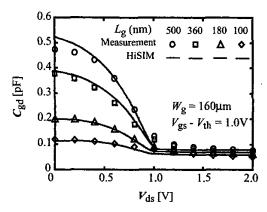

Fig. 10. HiSIM calculation for  $L_{\rm g}=500,\,360,\,180$  and 100nm pocket-implanted MOSFETs in comparison to measurements.

Fig. 10 shows measured  $L_{\rm g}$ -dependent  $C_{\rm gd}$ - $V_{\rm ds}$  characteristics for a 100nm pocket-implant technology. Two important features, occuring for reduced  $L_{\rm g}$ , are obvious:

- diminishing maximum at  $V_{\rm ds}{=}0$ , and

- reduction of the saturation  $C_{\rm gd}$ .

The physical reason for the diminishing maximum of  $C_{\rm gd}$  with smaller  $L_{\rm g}$  is the reduction of the relative size of the channel region in comparison to the pinch-off region, where  $Q_{\rm y}$  is the main cause of the  $C_{\rm gd}$  changes. At smaller  $L_{\rm g}$ , the capacitance flattens because the magnitude of the saturation  $C_{\rm gd}$  becomes comparable to that of the linear region. The physical reason for the  $C_{\rm gd}$  reduction in the saturation region with smaller  $L_{\rm g}$  is the shift of the beginning of the saturation region to lower  $V_{\rm ds}$  due to the high lateral electric field near the drain.

Fig. 10 also depicts calculated  $C_{\rm gd}$  by HiSIM using the new  $C_{\rm gd}$  model. Since HiSIM models all features of the pocket technology on a surface-potential basis, good re-

production is achieved without needing any  $L_{\rm g}$  dependent model parameters. Our results thus predict the positive effect of a reducing  $C_{\rm gd}$  for future MOSFET-generations, owing to the high field near the drain, which was previously considered to be only undesirable.

#### V. CONCLUSION

We have developed a new  $C_{\rm gd}$  model which includes the induced capacitance of the lateral field along the channel for small-size MOSFETs. The model, as implemented in HiSIM, achieves a good agreement with measured values down to  $L_{\rm g}{=}100{\rm nm}$ . The results promise reduced  $C_{\rm gd}$  for pocket-implanted MOSFETs which is desirable in RF applications.

#### REFERENCES

- H. Kawano, M. Nishizawa, S. Matsumoto, S. Mitani, M. Tanaka, N. Nakayama, H. Ueno, M. Miura-Mattausch, and H. J. Mattausch, "A Practical Small-Signal Equivalent Circuit Model for RF-MOSFETs Valid Up to the Cut-off Frequency," Proc. Int. Microwave Symposium, Vol. 3, pp. 2121-2124, 2002.

- [2] B. J. Sheu and P. K. Ko, "Measurement and Modeling of Short-Channel MOS Transistor Gate Capacitances," *IEEE J. Solid State Circuits*, SC22, pp. 464-472, June 1987.

- [3] H. Iwai, M. R. Pinto, C. S. Rafferty, J. E. Oristian, and R. W. Dutton, "Analysis of Velocity Saturation and Other Effects on Short-Channel MOS Transistor Capacitances," *IEEE Trans. CAD*, CAD-6, No. 2, pp. 173-184, 1987.

- [4] http://home.hiroshima-u.ac.jp/usdl/HiSIM.shtml

- [5] T. Hori, "A 0.1µm CMOS Technology with <u>Tilt-Implanted Punchthrough Stopper</u> (TIPS)," *IEDM Technical Digest*, pp. 75-78, 1994.

- [6] Y. Taur and E. J. Nowak, "CMOS Devices Below 0.1μm: How High Will Performance Go?" IEDM Technical Digest, pp. 215-218, 1997.

- [7] D. Navarro, K. Hisamitsu, T. Yamaoka, M. Tanaka, H. Kawano, H. Ueno, M. Miura-Mattausch, H. J. Mattausch, S. Kumashiro, T. Yamaguchi, K. Yamashita, and N. Nakayama, "Circuit-Simulation Model of MOSFET Gate-Drain Capacitance", submitted to IEICE for publication.

- [8] MEDICI User's Manual, Avant!.

- [9] Y. A. El-Mansy and A. R. Boothroyd, "A Simple Two-Dimensional Model of IGFET Operation in the Saturation Region," *IEEE Trans. Electron Devices*, Vol. ED-24, pp. 241-253, 1977.