# On the Optimal Shape and Location of Silicided Source and Drain Contacts

Phil Oldiges, Cheruvu Murthy, Xinlin Wang, Sam Fung, and Robert Purtell

IBM Semiconductor Research and Development Center (SRDC), Microelectronics Division, Hopewell Junction, NY 12533

E-mail: poldiges@us.ibm.com Phone: (845)892-2511 fax: (845)892-3039

Abstract- A detailed simulation and analysis of the source/drain resistance is performed. It is shown that the placement and depth of silicide regions can have a strong influence on the total source/drain resistance. Simulations further show that moving the silicided regions closer to the channel of a device will not necessarily decrease source/drain resistance, and may actually cause the resistance to increase. Lumped contact resistance, distributed resistance, Schottky contact models, and a new local distributed resistance model are compared.

#### I. INTRODUCTION

The importance of reducing parasitic source-drain resistance (Rsd) as devices are scaled down can not be overstated. The 2001 International Technology Roadmap for Semiconductors (ITRS) states that for 35 nm gate length high performance logic devices, the Rsd be  $140~\Omega$ - $\mu$ m and account for no more than 20% of the total device resistance [1]. End of the roadmap devices that exhibit ballistic transport are expected to have intrinsic device resistance of less than 50  $\Omega$ - $\mu$ m [2]. For those kinds of devices to operate effectively,

Rsd would need to be less than ~10  $\Omega$ - $\mu$ m, a value that is quite difficult to imagine using current technology. It is therefore important to be able to both qualitatively and quantitatively model the current flow in the source and drain regions. In this work we use doping profiles from process simulations and realistic depths and spacings from the gate edge for source-drain silicide regions coupled with a physical Schottky contact model to investigate single sided source-drain resistance. We vary the depth and location of the silicide region to understand how resistance will scale.

Section II discusses the device structure studied. Section III describes the models used and analyzes current flow. Section IV compares model results and describes a new local distributed contact resistance model. Conclusions are drawn in Section V.

#### II. DEVICE STRUCTURE

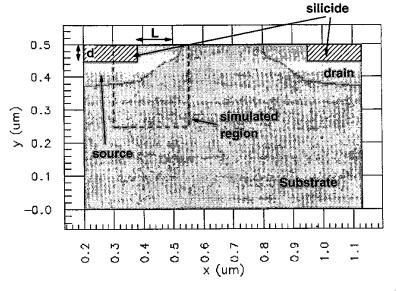

Figure 1 shows the device structure we consider. An IBM specific version of Tsuprem4 was used to simulate a prototype 150 nm nominal gate length process. Silicided source/drain contacts were defined at the end of the process simulation by etching the silicon to the desired shape and depositing a metal electrode. It was assumed that the doping profile was not changed by the silicidation process. Although the gate and spacer were simulated, they were removed at the end of the simulations since we concern ourselves here only with the intrinsic source-drain regions. A small area, zero  $\Omega$ - $\mu$ m ohmic contact was placed at the edge of the extension region. A silicided source was defined as a box-like contact region and parameterized by its depth, d, and distance from the edge of the gate to the silicide box, L. The full 2D device that was generated in the process simulations was truncated for device simulation since we are interested in the source-drain resistance. Fielday was used to perform the device simulations [3,4]. Physical modeling of the silicided source was performed utilizing the Schottky contact model in Fielday [5]. We varied the depth of the silicide region, d,

Fig. 1. Region of MOS device that is simulated. The gate stack is not shown and is not used in this study. The silicided regions are parameterized by their depth, d, and distance from the gate edge, L.

| Table 1. Simulated S/D resistance for various silicide shapes and con | tact |

|-----------------------------------------------------------------------|------|

| resistance models                                                     |      |

| d (nm) | L (nm) | R <sub>ohmic</sub> (Ω-μm) | R <sub>Schottky</sub> (Ω-μm) |

|--------|--------|---------------------------|------------------------------|

| 0      | 120    | 79.1                      | 93.5                         |

| 50     | 120    | 76.5                      | 151                          |

| 0      | 20     | 45.8                      | 75.5                         |

| 20     | 20     | 44.6                      | 163                          |

| 50     | 20     | 44.3                      | 355                          |

from 0 nm to 50 nm, which is typical for current technology [6,7]. The distance from silicide edge to gate, L, was varied from 20 nm to 150 nm. For the Schottky contact model, we assume a barrier height of 0.5 eV, which is approximately appropriate for cobalt silicide.

## III. OHMIC VS. SCHOTTKY CONTACT MODEL

We first assume that the silicide makes a perfect ohmic contact to the source with no additional lumped or distributed contact resistance. As the silicide moves closer to the extension, we might naively assume that the intrinsic source resistance would decrease. Table 1 shows that this is indeed the case for an ohmic contact. As we make the silicide thicker and thicker, the source resistance tends to decrease. Table 1 indicates the nearly opposite result when we use a more physical Schottky contact model. When the silicide depth increases, the intrinsic source resistance increases when

the Schottky contact model is used. This occurs because the doping concentration decreases as the silicide depth increases, thereby increasing the effective contact resistance. Similarly, as the silicide reaches into the extension region closer to the gate edge, the contact resistance increases because the doping concentration is lower in the extension than in the deep source.

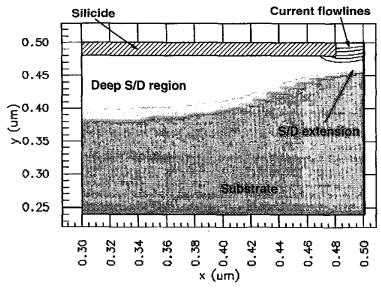

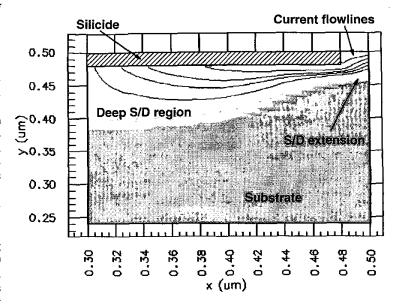

Figures 2 and 3 show how the current flows for the ohmic and Schottky contact cases. In

Figure 2, an ohmic contact shows that current flows practically horizontally between the edge of the silicide and the extension. For the Schottky contact in Figure 3, because the silicide contacts a low doping concentration region in the extension, the contact resistance is high so the current is forced to flow through the deep source and into the bottom of the silicide. From Table 1 and Figures 2 and 3, we find that single sided Rsd can easily *increase* by more than  $100 \ \Omega$ - $\mu$ m by *decreasing* the silicide-gate edge spacing.

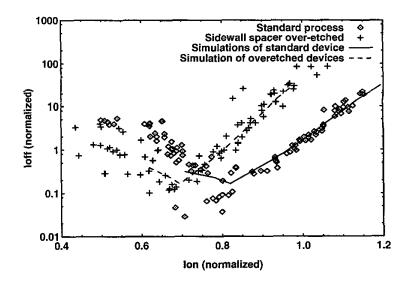

Figure 4 shows this effect on devices. A process was run that reduced the spacer width after the source and drain implants. This effectively caused the source and drain silicide regions to be formed closer to the gate edge. Compared to the standard devices, the devices with this longer silicide region were found to have ~20% lower on currents. Simulations of these two device splits indicated that the single sided source-drain resistance increase by ~125  $\Omega$ - $\mu$ m for this on current reduction.

Fig. 2. Current flow lines for a silicided S/D region assuming an ohmic contact. We can see that the current flows mostly out of the edge of the silicide into the extension region.

## IV. New Local Distributed Contact Model

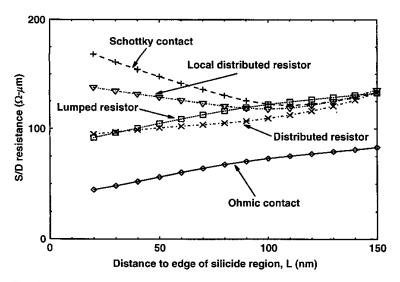

Various models for contact resistance have been proposed and used in device simulators. In the previous section we discussed the simple ohmic contact model and a physics-based Schottky model. For the ohmic contact, lumped resistive elements are easily implemented. Another commonly used model is a distributed contact resistance model where the contact to the semiconductor is considered ohmic but resistance is distributed over all of the contact nodes. In Figure 5, we compare simulations of source resistance using various contact models.

For a given silicide depth, we can vary the distance between the silicide edge and gate edge (L). Figure 5 shows results of that simulation for a silicide depth, d, of 20 nm. A canonical ohmic contact model with no lumped resistance, indicated by the label "Ohmic contact", shows that as

the spacing L increases, the source resistance also increases. For a spacing of 150 nm, the source resistance is ~80  $\Omega$ - $\mu$ m.

The Schottky contact case shows an interesting trend. For small values of L, the resistance is quite large. For large values of L, the resistance increases with L. We find that there is a minimum value for the source resistance. This minimum occurs where the deep S/D implant begins to tail off laterally into the extension region. For the device studied here, the doping concentration in the extension is ~2X smaller than in the deep source.

We can now compare various resistance models to the Schottky contact model. In order to match the ohmic contact model to the Schottky model for a silicide spacing of 150nm, we add a lumped resistor of 50  $\Omega$ - $\mu$ m. Figure 5 shows this result indicated by "Lumped resistor". This model shows the same shape as the ohmic model but simply shifted upwards on the plot.

A canonical distributed contact resistance model, indicated in Figure 5 by the label "Distributed resistor", was also used, assuming that the distributed contact resistance is  $3.3~\Omega$ - $\mu$ m<sup>2</sup>. Using this model we see some difference between the lumped resistor model, but it does not match the Schottky contact model when the spacing is reduced to less than 100nm.

A new model for distributed contact resistance model, indicated by "Local distributed resistor" in Figure 5, shows a similar trend as the Schottky model. This new model takes into account the barrier height and local doping concentration along the contact. It does so by placing small resistive elements along the contact whose values are dependent upon the doping concentration at each node along the contact. This model was calibrated using Fielday's Schottky contact model on uniformly doped regions. There is a quantitative difference between the new local distributed contact model and the Schottky model which is attributed to differences in the tunneling barrier for a retrograde doping profile. In spite of this difference, both models show a minimum in the source resistance indicating that an optimal shape and location for silicide can

Fig. 3. Current flow lines for the same structure as shown in Figure 2 but using a Schottky contact model. Because the silicide reaches into the lower concentration extension region causing a large contact resistance, the current is forced to flow deeper into the S/D region and into the area of lower contact resistance.

Fig. 4. Measurements and simulations of Ion/Ioff characteristics for devices built in a standard process and one with the sidewall spacer over-etched. The S/D resistance was increased by approximately 125  $\Omega$ - $\mu$ m due to this over-etch.

be determined when knowledge of the source-drain doping is well characterized.

#### V. CONCLUSIONS

Simulations of intrinsic resistance of source and drain diffusion regions including contact resistance at the silicide boundary were performed. Unlike earlier studies that assumed a uniform distributed contact resistance for the contact, this work showed that a Schottky contact model is needed to understand the current flow. Alternatively, a new model for distributed contact resistance compares well to the Schottky contact model. When the correct physics is included in the simulations, earlier assumptions about how resistance scales are shown to be invalid. Finally, it was shown that there can be an optimal silicide depth and location for source and drain regions.

## ACKNOWLEDGMENT

The authors wish to thank R. Rengarajan for useful discussions.

## REFERENCES

[1] International Technology Roadmap for Semiconductors, edited by Semiconductor Industry Association, URL:

- http://public.itrs.net/Files/2001ITRS/PIDS.pdf, 2001.

- [2] Farzin Assad, Zhibin Ren, Dragica Vasileska, Supriyo Datta, and Mark Lundstrom, "On the performance limits for Si MOSFET's: A theoretical study", *IEEE Trans. Electr. Dev.*, vol. 47, no. 1, p. 232, 2000.

p. 7,

- [3] E.M. Buturla, P.E. Cottrell, B.M. Grossman, and K.A. Salsburg, "Finite-element analysis of semiconductor devices: the FIELDAY program," *IBM J. Res. Develop.*, vol. 25, p. 218, 1981.

- [4] MeiKei Ieong, Ronald Logan, and James Slinkman, "Efficient quantum correction for multi-dimensional CMOS simulations", Proc. SISPAD, p. 129, 1998.

- [5] MeiKei Ieong, Paul M. Solomon, S.E. Laux, Hon-Sum Philip Wong, and Dureseti Chidambarrao, "Comparison of raised and Schottky source/drain MOSFETs using a novel tunneling contact model", *IEDM Tech. Dig.*, p. 733, 1998.

- [6] Pushkar Apte, Suresh Potla, Douglas A. Prinslow, Gordon Pollack, David Scott, and Kody Varahramyan, "An integrated approach for accurate simulations and modeling of the silicide-source/drain structure and the silicide-diffusion contact resistance", IEDM Tech. Dig., p. 729, 1998.

- [7] Bing-Yue Tsui, Ming-Da Wu, and Tian-Choy Gan, "Impact of silicide formation on the resistance of common source/drain region", IEEE Electr. Dev. Lett., vol. 22, no. 10, 2001.

Fig. 5. Calculations of S/D resistance show large differences based on the model used. Simple ohmic contact models show that moving the contact closer to the extension would decrease S/D resistance, but a physics-based Schottky contact model indicates that there is an optimal location for the silicide region.