# Simulation of DGSOI MOSFETs with a Schrödinger-Poisson Based Mobility Model

Andreas Schenk<sup>1</sup> and Andreas Wettstein<sup>2</sup>

<sup>1</sup> Integrated Systems Laboratory, Swiss Fed. Inst. of Technology, Gloriastr. 35, CH-8092 Zürich, Switzerland e-mail: schenk@iis.ee.ethz.ch, Tel: +41 1 263 6689, Fax +41 1 263 1194

<sup>2</sup> ISE Integrated Systems Engineering AG, Balgriststr. 102, CH-8008 Zürich, Switzerland

#### I. INTRODUCTION

Ultra-thin DGSOI transistors are considered as one of the most promising devices for future VLSI. Besides expected improvements in the sub-threshold behavior, a theoretical enhancement of the channel mobility was found by some authors. Here, we apply a quantum-mechanical mobility model, based on an integrated Schrödinger/Poisson solver, to double-gate SOI MOSFETs with a range of silicon slab thickness  $t_{\rm Si}$  and buried-oxide thickness  $t_{\rm box}$ . The main finding is that the theoretical enhancement of effective mobility and on-current at  $t_{\rm Si}\approx 10\,{\rm nm}$  is bound to comparable thicknesses of buried and front oxides. If  $t_{\rm box}\approx 100\times t_{\rm ox}$ , as e.g. in the case of SIMOX wafers, the volume-inversion related increase of the mobility completely vanishes.

### II. TRANSPORT AND MOBILITY MODEL

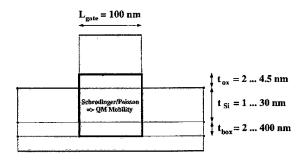

The density-gradient model [1], [2] is used in the entire MOSFET which automatically includes the gate quantum-depletion effect [3]. A domain under the front gate covering front oxide, buried oxide, and lowly p-doped (10<sup>15</sup> cm<sup>-3</sup>) silicon slab (see Fig. 1), is subject to the

Fig. 1. DGSOI MOSFET cross section with Schrödinger/Poisson window.

self-consistent Schrödinger/Poisson solver which yields all information (eigenstates, wave functions) needed for the computation of the channel mobility. This 'hybrid' approach has proven to improve convergence at larger drain currents with only little loss of accuracy in the electron density. Details of the density gradient model in the device simulator DESSIS\_ISE [4] are described in [1], details of the mobility model can be found in [2]. The

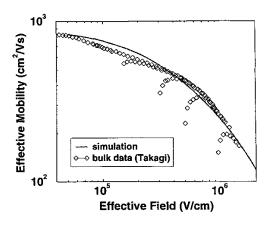

Fig. 2. Measured [5] versus simulated effective mobility in bulk silicon. Parameters:  $t_{\rm ox}=2\,{\rm nm},\,N_{\rm A}=10^{15}\,{\rm cm}^{-3}$ , other parameters as given in Table I.

TABLE I Parameters for the electron mobility.  $D_{\mathrm{int,f}}$  and  $D_{\mathrm{int,g}}$  are the inter-valley deformation potential constants for f- and g-type scattering, respectively.

| Quantity               | Value | Unit              |

|------------------------|-------|-------------------|

| $\Delta_{1,2}$         | 0.32  | nm                |

|                        | 1.5   |                   |

| $L_{\mathtt{corr}1,2}$ |       | nm                |

| $\alpha$               | 0.5   | $(eV)^{-1}$       |

| $D_{ m int,g}$         | 1.0   | ${ m GeV/cm}$     |

| $D_{ m int,f}$         | 0.2   | ${ m GeV/cm}$     |

| $D_{ m ac}/c_{ m l}$   | 12    | $\mu { m eVs/cm}$ |

| $\hbar\omega_{ u u'}$  | · 60  | meV               |

latter makes use of the relaxation time approximation for acoustic-phonon, inter-valley-phonon, and interface-roughness (IR) scattering, but neglects Coulomb scattering, which is negligible in the channel (we focus on the on-state), but is taken into account elsewhere by a conventional default model. Screening of IR scattering is obtained self-consistently by an inner iteration of the system's first-order response to geometrical fluctuations of the interfaces. The number of subbands is restricted to 11 in order to allow for routinely simulations. Bulk coupling constants are used which reproduce the universal mobility curve of bulk MOSFETs (Fig. 2). The parameters used in this paper are summarized in Table I. We assume equal IR amplitudes  $\Delta_1 = \Delta_2$  at both interfaces and neglect

the interdependence of upper and lower IR scattering. In particular, the perturbation of the electrostatic potential caused by the displacement of the interfaces is computed separately for the upper and lower interface. The perturbation is assumed to vanish at the top gate and at  $z = \infty$  for the top interface, and at the lower gate and  $z = -\infty$  for the bottom interface. The modification of the electron density induced by the displacement of the interfaces and the modification of the electrostatic potential is neglected, that is, screening is disregarded. The fit in Fig. 2 was obtained in this way. As shown by Gamiz et al. in Ref. [6] for a simplified IR perturbation Hamiltonian, the modification of the latter due to the presence of the buried interface leads to an increase of the effective mobility in the IR-dominated range compared to the corresponding Hamiltonian used in bulk situations. As in their work the thickness of the buried oxide was large, such a modification will be different for symmetrical DG-SOIs. In the light of the somewhat questionable physical meaning of the commonly used IR perturbation operator and because there are 4 adjustable IR parameters, we did not attempt to follow the line of Ref. [6].

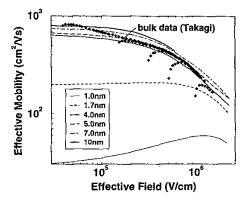

Fig. 3. Effective mobility versus effective field for  $t_{ox} = t_{box} = 2 \text{ nm}$ , and various  $t_{Si}$ . Bulk data [5] are shown for comparison.

The remaining symbols in Table I have the following meaning:  $L_{\rm corr\,1,2}$  are the auto-covariance lengths of the roughness fluctuations (assumed to be equal for both interfaces),  $\alpha$  is the nonparabolicity parameter,  $D_{\rm int}$  and  $D_{\rm ac}$  are the inter-valley and acoustic deformation potential constants, respectively,  $c_{\rm l}$  is the longitudinal sound velocity, and  $\hbar\omega_{\nu\nu'}$  is the phonon energy involved in intervalley scattering (Einstein approximation  $\hbar\omega_{\nu\nu'}=\hbar\omega_0$  used). The elastic approximation for the acoustic-phonon scattering rate and the equipartition approximation for the acoustic-phonon occupation probabilities have been applied, i.e.  $f_{\rm B}\left[\vec{q}\right]\approx k_BT_L/\hbar c_{\rm l}\left|\vec{q}\right|$ . Effective mobilities and effective electric fields are computed in analogy to bulk MOSFETs:

$$\mu_{\mathrm{eff}} = rac{\int dz \, \mu \left[z

ight] n \left[z

ight]}{\int dz \, n \left[z

ight]} \; ,$$

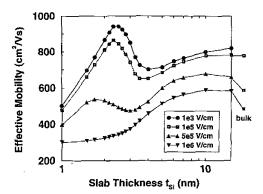

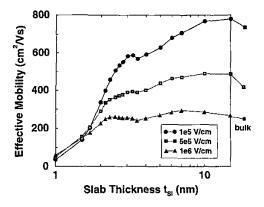

Fig. 4. Phonon-limited effective mobility versus SOI thickness for  $t_{\rm ox}=t_{\rm box}=2\,{\rm nm}$ , and various  $E_{\rm eff}$ . IR scattering was switched off.

$$E_{ ext{eff}} = rac{\int dz \; |\hat{z}\cdotec{E}\left[z

ight]| \, n\left[z

ight]}{\int dz \, n\left[z

ight]} \; ,$$

where  $\hat{z}$  denotes the unit normal vector along quantization direction z, and the interface positions are chosen as integration limits.

#### III. SIMULATION RESULTS

Fig. 3 shows  $\mu_{\rm eff}$  versus  $E_{\rm eff}$  for the symmetrical DG-SOI  $(t_{ox} = t_{box} = 2 \text{ nm})$ . In ultra-thin Si films with  $t_{\rm Si}$  < 4nm the mobility is suppressed due to geometrical confinement. An enhancement w.r.t. to the bulk curve is observed at intermediate and strong fields around  $t_{\rm Si} \approx 10\,{\rm nm}$  (compare Fig 2). The phonon-limited effective mobility as function of  $t_{Si}$  shown in Fig. 4 serves to explain the behavior in the different  $t_{Si}$ -regions in case of the symmetrical DGSOI. The phonon-limited bulk values are reached for  $t_{Si} > 15 \,\mathrm{nm}$ , when the interaction between upper and lower channel gradually disappears due to the growing potential barrier that separates the two inversion layers. The broad maxima around  $t_{\rm Si} \approx 10\,{\rm nm}$  are caused by the so-called volume inversion. As extensively discussed in Refs. [7], [8], in this region the communication between the two channels is associated with a reduction of the form factors

$$lpha_{N'N} = \int dz \, \left| \Psi_{N'} \left[ z \right] \right|^2 \left| \Psi_{N} \left[ z \right] \right|^2$$

$(\Psi_N = \text{envelope of the electron wave function in quantization direction)}$  and, therefore, leads to an enhancement of the mobility compared to the corresponding bulk MOSFET. The latter was obtained from the DGSOI by removing the buried oxide and changing the  $n^+$  backgate into a p-type substrate. Decreasing the Si thickness, the region governed by geometrical confinement starts at  $t_{\rm Si} \approx 4\,\mathrm{nm}$ . At low and intermediate effective fields, the mobility first sharply increases, since the average conductivity mass is reduced by the stronger population of the lowest non-primed ladder. With further reduction of  $t_{\rm Si}$  the growth of the form factors dominates over sub-band

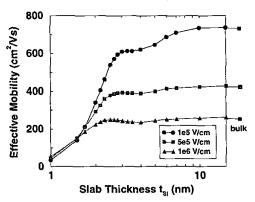

splitting and population effects and the mobility sharply drops. However, the range  $t_{\rm Si} < 4\,\mathrm{nm}$  is of academic interest only, because it is (currently) inaccessible by technology, and because IR scattering drops the mobility below its bulk values in this region. This is demonstrated in Fig. 5, where IR scattering now is included. As can be

Fig. 5. Effective mobility with IR scattering versus SOI thickness for  $t_{ox} = t_{box} = 2 \text{ nm}$ , and various  $E_{eff}$ .

seen, the mobility enhancement around  $t_{\rm Si}=10\,{\rm nm}$  has survived, although reduced in size and at a much lower mobility level. These changes obviously depend on the choice of the IR parameters.

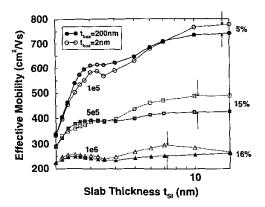

For the mobility enhancement it is essential that two equally filled channels can form. This is impossible in the more realistic case of a thick buried oxide. The results in Fig. 6 for  $t_{\rm box}=200\,{\rm nm}$  show that the mobility enhancement vanishes. This case is almost identical to single-gate SOI MOSFETs, where practically no mobility enhancement was found [8].

Fig. 7 compares the symmetrical with the asymmetrical device. For our choice of  $\Delta_2$  and  $L_{\rm corr\,2}$ , the difference amounts to 6% at  $E_{\rm eff}=1\times10^5\,{\rm V/cm}$  and to 15%–16% under strong inversion. These numbers also roughly represent the effect in comparison to the bulk MOSFET.

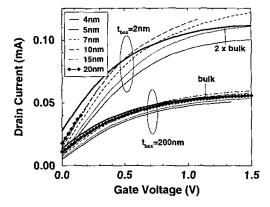

The transfer characteristics in Fig. 8 confirm these re-

Fig. 6. Effective mobility with IR scattering versus SOI thickness for  $t_{\rm ox}=2\,{\rm nm},\,t_{\rm box}=200\,{\rm nm},$  and various  $E_{\rm eff}$ .

Fig. 7. Effective mobility with IR scattering versus SOI thickness for  $t_{\rm ox}=2\,{\rm nm}$  and various  $E_{\rm eff}$  and  $t_{\rm box}$ .

Fig. 8. Transfer characteristics at  $V_{DS} = 1 \text{ mV}$  for various  $t_{Si}$ .

sults. In the symmetrical case the on-current exceeds two times the current of a bulk MOSFET (two parallel channels!). At  $V_{\rm GS}=1\,\rm V$  a 8% enhancement on top of that is observed for the 10 nm SOI candidate. However, in the case of  $t_{\rm box}=200\,\rm nm$  there is only one channel left, and due to the absence of volume inversion the mobility can only gradually approach the bulk value, but not exceed it.

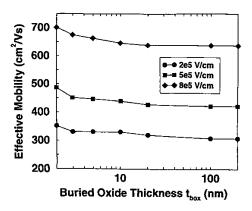

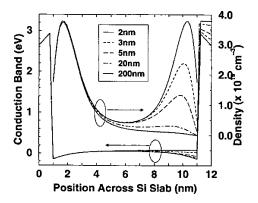

In order to demonstrate the loss of volume inversion with growing buried oxide, we plotted the effective mobility as a function of  $t_{\rm box}$  in Fig. 9. An increase of  $t_{\rm box}$  by a few nm is sufficient to halve the enhancement. Fig. 10 explains the situation in terms of band edge and density. The density in the upper channel is almost unaffected by an increase of  $t_{\rm box}$ , whereas the lower channel vanishes.

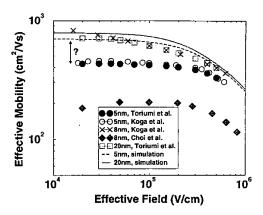

A comparison with (rare) experimental data [9]–[11] is shown in Fig. 11. For these simulations,  $t_{\rm ox}$  and  $t_{\rm box}$  were adapted to the published values. Most striking is the discrepancy for the 5 nm SOI (700 cm<sup>2</sup>/Vs simulated versus 420 cm<sup>2</sup>/Vs measured), since one would expect the mobility to be phonon-limited in this range. The open circles are very recent data from a sample with 'poor' buried interface [11] (measured density of interface

Fig. 9. Decrease of the effective mobility towards its bulk values with increasing  $t_{\rm box}$  for various  $E_{\rm eff}$  ( $t_{\rm Si}=10\,{\rm nm},\,t_{\rm ox}=2\,{\rm nm}$ ).

Fig. 10. Conduction band profile (left) and electron density (right) across the Si slab for various  $t_{\rm box}$  ( $t_{\rm Si}=10\,{\rm nm},\,t_{\rm ox}=2\,{\rm nm},\,V_{\rm GS}=1\,{\rm V}$ ).

traps  $D_{\rm it}=6\times10^{11}\,{\rm cm^{-2}eV^{-1}}$ ). For comparison, the same group measured a sample with  $t_{\rm Si}=8\,{\rm nm}$  (crosses), where the buried interface had a much higher quality ( $D_{\rm it}=4\times10^{10}\,{\rm cm^{-2}eV^{-1}}$ ). For the same  $t_{\rm Si}$ , older data [10] are significantly lower (diamonds). This shows the dramatic influence of the quality of the buried interface on the effective mobility. Koga et al. [11] attributed the mobility degradation in case of the 'poor' buried interface to Coulomb scattering at charged interface states.

## IV. Conclusion

A quantum-mechanical mobility model based on a 1D Schrödinger-Poisson solver can be routinely used with the device simulator DESSIS\_ISE. Convergence is improved by a hybrid technique, where the whole device is simulated with the density-gradient model, and only the channel mobility is computed with the information from the Schrödinger-Poisson window. We showed that the volume-inversion related enhancement of  $\mu_{\rm eff}$  for  $t_{\rm Si} \approx 10$  nm is bound to symmetrical DGSOIs. Thick buried oxides, as present in todays SIMOX technology, prevent the

Fig. 11. Comparison with experimental data. Parameters:  $\Delta_1 = \Delta_2 = 0.32 \, \text{nm}$ .

inversion of the buried channel and limit  $\mu_{\rm eff}$  to the bulk value.

#### REFERENCES

- O. Penzin A. Wettstein and E. Lyumkis. Integration of the density gradient model into a general purpose device simulator. In press. VLSI Design, 2002.

- [2] Andreas Wettstein. Quantum Effects in MOS Devices, volume 94 of Series in Microelectronics. Hartung-Gorre, 2000.

- [3] Andreas Schenk. Physical modeling of deep-submicron devices. In Proc. 31th ESSDERC'01, pages 9-16, 2001.

- [4] ISE Integrated Systems Engineering AG. DESSIS 8.0 reference manual, 2002.

- [5] Shin-ichi Takagi, Akira Toriumi, Masao Iwase, and Hiroyuki Tango. On the universality of inversion layer mobility in Si MOSFET's: Part I-Effects of substrate impurity concentration. IEEE Trans. Electron Devices, 41(12):2357-2362, December 1994.

- [6] F. Gámiz, J. B. Roldán, J. A. López-Villanueva, Pedro Cartujo-Cassinello, and J. E. Carceller. Surface roughness at the Si-SiO<sub>2</sub> interfaces in fully depleted silicon-on-insulator inversion layers. J. Appl. Phys., 86(12):6854-6863, December 1999

- [7] Masanari Shoji and Seiji Horiguchi. Electronic structures and phonon-limited electron mobility of double-gate siliconon-insulator Si inversion layers. J. Appl. Phys., 85(5):2722– 2731, March 1999.

- [8] F. Gamiz and M. V. Fischetti. Monte carlo simulation of double-gate silicon-on-insulator inversion layers: The role of volume inversion. J. Appl. Phys., 89(10):5478-5487, 2001.

- [9] A. Toriumi, J. Koga, H. Satake, and A. Ohata. Performance and reliability concerns of ultra-thin SOI and ultra-thin gate oxide MOSFETs. In *IEDM*, pages 847-814. IEEE, 1995.

- [10] J.-H. Choi, Y.-J. Park, and H.-S. Min. Electron mobility behavior in extremely thin SOI MOSFETs. IEEE El. Dev. Lett., 16, 1995.

- [11] Junji Koga, Shin-ichi Takagi, and Akira Toriumi. Influences of buried-oxide interface on inversion-layer mobility in ultra-thin SOI MOSFETs. *IEEE Trans. Electron Devices*, 49(6):1042-1048, June 2002.