# Quantum-Mechanical Correction to the Threshold Voltage of Deep-Submicron n-Channel MOSFET's

Maarten J. van Dort and Pierre H. Woerlee Philips Research Laboratories, P.O. Box 80.000, 5600 JA Eindhoven, The Netherlands

#### Abstract

The implications of high channel doping for the threshold voltage are discussed. Comparison of theory with experimental MOS devices of various generations show that quantum-mechanical effects are not to be neglected for deep-submicron MOSFET's. A simple analytical expression to account for these effects is proposed.

#### 1 Introduction

Device simulators treat the MOSFET in a classical way in the sense that only the Poisson and the continuity equations are solved. Effects arising from the quantum nature of the 2-D electron gas are therefore either completely ignored or enter the equations indirectly through the modeling of, for instance, the carrier mobility. Usually this approach is adequate, and there is no need for a self-consistent treatment of the problem which would require the solution of the Schrödinger equation.

At the onset of strong inversion the channel area is depleted causing a potential well perpendicular to the Si-SiO<sub>2</sub> interface to which the electrons in the inversion layer are confined. Electron motion in this direction is therefore quantized. As MOSFET's are scaled down to deep-submicron dimensions high levels of channel doping are needed to suppress punch-through currents. As a consequence, the potential well to which the electrons are confined becomes steeper and deeper. Quantum behavior is therefore expected to become more important for these MOSFET's. In this paper we will investigate the consequences of quantum-mechanical treatment of the problem for the long-channel threshold voltage.

# 2 Experimental

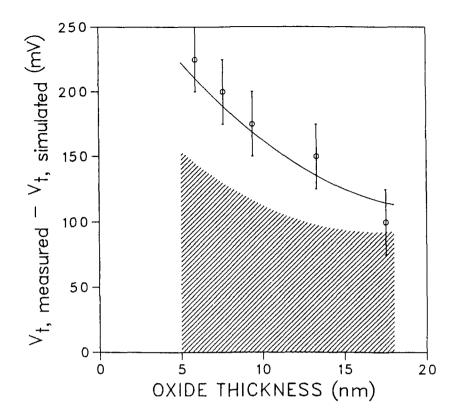

The MOS devices investigated in this report were scaled according to the quasi-constant-voltage approach [1], and were designed for nominal polysilicon gate lengths of 0.7, 0.5, 0.35, 0.25 and 0.15  $\mu$ m, respectively (See also Table 1). The threshold voltage was determined from  $8\times8-\mu\text{m}^2$  devices and is here defined as the gate voltage at which a drain current of 100 nA flows ( $V_{DS}$ = 0.1 V). We have also simulated the threshold voltages using the device simulator MINIMOS-4. Significant deviations exist between simulations and measurements. The difference between the simulated and measured threshold voltage is plotted in Fig. 1 versus the oxide thickness. We have verified that this difference can not be explained by trivial causes like deviations in the channel profile (measured with SIMS), the oxide thickness (determined from a  $200\times200-\mu\text{m}^2$  MOS capacitance in accumulation), oxide charges (below the detection limit of  $\sim10^9\text{cm}^{-2}$ ) or the existence of a depletion layer inside the polysilicon gate (can be determined from the MOS

| $\begin{array}{c} \text{design rule} \\ (\mu \text{m}) \end{array}$ | oxide thickness<br>(nm) | junction depth $(\mu \mathrm{m})$ | $< N_A > (cm^{-3})$  |

|---------------------------------------------------------------------|-------------------------|-----------------------------------|----------------------|

| 0.70                                                                | 17.5                    | 0.30                              | $0.7 \times 10^{17}$ |

| 0.50                                                                | 13.3                    | 0.23                              | $1.0\times10^{17}$   |

| 0.35                                                                | 9.4                     | 0.16                              | $1.5\times10^{17}$   |

| 0.25                                                                | 7.6                     | 0.12                              | $2.5\times10^{17}$   |

| 0.15                                                                | 5.9                     | 0.12                              | $3.5\times10^{17}$   |

Table 1: Devices used in the experiments

capacitance in the presence of an inversion layer). It should be emphasized that each point in Fig. 1 corresponds to a different MOS generation. A possible explanation will be presented below.

## 3 Theory

A full self-consistent quantum-mechanical treatment as a function of the gate voltage is extremely difficult and is only possible by numerical means. We can however solve the problem if we restrict ourselves to the state of weak inversion where the depletion layer already exists and the contribution of the minority carriers to the potential is negligible. The wave function of a long-channel MOSFET is  $\Psi = \Phi(z) \exp{(i\vec{k}\vec{r})}$  with  $\vec{k}$  in the (x,y)-plane. The coupled system of Poisson and Schrödinger equations is

$$\frac{\hbar^2}{2m^*} \frac{d^2}{dz^2} \Phi(z) + (E_n - V(z)) \Phi(z) = 0$$

(1)

$$\frac{d^2}{dz^2}V(z) = \frac{q}{\varepsilon_{\rm Si}}\rho(z) \approx \frac{q}{\varepsilon_{\rm Si}}N_A. \tag{2}$$

The channel doping  $N_A$  is taken to be homogeneous. If we further assume that the width of the inversion layer is small compared to the width of the depletion layer, we may linearize the potential and have

$$V(z) = q\mathcal{E}z. \tag{3}$$

Here,  $\mathcal{E}$  is the electric field (assumed constant) due to the charge in the depletion layer. The Schrödinger equation can be solved [2] and the solution consists of Airy functions with energy levels given by

$$E_n \approx \left(\frac{\hbar^2}{2m^*}\right)^{1/3} \left[\frac{3}{2}\pi q \mathcal{E}(n+\frac{3}{4})\right]^{2/3} \tag{4}$$

The average distance to the interface in sublevel n is found to be

$$\langle z_n \rangle = \frac{2E_n}{3q\mathcal{E}}. (5)$$

Figure 1: Difference between simulated and measured threshold voltages for various MOS generations. The open circles denote the measurements, the solid line is calculated with Eq. 9.

The average distance  $\langle z^{\rm QM} \rangle$  to the interface can be calculated if the occupation of the different sublevels is taken into account. For the conventional case we find  $\langle z^{\rm CONV} \rangle = kT/q\mathcal{E}$ . The total number of free carriers, N, can be calculated and is equal to [3]

$$N = \frac{m^* kT}{\pi \hbar^2} \sum_{n} \ln \left[ 1 + \exp\{(E_F - E_n)/kT\} \right], \tag{6}$$

where  $E_F$  is the position of the Fermi level. Although the summation runs in principle over all sublevels n, it should be mentioned that at high levels of channel doping the splitting between the energy levels is large compared to kT/q and only very few levels are actually occupied.

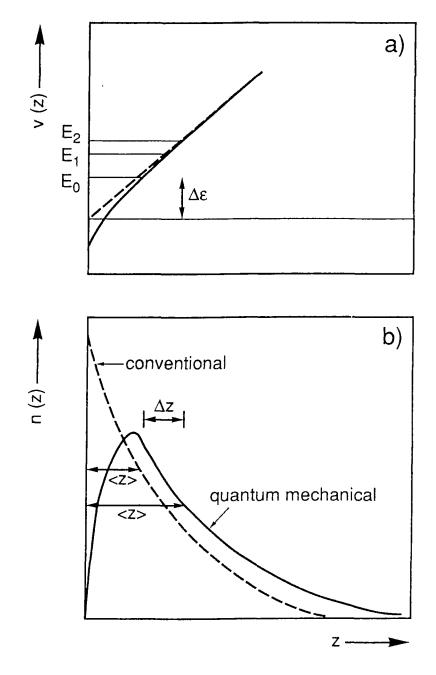

The quantum-mechanical solution differs in several manners from the conventional solution (see Fig. 2). First, the conventional solution consists of a continuum of energy levels starting at the bottom of the conduction band, while the energy spectrum of the quantum-mechanical solution consists of a discrete set of energy levels. The first allowed energy level,  $E_0$ , does not coincide any more with the bottom of the conduction band  $E_c$ . Second, the shape of the minority carrier density in the state of inversion differs for the two solutions. In the classical picture the carrier concentration reaches its maximum at the Si-SiO<sub>2</sub> interface. The quantum solution, on the other hand, shows a carrier concentration which is zero at the interface and an average distance to the interface larger than in the conventional calculations.

In order to establish the influence of both effects on the long-channel threshold voltage of a MOSFET, we will now focus on the surface potential needed to create the state of inversion.

Figure 2:

(a) Schematic representation of the potential in strong inversion. At the onset of inversion the potential reduces to a triangular shape (dashed line).

(b) Electron density versus distance.

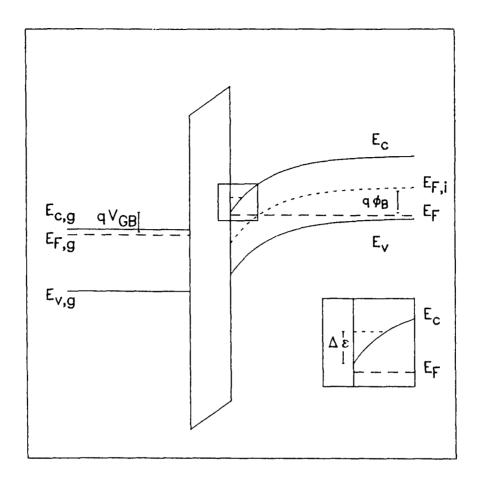

Figure 3: Band diagram for an  $n^+$  polysilicon gate on a p-type substrate. The part near the interface is shown in more detail in the inset.

(i) From the expression for the total number of free carriers (Eq. 6), it is clear that the position of the Fermi level is measured from the energy levels  $E_n$  instead of from the bottom of the conduction band. This involves an extra band bending  $\Delta\Psi_S$  of at least  $E_0/q$  ( $E_c=0$ , see also Fig. 3). (ii) The effects of the different shape of the electron density n(z) are more difficult to treat. Compared to the conventional calculations, the average distance to the interface is increased by an amount  $\Delta z = \langle z^{\rm QM} \rangle - \langle z^{\rm CONV} \rangle$  (Fig. 2b) [4]. We can use the expression for the potential (Eq. 3) to calculate the additional band bending needed to account for this effect. We find  $\Delta\Psi_S = \mathcal{E}\Delta z$ , implying an increase of the depletion width equal to  $\Delta z$ . (iii) Finally, the MOS capacitance in the presence of an inversion layer is slightly modified and is equal to

$$C_{\rm ox} = \varepsilon_{\rm ox}/t_{\rm eff},$$

(7)

with  $t_{\rm eff} = t_{\rm ox} + (\varepsilon_{\rm ox}/\varepsilon_{\rm Si})\Delta z$ .

We can now calculate the quantum-mechanical threshold voltage by substituting

$$\Psi_S = \Psi_S^{\text{CONV}} + \Delta \Psi_S. \tag{8}$$

with  $\Delta\Psi_S=E_0/q+\mathcal{E}\Delta z$  into the standard formula for the long-channel threshold voltage. We

find

$$V_t \approx V_t^{\text{CONV}} + \Delta \Psi_S \left( 1 + \frac{1}{2C_{\text{ox}}} \sqrt{\frac{\varepsilon_{\text{Si}} q < N_A >}{\phi_B}} \right).$$

(9)

A simple expression for  $\Delta z$  can be obtained if we assume that only the first allowed energy level is occupied, i.e.,

$\Delta z \approx \frac{2E_0}{3a\mathcal{E}} - \frac{kT}{a\mathcal{E}}.\tag{10}$

In realistic devices the channel profile is inhomogeneous, which makes it somewhat more difficult to calculate the exact position of the energy levels  $E_n$ . However, the dependence of  $E_n$  on the acceptor concentration does not change. We shall therefore assume that  $E_0 = q\alpha < N_A >^{1/3}$ , with  $< N_A >$  the acceptor concentration averaged over the depletion layer and  $\alpha$  a proportionality factor. Combining the two contributions to  $\Delta \Psi_S$ , we finally find

$$\Delta \Psi_{S} = \frac{5}{3}\alpha < N_{A} > ^{1/3} - \frac{kT}{q}. \tag{11}$$

### 4 Results

We have used Eqs. 9 and 11 with  $\alpha$  as a fitting parameter to describe the data presented in Fig. 1. The solid line in Fig. 1 is the result of the calculation with  $\alpha = 1.6 \times 10^{-7}$  V.cm. The theory describes the measurements well. The factor  $\alpha$  is only 40% higher than the value calculated according to Eq. 4, which is in good accordance with the theory described in the previous section considering the simplifications we were forced to make.

The shaded part in Fig. 1 represents the contribution to  $\Delta V_t$  due to the energy gap between the first allowed energy level and the bottom of the conduction band. The remainder is the contribution due to the finite distance to the interface. This clearly shows that the incorrect simulation of the long-channel threshold voltage is mainly due to the splitting of the energy levels and to lesser extent to the finite distance to the interface.

In conclusion, we have shown that quantum-mechanical effects need to be taken into account for the calculation of the threshold voltage of deep-submicron n-channel MOSFET's. We have further proposed a simple analytical expression for the first-order correction for the calculation of long-channel threshold of MOSFET's with high levels of channel doping.

# 5 Acknowledgements

The authors thank H. Lifka, A. Walker, C. Juffermans, W. Manders and F. Oude Lansink for the processing of the devices.

#### References

- [1] P. K. Chatterjee, W. R. Hunter, T. C. Holloway, and Y. T. Lin, *IEEE Electron Device Lett.*, vol. EDL-1, pp. 220-223, 1980.

- [2] F. Stern, CRC Crit. Rev. Solid State Sci., pp. 499-514, 1974.

- [3] A.P. Gnädinger and H.E. Talley, Solid-St. Electron., vol. 13, pp. 1301-1309, 1970.

- [4] Yasuyuki Ohkura, Solid-St. Electron., vol. 33, pp. 1581-1585, 1990.