# Electrothermal Properties of 2D Materials

S. Klein<sup>1</sup>, Z. Aksamija<sup>2</sup>

<sup>1</sup>University of Massachusetts, Amherst, MA, USA, <sup>2</sup>University of Utah, Salt Lake City, UT, USA, email: zlatan.aksamija@utah.edu

Abstract—To keep downsizing transistors, new materials must be explored. 2D materials are appealing due to their thinness and bandgap. The relatively weak van der Waals forces between layers in 2D materials allow easy exfoliation and device fabrication but also result in poor heat transfer to the substrate, which is the main path for heat removal. The impaired thermal coupling is exacerbated in few-layer devices where heat dissipated in the layers further from the substrate encounters additional interlayer thermal resistance before reaching the substrate, which results in self-heating ( $\Delta T \neq 0$ where  $\Delta T$  is the temperature rise of the few-layer device) and degradation of mobility. This study explores the electrothermal properties of five materials (MoS2, MoSe2, WS2, WSe2, and 2D black phosphorous). We simulate various devices with selfheating with various  $V_{\text{DS}}$  and examine the effects on mobility and change in device temperature and compare to the isothermal case ( $\Delta T = 0$ ). We observe that self-heating has a significant effect on temperature rise, layer-wise drain current, and effective mobility. We show that black phosphorous performs the best thermally and WSe2 performs the best electrically. This study will inform future thermally aware designs of nano electronic devices based on 2D materials.

### INTRODUCTION

As transistors continue to become smaller, traditional 3D materials such as silicon become problematic as quantum effects prevail [1]. New materials must be explored to continue downsizing semiconductors. 2D materials such as transition metal dichalcogenides (TMDs) and 2D black phosphorus (phosphorene) are attractive replacements as they are thin and contain a bandgap [2]. Mobility suffers in single-layer devices [3] due to charged impurity scattering from the substrate. To resolve this issue, few-layer stacks are explored, using the layers immediately above the first layer to encapsulate the bottom [4]. This results in improved mobility but creates more thermal issues. Heat removal is more difficult in upper layers as they are farthest from the substrate, which dissipates the most heat from the device [5], and the layers create additional interlayer thermal resistance [6] due to weak van der Waals forces between 2D layers [7]. This results in self-heating and a degradation of mobility.

In this study, the four TMDs (MoS2, MoSe2, WS2, and WSe2) as well as 2D black phosphorus (BP) are compared. We look at several electrical properties (drain current and mobility) and multiple thermal properties (temperature rise, joule heating, mobility degradation, TBC, and effective conductivity) to determine what material has the best balance between electrical and thermal performances.

## II. METHODS

The device being simulated is a back-gated MOSFET, composed of 10 layers. The source and drain contacts are connected to the topmost layer with the substrate and gate below the bottommost layer. Each layer has a different resistance, voltage, and current flowing through it. The current encounters extra resistance via interlayer resistance as well as the contact resistance above the topmost layer. The device can be represented as a resistor network, composed of layer resistance, interlayer resistance, and contact resistance, which is used to calculate layer-wise voltage and current. We use the coupled Schrodinger-Poisson equations to calculate carrier concentration per layer  $(Q_i)$  and screening length per layer  $(\lambda_i)$ , from which mobility per layer is calculated using  $\mu_i = \mu_1 + (\mu_{\infty})$  $-\mu_1$ )(1-c<sub>i</sub>) where  $c_i = c_{i-1} (exp(-d_{ML}/\lambda_i))$  and  $d_{ML}$  is the thickness of the layer. We calculate layer-wise resistivity using  $\rho_i$  =  $m/Q_i e \mu_i \cdot L_{channel}$  where m is the fraction of the channel not pinched off, e is the magnitude of the charge of an electron, and  $L_{channel}$  is the length of the channel. We then calculate the total resistivity in the device by adding the interlayer resistances (R<sub>int</sub>) and contact resistances in series with the layer resistivity and then add those values in parallel. Temperature rise per layer is calculated from

$$\Delta T_i = \left(\frac{P_i}{W_{ch}L_{ch}}\right) R_{BD,i} \left[1 - \frac{2L_{H,i}}{L_{ch}} \tanh\left(\frac{L_{ch}}{2L_{H,i}}\right)\right],$$

$\Delta T_i = \left(\frac{P_i}{W_{ch}L_{ch}}\right) R_{BD,i} \left[ \ 1 - \frac{2L_{H,i}}{L_{ch}} \tanh\left(\frac{L_{ch}}{2L_{H,i}}\right) \right],$  where  $L_{H,i} = \sqrt{\kappa_{bulk}d_{ML}R_{BD,i}}$ .  $R_{BD,i}$  is the layer-wise thermal boundary resistance  $(R_{BD,i} = 1/h_{BD,i})$ ,  $\kappa_{bulk}$  is the bulk thermal conductivity, and  $W_{channel}$  is the channel width. The simulation is iterated until convergence is reached (Fig. 1).

## III. RESULTS

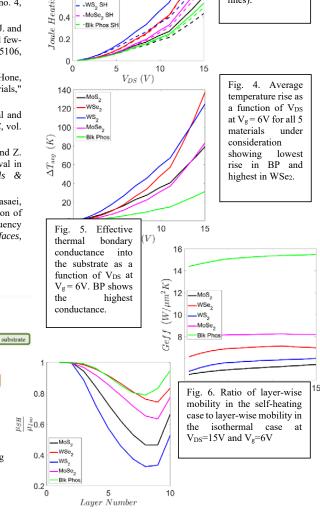

We first look at the ID-VDS characteristics of the five materials for both the isothermal case and the self-heating case where  $I_D = \sum I_i$  in Fig. 2. WS<sub>2</sub> has the most current and BP has the least in the isothermal case. However, current degradation due to self-heating is greatest for WS2 and MoS2, so WSe2 has the most current in that case and MoS2 has the least. Total joule heating  $(P = \sum P_i)$  (in Fig. 3) follows the same trend as the I<sub>D</sub>-V<sub>DS</sub> characteristics. WS<sub>2</sub> experiences the most joule heating in the isothermal case, but WSe<sub>2</sub> experiences the most with selfheating. BP has the least isothermally and MoS2 has the least with self-heating. Next, we look at average temperature rise  $(\Delta T_{avg})$  vs V<sub>DS</sub> in Fig. 4. WS<sub>2</sub> and WSe<sub>2</sub> undergo the most selfheating and BP self-heats the least. We calculate effective thermal conductance using  $G_{eff} = P/\Delta T_{avg}$  in Fig. 5. BP is shown to have the highest  $G_{eff}$  which makes sense given that BP has the lowest amount of self-heating. MoS<sub>2</sub> has the lowest conductance.

Next, we look at the ratio of carrier mobility in the self-heating case to the isothermal case per layer in Fig. 6. Overall, WS $_2$  experiences the largest amount of mobility degradation. BP and WSe $_2$  experience the least. Factoring in phonon-limited mobility, with self-heating, WS $_2$  and WSe $_2$  have the highest upper layer mobility and MoSe $_2$  and BP have the lowest. Thermal boundary resistance (TBR), calculated by taking the inverse of TBC, is plotted for each layer. MoS $_2$  has the highest TBR and BP has the lowest.

100

80

40

20

0

1.2

tem<sup>2</sup>

(mM)

$I_D (\mu A/\mu m)$

-MoS<sub>2</sub> Iso

-WSe<sub>2</sub> Iso

\_WS, Iso

-WSe, SH

ws, sh

MoSe, SH

-MoS<sub>2</sub> Iso

-WSe<sub>2</sub> Iso

-WS<sub>2</sub> Iso -MoSe<sub>2</sub> Iso

Blk Phos

- WSe<sub>2</sub> SH

10

$V_{DS}(V)$

15

60 \_ - MoS<sub>2</sub> SH

Fig. 2. IV-curve at

$V_g = 6V$  for both

(dashed) and self-

heating for various

$V_{DS}$  at  $V_g = 6V$  for

(dashed) and self-

heating case (solid

isothermal

case

the

heating

both

lines).

isothermal

(solid lines).

### IV. REFERENCES

- [1] H. Liu, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tomanek and P. D. and Ye, "Phosphorene: An Unexplored 2D Semiconductor with a High Hole Mobility," ACSN, vol. 8, no. 4, pp. 4033-4041, 2014.

- [2] Z. Jin, X. Li, J. T. Mullen and K. W. and Kim, "Intrinsic transport properties of electrons and holes in monolayer transition-metal dichalcogenides," *Phys. Rev. B*, vol. 90, no. 4, p. 045422, 2014.

- [3] J. H. Kim, T. H. Kim, H. Lee, Y. R. Park, W. Choi and C. J. and Lee, "Thickness-dependent electron mobility of single and fewlayer MoS2 thin-film transistors," AIPA, vol. 6, no. 6, p. 065106, 2016.

- [4] D. Rhodes, S. H. Chae, R. Ribeiro-Palau and J. and Hone, "Disorder in van der Walls heterostructures of 2D materials," *Nat. Mater.*, vol. 18, no. 6, pp. 541-549, 2019.

- [5] A. K. Majee, C. J. Foss and Z. and Aksamija, "Electrical and Electrothermal Properties of Few-Layer 2D devices," *JCE*, vol. 20, no. 1, pp. 2-12, 2021.

- [6] A. K. Majee, Z. Hemmat, C. J. Foss, A. Salehi-Khojin and Z. and Aksamija, "Current Rerouting Improves Heat Removal in Few-Layer WSe2 Devices," ACS Applied Materials & Interfaces, vol. 12, no. 12, pp. 14323-14330, 2020.

- [7] A. Behranginia, Z. Hemmat, A. K. Majee, C. J. Foss, P. Yasaei, Z. Aksamija and A. and Salehi-Khojin, "Power Dissipation of WSe2 Field-Effect Transistors Probed by Low-Frequency Raman Thermometry," ACS Applied Materials & Interfaces, vol. 10, no. 29, pp. 24892-24898, 2018.

Experimental current-voltage data

Use Schrodinger-Poisson equation to calculate charge density and screening length

Phonon dispersions of 2D material and 3D substrate

Phonon dispersions of 2D material and 3D substrate

T+ΔT

Electrical modeling to obtain layer-wise power dissipation

Thermal modeling to obtain thermal boundary conductance (TBC)

Use power dissipation and TBC to calculate layer-wise temperature rise (ΔT)

No Convergence Yes Exit

Fig. 1. Flowchart of our self-heating loop showing electronic and thermal components of the simulator.

Barcelona, June 12-16 2023