## A Microscopic Quantum Simulation of Si/SiO<sub>2</sub> Interface Roughness Scattering in Silicon Nanowire Transistors

Jing Wang, Eric Polizzi<sup>1</sup>, Avik Ghosh, Supriyo Datta and Mark Lundstrom

School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, U.S.A.

<sup>1</sup>Department of Computer Sciences, Purdue University, West Lafayette, Indiana 47907, U.S.A. email: <u>jingw@purdue.edu</u> website: <u>http://falcon.ecn.purdue.edu</u>:8080/

The Silicon Nanowire Transistor (SNWT) has attracted broad attention as a promising device structure for future integrated circuits [1-4]. As a result, the exploration of carrier transport and the modeling of various scattering mechanisms in Si nanowires become increasingly important. In this work, we perform a microscopic, quantum-mechanical simulation of Si/SiO<sub>2</sub> interface roughness scattering (so called "surface roughness scattering (SRS)") [5-10] in SNWTs.

The effects of Si/SiO<sub>2</sub> interface roughness on carrier transport are as follows: 1) the roughness introduces electrostatic potential variations inside the Si body, which behave as a scattering potential for carriers, 2) due to the Si/SiO<sub>2</sub> conduction band-edge discontinuity, the roughness causes a fluctuating electron subband energy and wavefunction shape, which lowers the transmission from the source to the drain (so called "wavefunction deformation scattering" [6-8]). In SNWTs with very small diameters (e.g., <5nm), both effects become substantially important and a direct treatment of SRS in a quantum mechanical framework is necessary.

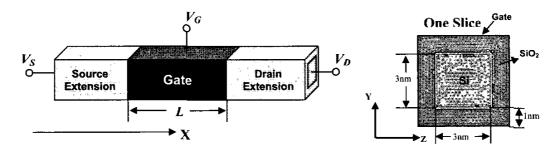

Figure 1 illustrates the simulated structure in this work. The simulation region is discretized with a 3D finite element mesh [11]; each element is a triangular prism with a comparable size to the roughness at the (100) Si/SiO<sub>2</sub> interfaces [12-13]. A 2D random distribution is generated across the Si/SiO<sub>2</sub> interfaces according to the relevant auto-covariance function [12], and based on this random distribution, the (material) types of the elements (prisms) at the Si/SiO<sub>2</sub> interfaces may be changed from Si to SiO<sub>2</sub> or reversely, to mimic the roughened interfaces. The roughened SNWT is then simulated by the non-equilibrium Green's function approach [14]. By using the coupled mode space approach [11], the wavefunction deformation due to the Si/SiO<sub>2</sub> interface roughness is adequately treated. To emphasize the role of SRS on electron transport, we do not include any other scattering mechanisms, so electron transport is coherent inside the device. The simulation results for the roughened device are then compared with those for a device structure with the same geometrical parameters but smooth Si/SiO<sub>2</sub> interfaces, which is treated as the *ballistic* device.

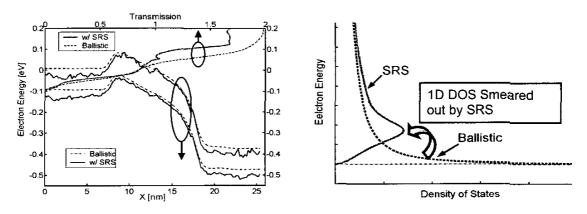

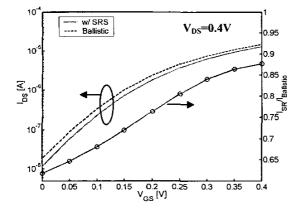

Figures 2 and 3 illustrate the effects of SRS on both the internal parameters (e.g., subbands, transmission) and current-voltage characteristics of the simulated SNWT. It is found that 1) SRS significantly deforms the electron subbands in the SNWT, 2) SRS blocks low-energy injections from the source into the channel, so it reduces the density-of-states (DOS) at low energy and consequently raises the threshold voltage of the device, 3) due to the DOS degradation caused by SRS, the roughened SNWT displays lower subband levels at the top of the barrier under ON-state conditions, which somehow compensates the reduction of transmission due to SRS at the ON-state, and 4) the transmission reduction caused by SRS becomes quite significant when more than one subbands become conductive (this is consistent with the observation that SRS is very important in planar MOSFETs, where a large number of transverse modes are conductive). In brief, this work provides an opportunity to understand the physics of SRS in SNWTs, which can be substantially different from that in planar MOSFETs.

A full journal publication of this work will be published in the Journal of Computational Electronics.

Fig. 1 The schematic diagram of the simulated gate-all-round SNWT with a rectangular cross-section (L=10nm). The X, Y, and Z coordinates are in the (100), (010) and (001) crystal orientations, respectively. The right figure shows a slice of the SNWT with a roughened Si/SiO<sub>2</sub> interface (please note that the pattern of the roughness varies from slice to slice).

Fig. 2 The electron subband profile and transmission coefficient for the simulated SNWT with and without (ballistic) SRS (left). The device is at the ON-state (i.e.,  $V_{GS}=V_{DS}=0.4V$ ), so the source and drain Fermi levels are located at  $\theta eV$  and  $-\theta.4eV$ , respectively. The right plot illustrates the DOS reduction at low energy caused by SRS.

Fig. 3 The *I-V* characteristics (left) of the simulated SNWT and the ratio (right) of the current for the roughened structure,  $I_{SR}$ , to the ballistic current,  $I_{Ballistic}$ .

## **REFERENCE:**

- [1] Y. Cui et al, NanoLett., 3, 149, 2003.

- [2] B. S. Doyle et al, EDL, 24, 263, 2003.

- [3] T. Saito et al, IEICE Trans. Electron., E85-C, 1073, 2002.

- [4] J. Wang et al, IEDM, 695, 2003.

- [5] F. Gamiz et al, JAP, 89, 1764, 2001.

- [6] K. Uchida et al, IEDM, 47, 2002.

- [7] H. Sakaki et al, APL, 51, 1934, 1987.

- [8] A. Gold, PR-B, 35, 723, 1987.

- [9] M. V. Fischetti et al, JAP, 94, 1079, 2003.

- [10] C. -Y. Mou et al, PR-B, 61, 12612, 2000.

- [11] J. Wang et al, to appear in JAP, 2004. (cond-

- matter/0403739)

- [12] S. M. Goodnick et al, PR-B, 32, 8171, 1985.

- [13] T. Yoshinobu et al, Jan. J. Appl. Phys., Partl 26, 1447, 1996.

- [14] S. Datta, IEDM. 703, 2002.

A full journal publication of this work will be published in the Journal of Computational Electronics.