## RF Performance of Strained SiGe pMOSFETs: Linearity and Gain

Wei Ma and Savas Kaya

SEECS, Ohio University, Athens, OH 45701, Email: wei.ma.1@ohio.edu

To continue CMOS scaling in sub-50nm range during the next decade, the use of SOI substrates and strained-Si/SiGe channel layers will be an attractive option [1]. Both approaches can dramatically improve the high frequency performance of MOSFETs due to reduced substrate leakage in the former and enhanced channel mobility and velocity overshoot effects in the latter [2]. A combination of these two approaches is also a possible structure currently investigated, where promising results are already demonstrated experimentally [3]. However, RF performance analysis of this device structure has not received extensive research efforts. In this work, we investigate RF performance of strained-SiGe pMOSFET because of its easy integration into planar architecture than strained-Si nMOSFET. RF figure of merits considered include linearity, intrinsic gain and  $g_m/I_d$ . To optimize RF performance, variations of SOI thickness  $(t_{si})$  and Ge concentration in the channel are investigated. Furthermore, since graded channel (GC) MOSFET has been proposed as a candidate of RF application [4], a graded strained-SiGe channel pMOSFET is studied comparatively for RF analysis.

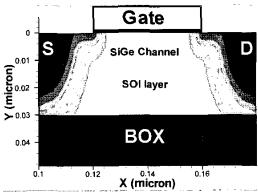

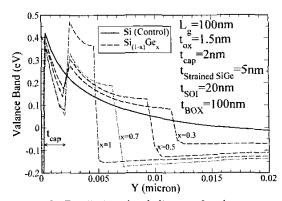

The strained-SiGe pMOSFET structure studied in this work is shown in Fig.1 with a 5nm strained SiGe channel layer. We use 2D device simulator DESSIS to obtain terminal characteristics of our devices [5]. In the simulation, quantum mechanical effects are taken into account using density-gradient corrections. Hydrodynamic transport model is included also to incorporate non-stationary transport in our simulations. Fig.2 shows the equilibrium band diagram of the strained-SiGe channel pMOSFET. For RF figure of merits,  $g_m/I_d$  is calculated from DC simulations, linearity ( $P_{IP3}$ ) is calculated from  $g_m$  derivatives using high-order polynomial fits [6], intrinsic gain ( $g_m/g_d$ ) is extracted from AC simulations. All of the simulations are conducted at the same operation condition ( $I_{DS}=200\mu A/\mu m$ ) to allow fair comparisons.

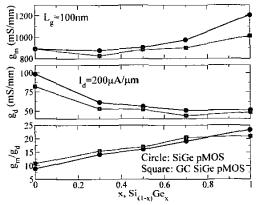

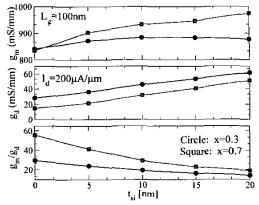

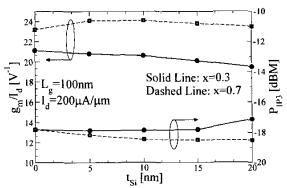

We first compare the RF performance of ordinary strained-SiGe pMOS with GC strained-SiGe pMOS at different Ge concentrations. The former has an unintentional doping density of  $10^{15}$  cm<sup>-2</sup> for the whole channel while the latter has a high doping density  $10^{17}$  cm<sup>-2</sup> in the left half of the channel. We observe in Fig.3 that, as the Ge concentration increases in the channel, the  $g_m/g_d$  improves consistently by as much as 14 (~23dB) in strained-SiGe pMOS, which benefits from an increase in  $g_m$  and a decrease in  $g_d$ . GC structure has only a small (~5dB) positive impact on  $g_m/g_d$ . Fig.5 shows that, by increasing Ge concentration in the channel, the  $g_m/l_d$  improves sharply by ~15V<sup>-1</sup> and the linearity ( $P_{1P3}$ ) decrease slightly (~2dBm) for undoped SiGe pMOS. The non-uniform channel doping has a slightly negative impact on  $g_m/l_d$  and a slightly positive impact on linearity. We also investigate the influence of SOI thickness on RF performance of both undoped and GC devices. From Fig.4, we observe that  $g_m/g_d$  increases for both  $Si_{0.3}Ge_{0.7}$  and  $Si_{0.7}Ge_{0.3}$  pMOS as  $t_{si}$  scales down, with a larger (~30dB) improvement for the former case than for the latter case (~23dB). Fig.6 shows that as  $t_{si}$  scales down,  $g_m/l_d$  increases slightly about  $1.5V^{-1}$  for undoped  $Si_{0.7}Ge_{0.3}$  pMOS while it has optimal value between 5nm to10nm for  $Si_{0.3}Ge_{0.7}$  case. The linearity figures of the same devices do not have a strong dependence on  $t_{si}$ .

An understanding of interplay between device parameters as well as incorporation of more elaborate physical models is essential for the use SiGe technology in RF applications. Therefore we investigate how the SiGe pMOSFET layer structure, gate geometry, and doping profiles result in several trade-offs in RF device design, and how TCAD tools may be deployed to search for optimum gain and linearity conditions in a given application.

- [1] B Yu, IEDM Tech. Dig, p.937, 2001

- [2] K Rim, IEDM Tech. Dig, p.43, 2002

- [3] T. Mizuno et al., IEDM Tech. Dig, p.31, 2002.

- [4] B. Cheng et al., IEEE Int. SOI Conference, p.113, 1998.

- [5] ISE System Inc., TCAD suite, www.ise.com

- [6] W Ma, S Kaya and A Asenov, Proc. of EDMO, p.255, 2003.

A full journal publication of this work will be published in the Journal of Computational Electronics.

FIGURE 1: Strained-SiGe p-MOSFET structure with  $L_{\rm eff}$ =100 nm. Mesh lines for the channel and contacts are indicative of fast varying potentials in these layers.

FIGURE 3: Comparison of ordinary strained-SiGe pMOS with GC strained-SiGe pMOS for  $g_m$ ,  $g_d$  and  $g_m/g_d$  at different Germanium concentration.

FIGURE 5: Comparison of ordinary strained-SiGe pMOS with GC strained-SiGe pMOS for  $g_{\rm m}/I_{\rm d}$  and  $P_{\rm IP3}$  at different Germanium concentration.

FIGURE 2: Equilibrium band diagram for the structure considered in this work. Note that only the classical potentials are plotted in the band diagram.

FIGURE 4: Impact of SOI body thickness  $(t_{si})$  on  $g_m$ ,  $g_d$  and  $g_m/g_d$  at of strained-Si<sub>0.7</sub>Ge<sub>0.3</sub> pMOS and strained-Si<sub>0.3</sub>Ge<sub>0.7</sub> pMOS.

Figure 6: Impact of SOI body thickness  $(t_{si})$  on  $g_m/I_d$  and linearity  $(P_{IP3})$  of strained-Si<sub>0.7</sub>Ge<sub>0.3</sub> pMOS and strained-Si<sub>0.3</sub>Ge<sub>0.7</sub> pMOS.

A full journal publication of this work will be published in the Journal of Computational Electronics.