## From Layout to Circuit: Multi-Dimensional Process and Device Simulation – Current Status and Open Problems

#### W. Fichtner

#### Integrated Systems Laboratory, Swiss Federal Institute of Technology, Gloriastrasse 35, CH-8092 Zürich, Switzerland

Physical simulation of semiconductor processes and devices has become a widely accepted procedure in the development of new technologies and circuits, allowing more accurate prototype designs and time-efficient optimization cycles. Apart from its impact on the microelectronics industry, however, it has also established itself as an important field for academic and industrial research.

Over the past decades, simulation has undergone important developments on several fronts. While one-dimensional (1D) calculations dominated the early efforts in the 1960s and 1970s, twodimensional (2D) investigations have become standard in the last decade for process and device analysis. Today, the simulation community is increasingly confronted with requests to optimize more complex merged 2D or even 3D structures. This enormous increase in simulation capabilities can be attributed to several factors such new numerical algorithms, improved physical understanding and more powerful computing platforms.

Looking at the simulation environment with a more critical eye, however, the positive remarks made above must be somewhat dampened in the light of reality. This is especially true is one would compare physical simulation to the more mature field of microelectronics CAD (i.e. IC design, simulation and test). The following paragraphs might illustrate this criticism. (In the following, let us assume a silicon "environment". Remarks much more critical must be made for III-V materials and devices).

To my knowledge, no complete system exists today that *really* allows an educated user to start at the layout and process flow level, to work upwards through process and device simulation and to end at the circuit level with a set of extracted parameters for CAD Models. Obviously, our dream system should be capable to handle more or less arbitrarily shaped devices of different dimensionality, it should contain all relevant physical models for process and device behavior, etc.

Looking in more detail, some answers can be given to explain this unsatisfactory state. While comprehensive 1D and 2D process simulators are available, these are essentially stand-alone tools requiring textual input. Apart from a few exceptions, transparent coupling to layout tools and process databases does not exist. 3D process simulators are only available for certain process steps. Interfacing process simulation results to device analysis has been solved only in one dimension. For complex 2D structures, major bottlenecks exist due to difficulties in structure recognition, mesh generation, and interpolation strategies.

On the device side, the situation is somewhat better, especially in 1D and 2D. The spectrum of available software ranges from simple drift-diffusion simulators to highly advanced software environments containing lattice and carrier heating or even Monte Carlo models. Even if the bottleneck of 3D structure generation and process simulation can be overcome, 3D device simulation restricts itself mainly to steady-state analysis due to the enormous CPU expenses involved. Nevertheless, the situation is not completely satisfactory. Most available software tools are restricted to only one level of dimensionality and cannot be embedded in a circuit environment.

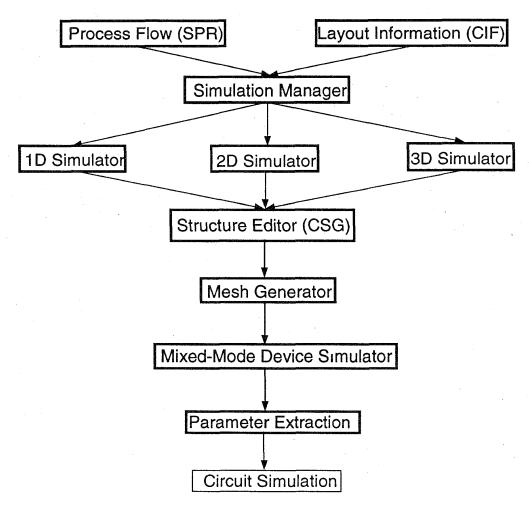

Obviously, the shortcomings mentioned have been recognized for some time. Remedies are being studied and implemented in a variety a programs such as the US TCAD initiative and the European ESPRIT and JESSI projects. In the following, I would like to outline one possible attempt to attack several of the serious problems mentioned above. Over the past three years, we have been working on a "dream system" called *Ligament* jointly with several other groups. Figure 1 shows a flowchart of this system which today is fully operational in two dimensions. For complex 3D with nontrivial surface features (e.g. nonplanarities), crashes still occur on a regular basis due to structure generation problems (see below). Through the rest of this paper, examples from a VLSI BiCMOS technology (18 masks) developed jointly by us and a major Swiss watch company will be used to illustrate salient points.

LIGAMENT combines the design representation of a technology (using design layout information) with a process representation to automatically generate 1D, 2D, and 3D structures to be transparently used in device simulation.

The three major inputs to the system are layout information (CIF files), a description of the process flow, and the electrical conditions for the device. The process flow is contained in a *semicon*ductor process representation (SPR) which allows a detailed description of a complete fabrication sequence. Details can be found in [1].

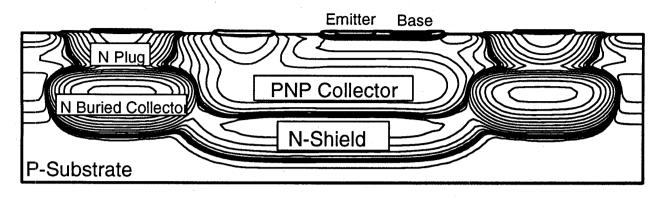

DIOS process simulation [2] is performed automatically using simulation input generated from the supplied SPR and CIF descriptions of the device, employing sohisticated mesh adaption. For 2-D simulations, process simulation results can be directly used to generate a device grid [3]. As one representative example, Fig. 2 shows the doping profile for a vertically isolated BiCMOS pnp transistor. This structure was generated automatically from the layout and SPR information of the process ( in nearly a CPU day on a Sparc 10). The final grid contains more than 100K triangles.

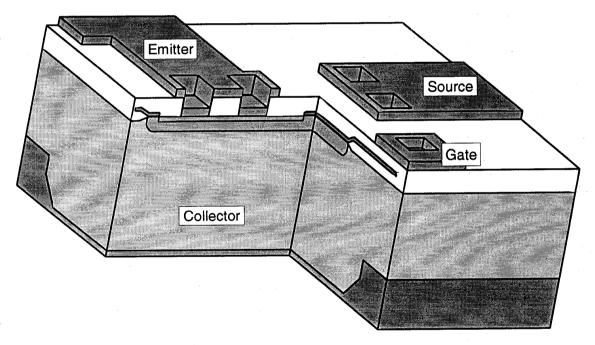

Looking at 3D structures, the nonavailability of 3D process simulation and the expense of obtaining multiple 2D cuts asks for a time efficient and pragmatic solution. For each unique combination of masks present on the layout, LIGAMENT performs a 1D simulation. The merged MOS-bipolar structure shown below required a total of 35 1D runs. When edge information is detected, 2D simulation is carried out (in this case a total of 11 2D simulations). These 2D simulations are restricted to small regions and CPU requirements are small. LIGAMENT splits simulation input decks with common initial stages into a tree to avaiod repetitive runs. The UNIX<sup>1</sup> programming facility make is used to ensure that simulation branches are executed correctly. Process simulation results are merged to form a 3D solid model using the ECHIDNA system[4]. Figure 3 shows the assembled "final" BiCMOS structure, that can be passed to the 3D grid generator OMEGA[5].

While a result like this is definitely encouraging, it was not obtained as elegantly as we are used to in 1D and 2D. Considerable difficulties remain to be solved, especially stability problems in underlying computational geometry algorithms.

Once grid and doping information is available, device simulation can be performed. We have developed a mixed-mode device and circuit simulator called SIMUL that allows to mix 1D, 2D and 3D devices [6]. By extending SIMUL to simulate more than one device as well as giving it access to the circuit simulator's functionalities it has been possible to combine both simulators' features into a single program (1D, 2D, 3D devices, extensive physical models for power devices, thermalelectric effects and all basic SPICE models). While other mixed-device and circuit simulators such as MEDUSA and CODECS have been presented, the originality of this work lies specifically in the possibility of a single code to simulate many devices of different dimensions together with the support of a full circuit simulator.

SIMUL was coded in the object-oriented language C++ allowing both fast prototyping and efficient execution. Our eperience with using a modern programming language has been extremely positive for many UNIX platforms ranging from Cray and NEC supercomputer to workstations.

The work reported here has been obtained through a joint effort by several people in the Integrated Systems Laboratory at ETHZ. Among others, I would like to mention K. Kells, J. Litsios and S. Müller (MESHBUILD and SIMUL), Nancy Hitschfeld (OMEGA), T. Feudel and N. Strecker (DIOS), A. Liegmann and C. Pommerell (linear solvers), C. Hegarty and P. Lamb LIGAMENT, and M. Westermann (PICASSO graphics system). Input (and criticism) is greatfully acknowledged from C. Lombardi (ST), G. Baccarani (Bologna), and P. von Staa (Bosch). This work was supported by the Swiss Lesit program, the Swiss National Science Foundation, and ESPRIT.

### References

[1] C. Hegarty and W. Fichtner, "Semiconductor process representation," *IEEE Transactions on CAD*, vol. submitted, 1992.

[2] N. Strecker, "DIOS 3.0 user's guide," tech. rep., ETH Integrated Systems Laboratory, 1992.

<sup>&</sup>lt;sup>1</sup>Unix is a trademark of AT&T Bell Laboratories

- [3] S. Müller, K. Kells, and W. Fichtner, "Automatic rectangle-based adaptive mesh generation without obtuse angles," *IEEE Trans. on CAD*, vol. 11, pp. 855-863, 1992.

- [4] P. R. Lamb, , C. Hegarty, N. Hitschfeld, and W. Fichtner, "Generating solid models for VLSI process and device simulation," in *Proceedings NUPAD-IV*, p. 1175, 1992.

- [5] N. Hitschfeld, S. Müller, and W. Fichtner, "Generation of 3-d delaunay meshes for complex geometries using iterative refinement," in *Algorithms, Software, Architecture - Information Pro*cessing 92, Volume I (J. van Leeuwen, ed.), pp. 388-394, Elsevier Publishing (North Holland), 1992.

- [6] S. Müller, N. Hitschfeld, C. Pommerell, K. Kells, M. Westermann, and W. Fichtner, "Technology-CAD algorithms, implementation and results," in *Proceedings of the Second NEC Symposium*, SIAM, 1992.

Figure 1: Structure of the Ligament system

# **BICMOS Vertical Isolated PNP Transistor**

Figure 2: Doping distribution for vertically isolated pnp transistor in VLSI BiCMOS technology

Figure 3: Cut view of 3D merged BiCMOS structure