# Electro-Thermal Analysis and Edge Termination Techniques of High Current β-Ga<sub>2</sub>O<sub>3</sub> Schottky Rectifiers

### Ribhu Sharma

Material Science and Engineering University of Florida Gainesville, Fl, USA https://orcid.org/0000-0001-5754-7873

### Fan Ren

Chemical Engineering

University of Florida

Gainesville, FL, USA

https://orcid.org/0000-0001-9234-019X

### Erin Patrick

Electrical and Computer Engineering University of Florida Gainesville, Fl, USA erin.patrick@ece.ufl.edu

### Mark Law

Electrical and Computer Engineering University of Florida Gainesville, Fl, USA law@ece.ufl.edu Jiancheng Yang

Chemical Engineering) University of

Florida

Gainesville, Fl, USA

yjcallen@ufl.edu

### Stephen Pearton

Material Science and Engineering University of Florida Gainesville, Fl, USA https://orcid.org/0000-0001-6498-1256

Abstract—The performance and limitations of β-Ga<sub>2</sub>O<sub>3</sub> Schottky rectifiers is studied via simulation using the Florida Object Oriented Device and Process (FLOODS) TCAD simulator. The effect of forward bias and power is examined for various bulk and epitaxial layer thicknesses as well as for heat sink geometries. Thicker bulk/substrate results in higher maximum temperature values whereas a thinner epitaxial-layer results in higher forward currents and hence a higher maximum temperature values via Joule heating. A Cu finned heat sink geometry results in a 26.76% reduction in the maximum temperature. Edge termination techniques are examined for β-Ga2O3 Schottky rectifiers in order to maximize the breakdown voltage, identify the location of breakdown and mitigate the maximum electric field. Best results have been observed for Al<sub>2</sub>O<sub>3</sub> as the dielectric material in a field-plate structure while the effect of field-plate dimensions is also studied.

Keywords—Gallium oxide, semiconductors – II-VI, Rectifiers, electro-thermal, edge-termination

## I. INTRODUCTION

Gallium oxide has recently emerged as the prime candidate for applications in power electronics due to its large bandgap, high electric breakdown strength, low on-resistance and low charge storage times [1][2][3]. The suitability of semiconductors as electronic power switches is evaluated by calculating various figure-of-merits (FOM). The large bandgap ( $\sim$ 4.85 eV) of Ga<sub>2</sub>O<sub>3</sub> translates into a high breakdown field (E<sub>br</sub>) creflected by a high Baliga's figure-of-merit which is about 4-7 times higher than that for SiC, leading to lower conductance losses at a low manufacturing cost in comparison to 4H-SiC diodes [4]. Notably, the electric field breakdown strength (E<sub>br</sub>) of Ga<sub>2</sub>O<sub>3</sub> is more than double the theoretic limits of SiC and GaN.

Schottky rectifiers have been adopted for power electronics applications due to its fast switching speed, which is required to improve the efficiency of inductive motor controllers and power supplies [5][6] as well as low forward voltage drop and high-temperature operability. Along with the high  $E_{\text{br}}$ ,  $Ga_2O_3$  also possesses an on-state resistance value of over 10 times larger than conventional Si rectifiers.

An ongoing issue with Ga<sub>2</sub>O<sub>3</sub> is its thermal conductivity (21 W/m.K) [7][8], which is an order of magnitude lower than its commercial counterparts, i.e. SiC and GaN. Recent studies [9][10][11] performed on vertical Schottky rectifiers have achieved high forward-currents and high breakdown voltages,

due to the rapid progress in the epitaxial growth methods. These studies focus on the realization of large dimension devices; hence it is important to understand the rise and inefficient dissipation of heat from the channel resulting in a degradation of electron transport properties. The thermal properties of Gallium oxide devices have been studied recently with a focus on thermoreflectance-based thermography and imaging of Ga<sub>2</sub>O<sub>3</sub> Schottky diodes [4][12], Ga<sub>2</sub>O<sub>3</sub> Field effect transistors [13] and Ga<sub>2</sub>O<sub>3</sub> MOSFETs [14]. Edge termination techniques for GaN and SiC devices to maximize breakdown voltage (V<sub>br</sub>) have been well established [15][16][17][18][19]; however, such methods have not yet been fully developed for Ga<sub>2</sub>O<sub>3</sub>. One of the biggest challenges for Ga<sub>2</sub>O<sub>3</sub> technology is the relative absence of p-type epitaxy or p-type doping which rules out the 'guard ring structure' method of edge termination [20][21]. This leaves methods like field plate structures [21][22] and high resistivity layers created by ion implantation [23] for edge termination.

In this paper, Ga<sub>2</sub>O<sub>3</sub> Schottky diodes are examined to assess the limitations stated above and to improve the design considerations in terms of dimensions, structure, and the materials used. We report on the effect of dimensionality on the forward current and heat generation by modeling the current density and heat flow in the device. Edge termination techniques are also evaluated in a separate set of simulations.

### II. SIMULATION METHODS

The partial and total differential equations governing the physics of the electrical and thermal domains are solved self-consistently with the FLOODS TCAD simulator. FLOODS/FLOOPS is a partial differential equation (PDE) solver, written as an extension to the Tcl language for easy specification of PDEs and boundary conditions [24].

# A. Device structure

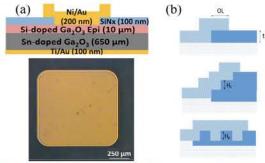

The device structure as given in Fig. 1a is used as the reference for the study as a two-dimensional model and designed to achieve both high forward currents and good reverse breakdown characteristics [9]. The device consists of a lightly doped epitaxial layer grown on highly doped bulk β-Ga<sub>2</sub>O<sub>3</sub> with [001] surface orientation and E-beam evaporated Ni/Au is used to form the Schottky (top) contact, while Ti/Au is used to form the Ohmic contact. In order to accurately model the electro-thermal profile the experimental IV curves are fitted via modeling [29]. The doping concentrations for the electro-thermal simulations are 1.3x10<sup>16</sup> and 3.6x10<sup>18</sup>

cm-3 for the epi and bulk layer respectively, and for the edge termination simulations are 2.8x1016 and 4.8x1018 for the epi and bulk layer respectively.

Figure 1. Schematic of a) vertical geometry Ni/Au Schottky structure (top) and top view with a contact area of 0.01 cm<sup>-2</sup>, and b) field plate structures showing field plate overlap (OL), dielectric thickness (t), dielectric step height (Hs), and pillar height (Hp).

#### B. Electrical domain

Equations used the model include the common device equations [25] including the Poisson's, continuity and current density equations. By using the Boltzmann relation, the quasi-Fermi level from the current density equation can be related to the electrostatic potential. For the electric field analysis, the gradient of the electrostatic potential is then used to obtain the electric field, |E|. Equation 1 describes the formulation of ionized donor trap density,

$$\frac{N_D^+}{N_{tot}} = \int \left(\frac{1}{\frac{E_F - E}{1 + 2e^{\frac{E_F}{kT}}}}\right) \left(\frac{1}{\nabla E\sqrt{2\pi}} e^{\frac{\left(E - E_T\right)^2}{2\nabla E^2}}\right) dE, \tag{1}$$

where  $N_{tot}$  is the total donor trap concentration,  $N_D^+$  is the ionized donor density, EF and ET are the electron quasi-Fermi levels and trap levels, respectively, and  $\nabla E$  is the energy spread of the traps. The total trap densities and energy levels of the traps associated with β-Ga<sub>2</sub>O<sub>3</sub> [26] have been added into the above model. The mobility model used has been incorporated using the equations derived by Ma et al. [27].

Table 1. Material (electronic and thermal) properties of Ga2O3 vs other semiconductors.

|                                | Si   | 4H-SiC | GaN<br>(Wurzite) | Ga <sub>2</sub> O <sub>3</sub> |

|--------------------------------|------|--------|------------------|--------------------------------|

| Eg (eV)                        | 1.1  | 3.3    | 3.4              | 4.6-4.9                        |

| $\mu_n$ (cm <sup>2</sup> /V-s) | 1400 | 1000   | 1200             | 100-200                        |

| E <sub>cr</sub> (MV/cm)        | 0.3  | 2.5    | 3.3              | 8                              |

| ε                              | 11.8 | 9.7    | 9.0              | 10.0                           |

| Normalized<br>BFOM             | 1    | 340    | 870              | 1100-<br>2250                  |

| κ at 300K (W/m-<br>K)          | 150  | 270    | 210              | 27 [010]<br>11 [100]           |

#### C. Thermal Domain

Using the electron and hole current densities, heat generation (Q) is incorporated into the model via Joule heating [28][29]. Heat transport is modeled as a function of heat generated and temperature change with respect to time and space via the following equation:

$$C \frac{\partial T}{\partial t} - \nabla \cdot K \nabla T = Q$$

(2)

where C is the specific heat capacity, T is temperature and K is the thermal conductivity. The thermal conductivity for Ga<sub>2</sub>O<sub>3</sub> has been studied in detail, while Table I also shows the

anisotropic nature of the thermal conductivity. Due to the surface orientation along the [001] direction and heat moving along the [001] direction, we assume an average value of 21 ± 2 W/mK. In coherence with previous thermal studies [31] an isotropic value for the thermal conductivity has been considered. However, future work with anisotropic thermal conductivity and the temperature dependence on the conductivity is ongoing. We use a convective heat transfer [32] equation as the boundary condition for heat transfer. given by Newton's law of cooling:

$$q'=hA(T_s-T_{\infty}) \tag{3}$$

where q' is the heat flux, h is the heat transfer coefficient, A is the area of the surface, T<sub>s</sub> and T<sub>∞</sub> (300K) are the surface and ambient temperatures respectively. The heat transfer coefficient is expressed as a function of three dimensionless numbers, the Nusselt (Nu), Grashof (Gr) and the Prandtl (Pr) numbers.

$$Nu(Gr, Pr) = hL/k$$

(4)

$$Gr = \frac{g\beta (T_s - T_{\infty})L^3}{v^2}$$

$$Pr = \frac{\mu C}{L}$$

(5)

$$Pr = \frac{\mu C}{L}$$

(6)

In Eqs 4-6, L is the characteristic length, k is the thermal conductivity, g is the gravitational force, B is the volume coefficient of expansion ( $\beta = 1/T$ ; for an ideal gas),  $\mu$  and  $\nu$ are the dynamic and kinematic viscosities. In order to get an expression for the heat transfer coefficient for different surfaces a simpler expression gives a better understanding:

$$\overline{Nu} = \frac{hk}{r} = c(Gr Pr)^m$$

(9)

where c and m are constants, which depend on the type of surface in question (i.e., a vertical surface or a horizontal surface). A Dirichlet boundary condition is applied for the temperature at the bottom side of the wafer of T=300K, representing a perfect heat sink. While modeling the convective heat transfer from the top and sides of the device, Neumann boundary conditions have been set for the temperature.

### III. RESULTS AND DISCUSSIONS

# A. Electro-Thermal management

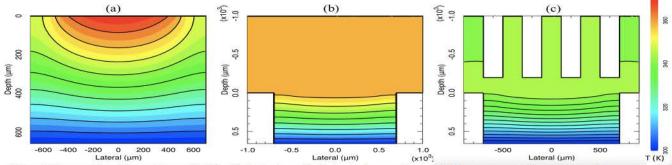

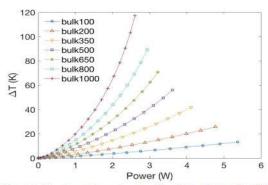

The effect of forward (0-2.5 V) and power generation (0-5.5 W) is examined for the device structure. The effect of the voltage bias is reflected in heat generation in the drift region near the epi-metal interface and results in highest temperature values near this interface. A temperature profile is simulated in the device cross-section as seen in Fig 2a, and the effect of dimensionality is seen via this temperature profile and peak temperature (T<sub>max</sub>) values. The bulk thickness is varied from 100 μm to 1000 μm while the epi-layer thickness and contact area were kept constant. This resulted in T<sub>max</sub> values from 313 K for the 100 μm bulk to 417 K for 1000 μm bulk thickness. The rise in temperature also causes a drop in the electron mobility, while a thinner bulk also causes a higher effective heat dissipation via the bottom contact. Thinning the substrate thickness shows a significant reduction in heating in the device as seen in Fig 3.

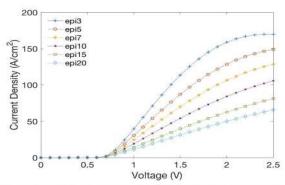

Similarly, the epitaxial layer thickness was varied from 3 μm to 20 μm while the bulk-layer thickness and contact area

Figure 2. Cross-sectional temperature profile for a diode structure with free/natural convection from (a) device top and side surfaces peak temperature 369 K), (b) a copper top-side heat sink block (peak temperature 359 K), and (c) a copper top-side finned heat sink (peak temperature 344 K

Figure 3. The temperature rises as a function of Power ( $P=V^2/R$ ) while varying the bulk layer thickness from 100  $\mu m$  to 1000  $\mu m$  with epilayer thickness constant at 7  $\mu m$ .

were kept constant. As the epi-layer is thinned, the resistance decreases which results in higher currents in the device, (Fig 4); however, this results in a trade-off for peak temperature as the  $T_{\text{max}}$  ranges from 464 K for the 3  $\mu m$  epi layer to 324 K for the 20  $\mu m$  epi-layer thickness diode. The self-heating effects are evident, and the importance of efficient heat dissipation is realized.

Figure 4. The dependence of the forward J-V characteristics on the epilayer thickness from 3 μm to 20 μm with bulk thickness constant at 650 μm.

Initial studies show the importance of dimensions [4] and the simulations show considerable amounts of heat being dissipated from the Schottky (top) contact, a requirement for top-side passive cooling methods like nanocrystalline diamond capping layers and flip-chip hetero-integration. In electronics, copper is one of the most widely used material as a heat sink and different structures have been investigated thoroughly. Two top-side cooling cap heat-sink designs have been considered: a solid copper block and a finned copper structure. Heat loss from the heat sinks to the atmosphere is modeled as free convection via a steady flux. Fig 2 shows the temperature profile for three test simulations: a) natural

convection with bulk thickness of 650  $\mu m$  and epi thickness of 7  $\mu m$ , b) the same device structure with a 1 mm thick solid Cu heat sink block with a width of 2 mm on top, c) the same device structure with a 1 mm thick finned copper heat sink and 200  $\mu m$  fin thickness. As seen in the figure, the solid heat sink reduces the  $T_{max}$  value by  $\sim 10$  K, while the finned heat sink reduces  $T_{max}$  by  $\sim 25$  K compared to the device with no heat sink. The reduction is device temperature causes the mobility to increase which results in higher forward currents.

# B. Edge termination techniques

The field plate (FP) structural variance is shown in Fig 1b. The electric field distribution is simulated and breakdown locations are observed which helps in concluding where the device is breaking down. Traditionally device breakdown happens near the contact edges due to field crowding near the edge, and edge termination is important to mitigate these effects. The electric field is mapped out as a function of reverse voltage and the breakdown voltage is noted as the critical electric field of the material is reached. The simulations are performed for each structure using the same mesh and the same technological parameters in order to maintain homogeneity in the results. Four dielectric materials have been studied as the FP dielectric;  $SiN_x$  ( $\varepsilon$ =7.0,  $E_{br}$ =6.7 MV/cm), SiO<sub>2</sub> ( $\varepsilon$ =3.9, E<sub>br</sub>=10 MV/cm), Al<sub>2</sub>O<sub>3</sub> ( $\varepsilon$ =8.0,  $E_{br}$ =8.68 MV/cm), and HfO<sub>2</sub> ( $\varepsilon$ =15.5,  $E_{br}$ =5.3 MV/cm). Figure 1.(b) shows the different FP structures used in the

Figure 5. Plots showing the normalized breakdown voltage as a function of (a) field plate overlap (blue) and dielectric thickness (red), and (b) dielectric pillar height (blue) and dielectric step height (red).

simulations and denotes the variables in our simulations, i.e. dielectric layer thickness, filed plate overlap, step height, and pillar height. The results have been represented in Fig 5, the best results have been achieved for  $Al_2O_3$  due to its high critical field strength and high relative permittivity, with a normalized breakdown field ( $V_{Nbr}$ ) of more than 2 for the dielectric thickness equal to or greater than 0.5  $\mu m$ . Furthermore, using  $Al_2O_3$  dielectric step FP structure, a  $V_{Nbr}$  or more than 3 is achieved, while an  $Al_2O_3$  pillar height of 1  $\mu m$  achieves the highest  $V_{Nbr}$ . Future work on ion implantation to create highly resistive area near the contact is currently being developed.

### IV. CONCLUSIONS

This paper conducted a thorough investigation via simulations into the effect of device design on  $\beta\text{-}Ga_2O_3$  Schottky rectifiers to aid device optimization. Two pressing concerns of  $Ga_2O_3$  as a power-electronics materials are addressed and the results predict efficient design considerations. Industry desires devices that generate high power and low self-induced heating. The results predict that a thin epitaxial layer and a thin substrate would achieve the desired result. The simulations predict a significant amount of heat being dissipated neat the Schottky contact and warrant the requirement of top-side passive cooling. In order to maximize the breakdown voltage, edge termination techniques were investigated and field plate designs and dielectric materials were studied.

### ACKNOWLEDGMENT

The work at UF is partially supported by HDTRA1-17-1-0011 (Jacob Calkins, monitor). The project or effort depicted is sponsored by the Department of the Defense, Defense Threat Reduction Agency. The content of the information does not necessarily reflect the position or the policy of the federal government, and no official endorsement should be inferred.

### REFERENCES

- G. Jessen, K. Chabak, A. Green, J. McCandless, S. Tetlak, K. Leedy, R. Fitch, S. Mou, E. Heller, S. Badescu, A. Crespo, and N. Moser. 75th IEEE Device Research Conference (DRC) (2017).

- [2] K. Momma and F. Izumi, J. of Appl. Crys., 41, 653–658 (2008).

- [3] H. Wang, thesis, (2007) <a href="http://hdl.handle.net/10919/27517">http://hdl.handle.net/10919/27517</a>.

- [4] B. Chatterjee, A. Jayawardena, E. Heller, D. W. Snyder, S. Dhar, and S. Choi, *Review of Scientific Instruments*, 89, 114903 (2018).

- [5] S. J. Pearton, J. Yang, P. H. Cary, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro. Appl. Phy. Rev., 5, 11301 (2018).

- [6] M. A. Mastro, A. Kuramata, J. Calkins, J. Kim, F. Ren, and S. J. Pearton, ECS J. of Sol. State Sci. and Tech. 6,356 (2017).

- [7] Z. Guo et al., "Anisotropic thermal conductivity in single crystal β-gallium oxide," Appl. Phys. Lett., vol. 106, no. 11, p. 111909, Mar. 2015.

- [8] M Handwerg and R Mitdank and Z Galazka and S F Fischer, "Temperature-dependent thermal conductivity in Mg-doped and undoped β-Ga 2 O 3 bulk-crystals," Semi. Sci. and Tech., vol. 30, no. 2, p. 24006, 2015.

- [9] J. Yang, F. Ren, M. Tadjer, S. J. Pearton, and A. Kuramata. AIP Advances, 8, 55026 (2018).

- [10] J. Yang, S. Ahn, F. Ren, S. J. Pearton, S. Jang, and A. Kuramata, IEEE Elec. Dev. Lett., 38, 906–909 (2017).

- [11] J. Yang, F. Ren, M. Tadjer, S. J. Pearton, and A. Kuramata, ECS J. of Sol. State Sci. and Tech., 7, Q92—Q96 (2018).

- [12] P. E. Raad et al., "Thermoreflectance Temperature Mapping of Ga2O3 Schottky Barrier Diodes," in H01 - Wide Bandgap Semiconductor Materials and Devices 20, Dallas, TX, 2019.

- [13] J. Chen, Z. Xia, S. Rajan, and S. Kumar, "Analysis of Thermal Characteristics of Gallium Oxide Field-Effect-Transistors," presented at the 2018 17th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), 2018.

- [14] B. Chatterjee, K. Zeng, C. D. Nordquist, U. Singisetti, and S. Choi, "Device-Level Thermal Management of Gallium Oxide Field-Effect Transistors," *Trans. on Comp., Pack. and Manu. Tech., June, 2019*.

- [15] V. Soler et al., "Planar edge terminations for high voltage 4H-SiC power MOSFETs," Semi. Sci. and Tech., vol. 32, no. 3, p. 35007, Jan. 2017.

- [16] M. C. Tarplee, V. P. Madangarli, Quinchun Zhang, and T. S. Sudarshan, "Design rules for field plate edge termination in SiC Schottky diodes," *IEEE Tran. on Elec. Dev.*, vol. 48, no. 12, pp. 2659–2664, Dec. 2001.

- [17] J. R. Laroche, F. Ren, K. W. Baik, S. J. Pearton, B. S. Shelton, and B. Peres, "Design of edge termination for GaN power Schottky diodes," *J. of Electronic Materials*, vol. 34, no. 4, pp. 370–374, Apr. 2005.

- [18] A. M. Ozbek and B. J. Baliga, "Planar Nearly Ideal Edge-Termination Technique for GaN Devices," *IEEE Electron Dev. Lett.*, vol. 32, no. 3, pp. 300–302, Mar. 2011.

- [19] A. M. Ozbek and B. J. Baliga, "Finite-Zone Argon Implant Edge Termination for High-Voltage GaN Schottky Rectifiers," *IEEE Elec. Dev. Lett.*, vol. 32, no. 10, pp. 1361–1363, Oct. 2011.

- [20] J. B. Varley, A. Janotti, C. Franchini, and C. G. Van de Walle, "Role of self-trapping in luminescence and p-type conductivity of wide-band-gap oxides," *Phys. Rev. B*, vol. 85, no. 8, p. 81109, Feb. 2012.

- [21] J.-H. Choi, C.-H. Cho, and H.-Y. Cha, "Design consideration of high voltage Ga2O3 vertical Schottky barrier diode with field plate," *Results in Physics*, vol. 9, pp. 1170–1171, Jun. 2018.

- [22] K. Konishi et al., "1-kV vertical Ga2O3 field-plated Schottky barrier diodes," Appl. Phys. Lett., vol. 110, no. 10, p. 103506, Mar 2017

- [23] Y. Gao et al., "High-Voltage β-Ga2O3 Schottky Diode with Argon-Implanted Edge Termination," Nano. Res. Lett., vol. 14, no. 1, p. 8, Jan. 2019.

- [24] M. E. Law and S. M. Cea, "Continuum based modeling of silicon integrated circuit processing: An object-oriented approach," Computational Materials Science, vol. 12, no. 4, pp. 289–308, Nov. 1998.

- [25] R. Sharma, E. Patrick, M. E. Law, J. Yang, F. Ren, and S. J. Pearton, "Thermal Simulations of High Current β-Ga2O3 Schottky Rectifiers," ECS J. of Sol. State Sci. and Tech., vol. 8, no. 7, pp. Q3195–Q3201, Jan. 2019.

- [26] Z. Zhang, E. Farzana, A. R. Arehart, and S. A. Ringel, "Deep level defects throughout the bandgap of (010) β-Ga2O3 detected by optically and thermally stimulated defect spectroscopy," Appl. Phys. Lett., vol. 108, no. 5, p. 52105, Feb. 2016.

- [27] N. Ma et al., "Intrinsic electron mobility limits in β-Ga2O3," Appl. Phys. Lett., vol. 109, no. 21, p. 212101, Nov. 2016.

- [28] G. K. Wachutka, "Rigorous thermodynamic treatment of heat generation and conduction in semiconductor device modeling," *IEEE Trans. on Computer-Aided Design of Int.* Circ. and Sys., vol. 9, no. 11, pp. 1141–1149, Nov. 1990.

- [29] E. Patrick, D. Horton, M. Griglione, and M. E. Law, "A Self-Consistent Electro-Thermo-Mechanical Device Simulator based on the Finite-Element Method," SISPAD 2012, Sep. 2012.

- [30] T.-S. Kang et al., "Thermal Simulation of 193 nm UV-Laser Lift-Off AlGaN/GaN High Electron Mobility Transistors Mounted on AlN Substrates," ECS Transactions, vol. 41, no. 6, pp. 129–136, Oct. 2011.

- [31] E. A. Douglas, F. Ren, and S. J. Pearton, "Finite-element simulations of the effect of device design on channel temperature for AlGaN/GaN high electron mobility transistors," *J. of Vac. Sci. & Tech. B*, vol. 29, no. 2, p. 20603, Mar. 2011.

- [32] F. P. Incropera, D. P. Dewitt, T. L. Bergman, and A. S. Lavine, Fundamentals of heat and mass transfer, 6th ed. John Wiley and son.