# A SPICE Compatible Compact Model for Process and Bias Dependence of HCD in HKMG FDSOI MOSFETs

Uma Sharma and Souvik Mahapatra\*

Department of Electrical Engineering, Indian Institute of Technology Bombay, Mumbai 400076, India \*Phone: +91-222-572-0408, Email: souvik@ee.iitb.ac.in

Abstract— A SPICE compatible model is developed for the time kinetics of linear drain current drift ( $\Delta I_{DLIN}$ ) under Hot Carrier Degradation (HCD) stress in 28 nm Fully Depleted Silicon On Insulator (FDSOI) n-channel FETs having High-K Metal Gate (HKMG) gate stack. The impact of varying the drain (V<sub>D</sub>), gate (V<sub>G</sub>) and body (V<sub>BB</sub>) biases is modeled. The framework is also capable of modeling the channel length (L<sub>CH</sub>) and gate-oxide thickness (Tox) variations. Impact of Self-Heating Effect (SHE) has also been taken into consideration during  $\Delta I_{DLIN}$  modeling.

# Keywords—HCD, FDSOI, HKMG, SHE, gate-oxide thickness, body bias

## I. INTRODUCTION

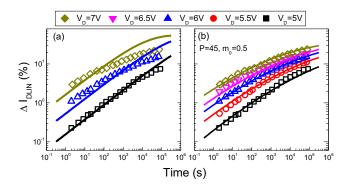

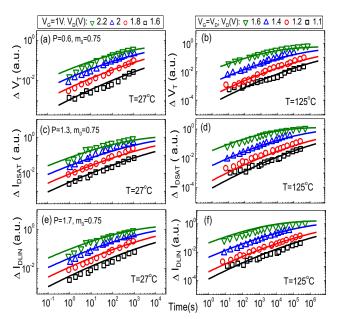

FDSOI MOSFETs are gaining interest for use in IoT and 5G applications. The adaptive body biasing in FDSOI devices can be utilized for dynamic power-performance control [1]. After a brief hiatus, HCD has once again emerged as one of the important and crucial aspects of MOSFET reliability and it impacts both FinFET and FDSOI devices [2]-[9]. HCD causes local damage towards the drain side of the transistor leading to device parametric degradation. Accurate modeling of HCD time kinetics is necessary to extrapolate short time accelerated stress data to determine the HCD magnitude at End-OF Life (EOL) under operating condition. Unlike typical stress condition where  $V_G$  and  $V_D$  are held fixed, in actual digital circuit V<sub>G</sub> and V<sub>D</sub> are varied from 0 to V<sub>DD</sub>. Thus, it is necessary to model the HCD time kinetics under full V<sub>G</sub>/V<sub>D</sub> space [10]. Unlike FinFET, the FDSOI devices use adaptive  $V_{BB}$  to optimize performance and power consumption [1], which also impacts HCD [9] and needs to be modeled. Finally, SHE needs to be carefully modeled in more electrostatically confined architectures (like FinFET and FDSOI) where thermal resistance is much higher than the bulk counterparts [11]. Note that unlike classical HCD, degradation in modern devices show positive temperature (T) activation (increase at larger T) [3]-[5]. The compact model should be SPICE compatible, where the transistor degradation should only depend on V<sub>G</sub>, V<sub>D</sub>, V<sub>BB</sub>, T and time, and not on any device parameter (like I<sub>D</sub> or saturation drain bias (V<sub>DSAT</sub>) etc.). Our previous work has shown, using Eq.(1), the model struggles to predict the measured time kinetics across wide VD and time ranges. Fig.2 (a) plots the prediction of  $V_D$  (using Eq.(1)) dependent IDLIN degradation in time from [13]. Therefore, to improve accuracy, the basic Eq.(1) is modified using a time varying *m* Eq.(2). Fig 1(b) and Fig. 2 shows the modeled time kinetics using the modified equation for planar [10] and Fig. 3 for FinFET [12] devices. The framework is robust to model different probes as V<sub>T</sub>, I<sub>DLIN</sub>, I<sub>DSAT</sub> and CP. Fig. 2 plots the model prediction [10] of time kinetics probed by using (a, b) V<sub>T</sub>, (c, d) I<sub>DSAT</sub> and (e, f) I<sub>DLIN</sub> methods in shorter L<sub>CH</sub> planar devices [14]. The V<sub>D</sub> dependence at various V<sub>G</sub>/V<sub>D</sub> combinations is studied in different L<sub>CH</sub> at room and higher T. The P is listed, which is device and probe specific. Fig. 3 shows the time kinetics of  $\Delta V_T$  during HCD stress at different V<sub>G</sub> and V<sub>D</sub> conditions in SiGe channel p-FinFETs measured by an ultra-fast method and explained using the SPICE compatible compact model.

#### II. SCOPE OF WORK

The developed compact model for planar and FinFET devices [10, 12] is suitably modified for FDSOI MOSFET. It can model the  $\Delta I_{DLIN}$  time kinetics under full  $V_G / V_D / V_{BB}$  space and also model the  $L_{CH}$  and  $T_{OX}$  dependence. In particular, the impact of  $L_{CH}$  and  $T_{OX}$  on the  $V_G$  dependence of HCD can be modeled. The model is validated against measured data from published reports on 28 nm FDSOI technology [6]-[8] and the parameters are listed.

#### III. FRAMEWORK

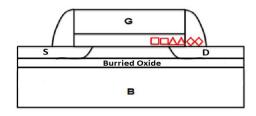

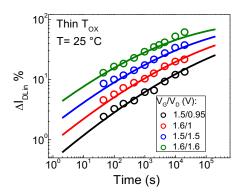

The schematic of a FDSOI MOSFET is shown in Fig. 4 along with localized defects induced by HCD stress in the channel and near drain junction, gate-drain overlap and spacer regions. Threshold voltage and mobility are affected due to the defects in channel, and defects in the overlap and spacer regions impact series resistance. Therefore, defects in all the regions impact drain current. The compact model equations are listed in Table-I. Eq.(1) shows the self-saturating empirical equation to model the HCD time kinetics with a time-varying slope, Eq.(2). Eqs. (3)-(9) govern the modeling of the time-constant  $(\tau)$  that takes into account all the process parameters ( $L_{CH}$  and  $T_{OX}$ ) and the stress conditions ( $V_G$ ,  $V_D$ , V<sub>BB</sub>, and T). Eq.(10) is used for SHE. Fig. 5 shows the measured and modeled time kinetics of  $\Delta I_{DLIN}$  for various V<sub>G</sub>/V<sub>D</sub> conditions for thin gate oxide at room temperature (25°C).

## IV. BODY BIAS DEPENDENCE

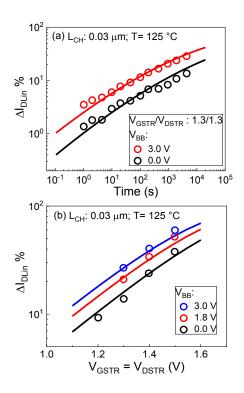

In FDSOI structure, forward body biasing can be done to switch the transistor faster. Fig. 6 (a) and (b) show the measured and modeled forward body bias effect on HCD time kinetics in a device having  $L_{CH}$  of 0.30 µm and thin gate oxide. Fig. 6 (a) shows the time kinetics with varying  $V_{BB}$  and keeping  $V_G$  and  $V_D$  constant. It is observed that degradation increases with increase in  $V_{BB}$ . Fig. 6 (b) shows the fixed time degradation with varying  $V_G$ . It can be modeled using a consistent set of parameters, which are also used in Fig. 7 (a).

#### V. CHANNEL LENGTH DEPENDENCE

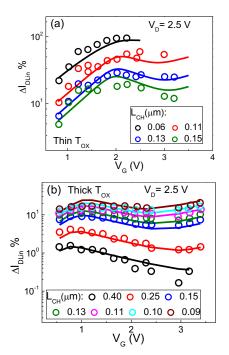

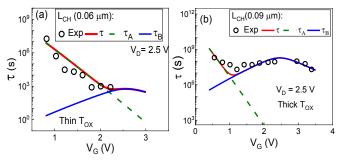

Fig. 7 models the impact of  $L_{CH}$  variation on the  $V_{G}$ dependence of measured  $\Delta I_{DLIN}$  (V<sub>D</sub> is held fixed) at a fixed stress time for thin and thick oxide devices. Note that the V<sub>G</sub> dependence is different for thick and thin oxide devices. Fig. 7 (a) shows the  $V_{G}$  dependence changes from bell shape to monotonic with decreasing  $L_{CH}$  for thin gate oxide. However, in Fig. 7 (b) the effect is reversed with  $L_{CH}$  for thick gate oxide. It can be seen that the model is capable of explaining both trends with consistent model parameters, which are listed in Table-II. Note that the difference in V<sub>G</sub> dependence of  $\Delta I_{DLIN}$  for thin and thick oxide devices is due to difference in V<sub>G</sub> dependence of the sub-components of time constant  $(\tau)$ as shown in Fig.8 (a) and (b):  $\tau_A$  monotonically reduces while  $\tau_{\rm B}$  increases first and later reduces as VG is increased and they control the overall  $\tau$  and HCD lifetime. For thick gate oxide device,  $\tau_A$  is dominant till  $V_G = V_D/2$  while for thin gate oxide it is significant till  $V_G = V_D$ , which are the well-known worse case conditions for each cases [10]. Also, the model helps to explain the L<sub>CH</sub> scaling keeping same gate process. Model parameters are listed in Table-II.

## VI. OXIDE THICKNESS

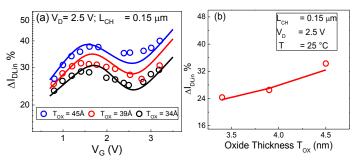

Measured HCD data from different  $T_{OX}$  devices are modeled using a consistent set of parameters at a fixed L<sub>CH</sub>. Fig. 9 shows the measured and modeled data for gate oxide thickness variation at 0.15 µm channel length. Thus, the model can help in providing the complete modeling and thus helps in the study of gate-oxide scaling as well.

#### VII. CONCLUSION

A compact HCD time kinetics model is proposed and validated using measured data from 28 nm FDSOI devices. The model is fully SPICE compatible, as it only uses terminal voltages and T, and does not depend on any internal transistor parameter. It can model data over the full VG/VD spectrum (for  $V_G <$ , = and >  $V_D$ ); different T (including SHE as applicable),  $V_{BB}$ , and can also handle technology parameter ( $L_{CH}$  and  $T_{OX}$ ) changes. In particular, it is observed that  $L_{CH}$  scaling results in different  $V_G$  dependence of measured  $\Delta I_{DLIN}$  at fixed time for thick and thin  $T_{OX}$  devices, which is explained. The model can be incorporated in a SPICE simulator to model HCD in actual circuits under different mission profiles.

#### VIII. REFERENCE

- "FDSOI Technology and Dynamic Body Bias Compensation to Enable Next Generation AI/IoT and Automotive Products – An industrial perspective" V. Huard, tutorial, 2019 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, 2019.

- [2] S. Ramey et al., "Intrinsic transistor reliability improvements from 22nm tri-gate technology," 2013 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, 2013, pp. 4C.5.1-4C.5.5. doi: 10.1109/IRPS.2013.6532017

- [3] H. Jiang, S. Shin, X. Liu, X. Zhang and M. A. Alam, "Characterization of self-heating leads to universal scaling of HCI degradation of multifin SOI FinFETs," 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, 2016, pp. 2A-3-1-2A-3-7. doi: 10.1109/IRPS.2016.7574506

- [4] A. Kerber, S. Cimino, F. Guarin and T. Nigam, "Assessing device reliability margin in scaled CMOS technologies using ring oscillator circuits," 2017 IEEE Electron Devices Technology and Manufacturing Conference (EDTM), Toyama, 2017, pp. 28-30. doi: 10.1109/EDTM.2017.7947495

- [5] Y. Qu et al., "Ultra fast (<1 ns) electrical characterization of selfheating effect and its impact on hot carrier injection in 14nm FinFETs," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, Dec. 2017, pp. 39.2.1-39.2.4. doi: 10.1109/IEDM.2017.8268520.

- [6] W. Arfaoui, X. Federspiel, P. Mora, M. Rafik, D. Roy and A. Bravaix, "Experimental analysis of defect nature and localization under hotcarrier and bias temperature damage in advanced CMOS nodes," 2013 IEEE International Integrated Reliability Workshop Final Report, South Lake Tahoe, CA, 2013, pp. 78-83. doi: 10.1109/IIRW.2013.6804163

- [7] W. Arfaoui, X. Federspiel, A. Bravaix, P. Mora, A. Cros and D. Roy, "Application of compact HCI model to prediction of process effect in 28FDSOI technology," 2014 IEEE International Integrated Reliability Workshop Final Report (IIRW), South Lake Tahoe, CA, 2014, pp. 69-72. doi: 10.1109/IIRW.2014.7049513

- [8] W. Arfaoui et al., "Energy-driven Hot-Carrier model in advanced nodes," 2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, 2014, pp. XT.12.1-XT.12.5. doi: 10.1109/IRPS.2014.6861189

- [9] Federspiel, X., Angot, D., Rafik, M., et al. (2012) 28 nm Node Bulk vs FDSOI Reliability Comparison. 2012 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, 15-19 April 2012, 3B.1.1-3B.1.4.

- [10] U. Sharma and S. Mahapatra, "A SPICE Compatible Compact Model for Hot-Carrier Degradation in MOSFETs Under Different Experimental Conditions," in IEEE Transactions on Electron Devices, 2019. doi: vol. 66, no. 2, pp. 839-846, Feb. 2019.

- [11] C. Prasad et al., "Self-heat reliability considerations on Intel's 22nm Tri-Gate technology," 2013 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, 2013, pp. 5D.1.1-5D.1.5. doi: 10.1109/IRPS.2013.6532036

- [12] U. Sharma, N. Parihar and S. Mahapatra, "Modeling of HCD Kinetics for Full V<sub>G</sub>/V<sub>D</sub> Span in the Presence of NBTI, Electron Trapping, and Self Heating in RMG SiGe p-FinFETs," in *IEEE Transactions on Electron Devices*, vol. 66, no. 6, pp. 2502-2508, June 2019. doi: 10.1109/TED.2019.2911335

- [13] J. Goo, Y. Kim, H. L'Yee, H. Kwon and H. Shin, "An analytical model for hot-carrier-induced degradation of deep-submicron n-channel LDD MOSFETs," in *1995 Solid-State Electronics*, 38(6), pp.1191-1196. DOI: <u>10.1016/0038-1101(94)00221-Z</u>

- [14] D. Varghese, M. A. Alam and B. Weir, "A generalized, IBindependent, physical HCI lifetime projection methodology based on universality of hot-carrier degradation," in *Proc. Int. Rel. Phys. Symp* 2010, pp. 1091-1094. **DOI:** <u>10.1109/IRPS.2010.5488666</u>

Fig.1. Modeling of measured  $\Delta I_{DLIN}$  time kinetics at different  $V_D$  for on-state HCD stress (data from [13]) using standard and modified compact models. Further details [10].

Fig.2. Modeling of V<sub>D</sub> dependence of measured (a, b)  $\Delta V_T$ , (c, d)  $\Delta I_{DSAT}$  and (e, f)  $\Delta I_{DLIN}$  time kinetics at (a, c, e) room and (b, d, f) high T from planar devices at low V<sub>D</sub> stress [14]. Further details [10].

Fig.3. Time kinetics of measured and modeled  $\Delta V_T$  at different stress  $V_D$  but for  $|V_G| = |V_D|$  condition in SiGe devices (a) FF\_A (Low N%, L<sub>CH</sub>= 20 nm), (b) FF\_B (High N%, L<sub>CH</sub>= 20 nm) and (c) FF\_C (High N%, L<sub>CH</sub>= 60 nm) devices. Symbols: data, lines: model. In (d), the  $V_D$  dependence of the parameter  $\tau$  (see Eq. (1) and Eq. (2), Table-I) is identical for all three devices. Further details [12].

Fig 4. Schematic of a FDSOI MOSFET showing regions along the channel that get degraded during HCD: square (channel), triangle (gate/drain overlap) and diamond (spacer).

Fig. 5. Time evolution of experimental  $\Delta I_{DLIN}$  (in %) for DC stress, with model prediction at different  $V_G$  and  $V_D$

## TABLE I. COMPACT MODEL EQUATIONS

$$\Delta P = P[1 - e^{\left\{-\left(\frac{t}{\tau}\right)^{m}\right\}}] \tag{1}$$

$$m - m e^{\left[-\left(\frac{t}{\tau}\right)^{k}\right]} \tag{2}$$

$$n = m_0 e^{-1} m_0 e^{-1} m_0 e^{-1} e^{-1$$

$$\tau_{A} = \frac{A}{e^{\Gamma_{A2}(V'_{D})}} e^{\Gamma_{A1}(V'_{D} - \alpha V_{G})}$$

(3)

(4a)

$$\tau_B = \frac{B}{2} e^{\Gamma B_1 (V_G - \beta V'_D)} \tag{4b}$$

$$C = [1 + C_1 e^{\Gamma C_1 (V_G - \sigma V'_D)}] e^{(\Gamma C_2 V'_D)}$$

(5)

$$V'_{D} = V_{D} + (\chi * V_{BB});$$

(6)

$q = q_{0} * T_{cu};$  (7a)

$$\Gamma_{R1} = \Gamma_{R10} * e^{-(Tox*s1)};$$

(7b)

$$\Gamma_{C1} = \Gamma_{C10} * T_{ox}^{(s2)}; (7c)$$

$$A = A_1 e^{(\frac{-Ea_A}{kT})}, B = B_1 e^{(\frac{-Ea_B}{kT})}$$

(8)

$$A_{1} = A_{2} L_{CH}^{(AA)}, B_{1} = B_{2} L_{CH}^{(AB)}, C_{1} = C_{2} L_{CH}^{(Ac)}$$

(9)

$$T = T_{SHE} + T_{CHIICK}, T_{SHE} = \Theta V_{G} V_{D}$$

(10)

$\Delta P$ : device parameter shift,

P: Model parameter related to maximum degradation, t: stress time,  $\tau$ : related to bond dissociation rate, m: governs the kinetics at early time before the onset of saturation Fixed Parameters:  $m_0 = 0.5$ ;  $\tau_m$  (s) = 1e4; k = 0.036;  $\chi = 0.08$ ; s1 = 0.1; s2 = 0.5;  $\Gamma_{A1}$  (V<sup>-1</sup>) = 4.5;  $\Gamma_{A2}$  (V<sup>-1</sup>) = 17.6;  $E_{A\_HC}$  (eV) = 0.4;  $\beta = 0.5$ ;  $E_{B\_HC}$  (eV) = 0.4;  $\sigma = 1$ ;  $\Gamma_{C2}$  (V<sup>-1</sup>) = 6.96;

Adjustable Parameters:

|                                                      | Fig 4a | Fig 4b | Fig 5 |

|------------------------------------------------------|--------|--------|-------|

| A2*                                                  | 1      | 0.4    | 1e-5  |

| $\alpha/\alpha_0$                                    | 2      | 2.5    | 0.027 |

| B2*                                                  | 1      | 1e3    | 1e-1  |

| $\Gamma_{\rm B}/\Gamma_{\rm B0}({ m V}^{-1})$        | 2      | 1.7    | 60    |

| C2*                                                  | 1      | 10     | 10    |

| Γ <sub>C1</sub> /Γ <sub>C10</sub> (V <sup>-1</sup> ) | 6      | 5.8    | 35    |

\*values are normalized to thin gate oxide parameters. Data for thick and thin oxide are normalized to different values in referenced paper.

Fig. 6. Modeling of  $V_{BB}$  stress impact over  $I_{DLIN}$  drift in thin gate-oxide (a) time kinetics over classical HCI stress with FBB stress for (b) over voltage stress where  $V_G=V_D$  with and without FBB at fixed time.

Fig. 7. Modeling of channel length dependence. (a) thin gate-oxide and (b) thick gate oxide. (a, b) shows varying channel length across  $V_G$ . Parameters are shown in Table II.

Fig. 8. Contribution from different  $\tau$  subcomponents. (a) thin gateoxide and (b) thick gate oxide. (b) shows varying channel length across VG. Parameters are shown in Table II.

Fig. 9.  $I_{DLIN}$  drift modeling over gate voltage stress for (a) several gate-oxide thickness at fixed channel length (b) several gate-oxide thickness at fixed condition  $V_G=V_D$ .