# Simulation Based DC and Dynamic Behaviour Characterization of Z2FET

<u>F. Adamu-Lema</u><sup>+</sup>, M. Duan<sup>+</sup>, C. Navaro<sup>++</sup>, V. Georgiev<sup>+</sup>, B. Cheng<sup>\*</sup>, X. Wang<sup>\*</sup>, C. Millar<sup>\*</sup>, F. Gamiz<sup>++</sup>, A.Asenov<sup>\*+</sup>

<u>Fikru.adamu-lema@glasgow.ac.uk</u>, School of Engineering, University of Glasgow, Scotland, Glasgow, G12 8LT, UK

+ University of Glasgow, <sup>++</sup>University of Granada \*Synopsys, 133 Finnieston street, Glasgow G3 8HB, UK

Abstract: This work presents a TCAD investigation of the operation of a Z2FET device for memory application, where the TCAD model is well calibrated to experimental hysteresis curves. The DC operation of the Z2FET has been analyzed for 4 cases, based on the permutations of the front and back gate biases, to identify and compare different modes of operation. The memory mode of operation is under the "thyristor" like scenario with positive and negative biases applied to the front and back gates respectively. The dynamic property of Z2FET as a memory device is shown and its working mechanism is described.

Keywords: Hysteresis; 1T-DRAM; Thyristor, DRAM; partioning; Z2FET

### I.INTRODUCTION

The Z2FET architecture is particularly complex and its operation has promise for application in memory cells without connection to external charge storage components-1T-DRAM [1][2]. Since its inception [3 -6] and experimental demonstrations [7][8], important progress has been made in analyzing its transient properties through experimental characterization. However, the carrier dynamics and device operation within the distinct sections of the device under DC operation is still not well understood. This paper describes the DC characterization of Z2FET from different angles, including a brief description of its transient (dynamic) properties. In this work, we mainly concentrate our discussions on how the current-voltage characteristics behave in different bias conditions or modes of operations. Also answer the question what the carrier distributions looks like during the operation of the device?

## II. TCAD CALIBRATION AND METHODOLOGY

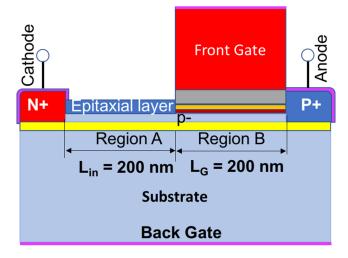

The Synopsys TCAD tool Sentaurus Structure editor and Device simulator [9] were used to design the device and perform the device simulation respectively. The schematic of device structure is illustrated in Fig.1. For this work, we focused on the smaller device data available at the time of the calibration process. Ungated region (Region A) is 200nm in length and the SOI (Region B) section is 200 nm as well. All-important dimensions used in the device structure are documented in Table 1. The channel doping is very low, which gives

a configuration like the P-i-N diode [10]. The nominal back gate ( $V_{BG}$ ) and front gate ( $V_{FG}$ ) bias conditions used for calibration of the TCAD deck are -1.0V and 1.2V respectively. The cathode voltage ( $V_K$ ) is kept at 0 V while sweeping the anode voltage ( $V_A$ ). The mobility and SRH recombination and generation models are calibrated against the experimental  $I_a$ - $V_a$  data so that the simulation deck can reproduce the hysteresis curve at the nominal biasing conditions.

The systematic calibration is organized in such a way that it will achieve an accurate matching of the simulation result with the experimental data. This was done through sensitivity analysis of  $I_a$ - $V_a$  curves with different front gate voltages and various mobility model parameters. During the sensitivity analysis, we also probed the effect gate work function  $(\phi_m)$  to see how it impact the memory window. Since carrier lifetime plays important roles in determining hysteresis, various carrier life time  $(\tau_{e,h})$  values have been used in the SRH recombination and generation model during the calibration process inorder to guage the behaviour of the hysteresis width. For completeness, we also activated the band to band tunneling (B2BT) model during the calibration stage although it contributes slightly. However, it doesn't modify the hysteresis window, which means B2BT has no significant effect on Z2FET operation.

Fig. 1 Illustration of used device structure with Lin=Lg=200 nm

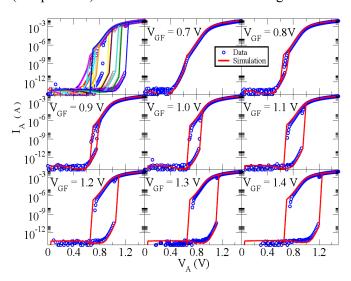

Finally, Fig. 2 shows a good agreement between the TCAD simulation and experimental data. Following calibration of the model, the TCAD deck was used as the basis for all subsequent simulations, which differ through the variation of  $V_{FG}$  and  $V_{BG}$  as required.

| Table 1: | Important : | phys | ical | and | doning | information |

|----------|-------------|------|------|-----|--------|-------------|

|          |             |      |      |     |        |             |

| Parameter                     | Value                  | Parameter          | Value                               |  |

|-------------------------------|------------------------|--------------------|-------------------------------------|--|

| $L_{g}$                       | 200 nm                 | t <sub>ox-HK</sub> | 1.785 nm                            |  |

| Lin                           | 200 nm                 | tBox               | 25 nm                               |  |

| t <sub>epi</sub>              | t <sub>epi</sub> 15 nm |                    | 1x10 <sup>15</sup> cm <sup>-3</sup> |  |

| tsi                           | 7 nm                   | Ns/D               | 5x10 <sup>20</sup> cm <sup>-3</sup> |  |

| t <sub>ox-SiO2</sub> 0.711 nm |                        | N <sub>BG</sub>    | 1x10 <sup>18</sup> cm <sup>-3</sup> |  |

## III. Z2FET OPERATION AND ANALYSYS

## A. Operation

As a device, the operation mechanism of Z2FET is manifested on the positive feedback mechanism [11][12] which is triggered because of a chain of carriers' injections. The increase in  $V_A$  increases injections of holes from the anode (which is the drain) towards source region. The increase in drain bias reduces the potential barriers formed by  $V_{BG}$ . The injection of holes across the channel initiate the return injection of electron from the source (Cathode) back to the two channel regions, which reduces  $V_{FG}$ . These cascades of injections of electrons, holes and the near collapse of the two barriers lead to an abrupt increase (sharp switch) of drain current as shown in Fig. 2

Fig. 2 Calibration of TCAD stationary simulation. Points are from experimental data and lines are simulation results. In all cases the carrier life time are the same for electrons, ( $\tau_{maxh}=3\times10^{-8}\,s$ ) and for holes, ( $\tau_{maxh}=5\times10^{-9}\,s$ ). The back-gate voltage is fixed to -1.0 V and the cathode terminal is grounded.

As shown in Fig. 2, the hysteresis window depends on the level of  $V_{GF}$  applied among other deciding factors. High  $V_{GF}$  shifts the triggering point of the drain voltage  $(V_{ON})$  to the right. This is the point where the

drain current exhibit sharp increase. On the other hand, the reverse sweep remains practically unchanged. Applying large  $V_{GF}$  will enhance the memory window. The main drawback of increasing the front gate voltage is the power consumption.

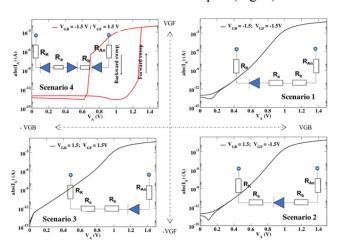

## B. Z2FET Operation Based Partition

Observing from another angle, the above description of Z2FET device operation mechanism can also be understood by a systematic partitioning of the overall process into 4 biasing regions assuming the scenarios in Table 1 under the listed polarities of  $V_{BG}$  and  $V_{FG}$ . These partitions used throughout this work will enhance the understanding of Z2FET functionality under different bias conditions. The possible partitions, based on the possible permutations of the front and back gate bias, is illustrated in Fig. 3.

Table 1 Possible scenarios during Z2FET operation:

| $V_{BG}\left( V\right)$ | V <sub>FG</sub> (V) | Cathode | Region A | Region B | Anode | Scenarios                       |   |  |

|-------------------------|---------------------|---------|----------|----------|-------|---------------------------------|---|--|

| -                       | -                   | n       | p        | p        | p     | D R <sub>A</sub> R <sub>B</sub> | 1 |  |

| +                       | -                   | n       | n        | p        | p     | R <sub>h</sub> R <sub>n</sub>   | 2 |  |

| +                       | +                   | n       | n        | n        | p     | R <sub>A</sub> R <sub>B</sub>   | 3 |  |

| -                       | +                   | n       | p        | n        | p     | D R <sub>A</sub> R <sub>B</sub> | 4 |  |

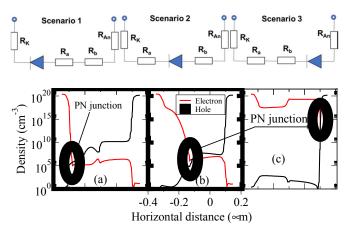

From the list of scenarios given in Table 1, the Z2FET operates as memory device only in one of them, which is listed as scenario 4. In the remaining three cases, the DC behaviour replicates that of a diode with the combination resitance in Region A&B and the contact (access) resistances,  $R=R_{CI}+R_{C2}+R_A+R_B$ . The back-bias  $V_{BG}$  and the front gate bias  $V_{GF}$  can influence the values of  $R_A$  and  $R_B$  and change the position of the diode in the Z2FET structure as depicted in Fig 6. Therefore, combinations of  $V_{BG}$  and  $V_{GF}$  can create one (in three different location) or three diodes as in Fig 4.

For example, in *scenario 1*, The negative gate bias creates accumulation of holes in the gated channel region. This lead to the lowering of the resistivity of the SOI channel region ( $R_B$  decreases) thus the forward diode current increases. For  $V_{BG} >> 0$  and  $V_{FG} < 0$  bias condition, namely scenario 2, the access epitaxial region (ungated) will be inverted and the two diodes will disappear as a result. As shown in Table 1, for scenario 3, the biasing condition is  $V_{BG} >> 0$  and  $V_{FG} >$ 0. At this condition, the epitaxial region and the gated SOI region are inverted creating an N-n-n-P configuration and the two diodes disappear leaving the one near the neighbourhood of the anode contact. In scenario 4, namely the hold state, the gated channel is biased at inversion mode and the epitaxial access region is biased at accumulation mode. In this condition, we will have alternating regions of N-p-n-P configuration in the thin silicon body resulting in three p-n junction formation, hence three diodes as shown in Fig.3. This resembles a "thyristor", [11][12] represented as a back to back bipolar transistors.

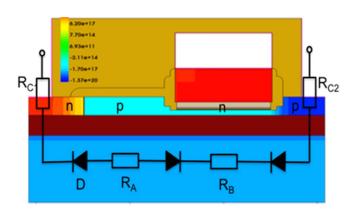

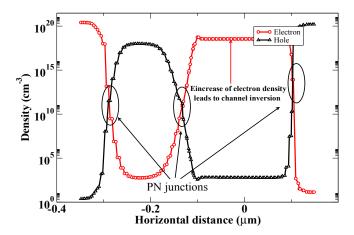

The carrier distribution for this configuration (scenario 4) indicate that three p-n junction regions (Fig. 5 circled) are formed for a bias condition of  $V_{BG}$  << 0 and  $V_{FG}$  >> 0. As expected, the DC characteristics in this case exhibit hysteresis (Fig. 2). On the other hand in Fig. 6 the carrier density plot shows a single p-n junction coresponding to scenario I (a), scenario I (b), and scenario I (c). The representative ("equivalent") circuit are illustrated in Fig.6(top), where the diodes are placed in three different position of the Z2FET during its operation phase. The location of the three diods is reflected in the carrir distribution plot (Fig. 6).

Fig.3 Partisioned regions of  $Z^2FET$  and corresponding  $I_A$ - $V_A$  characteristics, of proposed Cenarios. Arange of  $V_{FG}$  and  $V_{BG}$  between (+/-1.5: +/-1.5) V is used in the simulations. Only simulations from the boundary values of the range are shown

Fig. 4 Possible working state of  $Z^2FET$  as a memory device for  $V_{FG} >> 0$  and  $V_{BG} << 0$ . At this phase of operation, the devise forms an N-p-n-N configuration by inverting the two channel regions. The three P-N junctions form a representative "equivalent circuit" with 3 diodes and resister elements.

The carrier distribution is constantly evolving (changing) in the system during the operation phase, and it is hard to estabilish the condition and position of the diodes. However, visualising both electron and hole carrier distributions, which are extracted from the cross-section along the longtudnal direction of the device as shown in Fig. 5 and Fig. 6, clearly indicate

that the formation of the metalergical junctions. These are the points where the diodes likely be located at a specific bias condion.

Fig 5. Carrier distribution extracted at the same bias conditions as in the conditions where the device state of operation three diodes

Fig 6. Carrier density plot showing the PN junctions and the circuit representation involving the diods and resistors are illustrated top. The three Diodes are placed in different positions of the  $Z^2$ FET during its operation pheses. The coresponding carrier density profiles of scenario1, scenario 3, and scenario 3 are illustrated in (a), (b) and (c) respectivly.

# C. Memory operation

The Z2FET operates as a memory device only under scenario 4, where *n-p-n-p* configuration has been established in the device. Only this bias condition allows Z2FET to perform a fast switching in combination with appropriate hysteresis width.

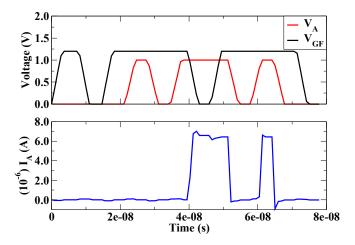

The waveforms shown in Fig. 7 are chosen to study the operation of the Z2FET as a memory device, where it is understood that successful DRAM operation requires the right bias condition and is sensitive to timing. All expected normal operations including program '0' (P0), hold '0' (H0), read '0' (R0), program '1' (P1), hold '1' (H1), and read '1' (R1) are covered in the simulation trace where the complete operation cycle is presented in Fig. 6. The dependence of  $I_A$  – as a function of time (*time-diagram*) is given in Fig. 7. This

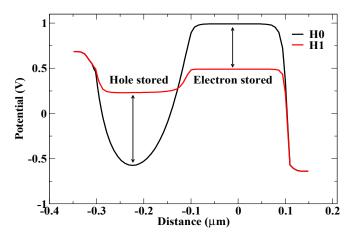

shows the typical output result of the memory operation of the Z2FET. Furthermore, when '1' is written as shown in Fig. 8 the holes are stored under the ungated region and electrons are stored under the gated SOI region. This lowers the potential barrier and allows injection of further holes into the ungated epitaxial access region when  $V_A$  is lifted.

Fig. 7 Waveform for  $Z^2FET$  used as DRAM device. As shown in (left), both '1' and '0' can be successfully written in and read out on this device when biased at scenario 2 (in this example,  $V_{FG}$ =1.2 V and  $V_{BG}$  = -1.0 V are applied).

Fig. 8 shows where the stored information is located with respect to the potential distribution in the system.

## IV. CONCLUSION

The operation of the Z2FET when biased to act as a memory device has been investigated. The main operation bias points of Z2FET have been analyzed. From DC operation point of view, 4 *scenarios* have been considered based on a given domain of both  $V_{BG}$  and  $V_{BF}$ . The switching condition of Z2FET emulate like a *Thyristor* when  $-V_{BG}$  and  $+V_{GF}$  bias conditions are meet. The dynamic property of Z2FET as a memory device and it's working mechanism has been described.

#### ACKNOWLEDGMENT

This research work is funded under the EU Horizon-2020 project, Revolutionary Embedded Memory for INternet of Things Devices and Energy Reduction (REMINDER). We also would like to thank INPG for providing the experimental data.

#### REFERENCES

- [1] N. Rodriguez, S. Cristoloveanu, F. Gamiz, , "Novel Capacitorless 1T-DRAM Cell for 22-nm Node Compatible With Bulk and SOI Substrates", *Transactions on Electron Devices*, Vol. 58, NO. 8, August 2011

- [2] Cheng-Wei Cao, Song-Gan Zang, Xi Lin, Qing-Qing Sun, Charles Xing, Peng-Fei Wang, and David Wei Zhang, "A Novel 1T-1D DRAM Cell for Embedded Application", *IEEE Transactions on Electron Devices*, Vol. 59, NO. 5, May 2012

- [3] J. Wan, S. Cristoloveanu, C. Le Royer, A. Zaslavsky, US Patent number US 20130069122 A1

- [4] J. Wan, C. Le Royer, A. Zaslavsky, and S. Cristoloveanu, "A systematic study of the sharp-switching Z2-FET device: From mechanism to modeling and compact memory applications," *Solid. State. Electron.*, vol. 90, pp. 2–11, 2013.

- [5] J. Wan, C. Le Royer, A. Zaslavsky and S. Cristoloveanu, "Z2-FET: A zero-slope switching device with gatecontrolled hysteresis", VLSI-TSA, 23-25 April 2012

- [6] J. Wan, C. Le Royer, A. Zaslavsky, and S. Cristoloveanu, "A Compact Capacitor-Less High-Speed DRAM Using Field Effect-Controlled Charge Regeneration", *IEEE Transactions on Electron Letters*, VOL. 33, NO. 2, February 2012

- [7] J. Wan, C. LeRoyer, A. Zaslavsky and S. Cristoloveanu. "A systematic study of the sharp-switching Z2-FET device: From mechanism to modeling and compact memory applications". Solid-State Electronics, 90, pp. 2-11, 2013.

- [8] REMINDER Project: (Accessed on 30/06/2017) http://www.reminder2020.eu.

- [9] Synopsys Sentaurus Device User Guide, Version K-2015.

- [10] M. Caulton, et al, "PIN Diodes for Low-Frequency High-Power Switching Applications," *IEEE Transactions on Microwave Theory & Techniques*, Vol MTT-30, No 6, June 1982, pp 875-882

- [11] C.W. Mueller, J. Hilibrand, "The "Thyristor" A new high-speed switching transistor", *IEEE Transactions on Electron Devices*, Volume: 5, Issue: 1, Jan. 1958

- [12] D.J. Roulston, M.R. Nakhla, "Efficient modeling of thyristor static characteristics from device fabrication data", *IEEE Transactions on Electron Devices*, Volume: 26, Issue: 2, Feb. 1979