# A SPICE-compatible model of SG-MONOS for 28nm flash macro design considering the parasitic resistance caused by trapped charges

Risho Koh, Mitsuru Miyamori, Katsumi Tsuneno, and Tetsuya Muta

Elemental technology development division2 Renesas System Design Co., Ltd. Kodaira-shi, Tokyo, Japan risho.koh.vj@renesas.com

Abstract— A SPICE-compatible model for the read current of split-gate MONOS (SG-MONOS) cell has been developed for 28nm embedded flash macro design. The influence of trapped charges on the read current has been analyzed by using TCAD. It has been found that trapped charges located on top of the gap region strongly decrease the cell current. It has been also found that the shape of  $I_d$ - $V_{\rm sg}$  curve changes drastically depending on the positon of trapped charge and trap density. This paper proposes a new model which reproduces the above behavior by using a synthesis of several resistances in which every resistance changes its value exponentially to the gate voltage. The model shows an excellent fitting accuracy for 28nm generation cell.

Keywords—SPICE; compact model; MONOS; Split-gate; flash

## I. INTRODUCTION

SG-MONOS is an attractive flash memory cell structure since it provides a high-speed operation, a low power operation, and a long retention [1-4]. In this work, we report a spice-compatible model of SG-MONOS cell read currents which is required for designing circuits of SG-MONOS memories.

Although elaborated SPICE-compatible models for floating split-gate cells have already been published [5-7], the SG-MONOS has not fully modeled yet. A gap resistance which is modified by trapped charges is an issue for modeling such a split-gate charge-trap memory. This paper reports a novel model for the SG-MONOS cell in which a gap resistance is approximated by a synthesis of several resistances whose value are exponentially depending on the select gate voltage. The model has been verified by using measurements of read current of 28nm generation SG-MONOS cell. The proposed model accurately reproduces the cell current in all conditions.

# II. DEVICE STRUCTURE AND THE GOAL OF MODELING

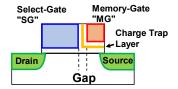

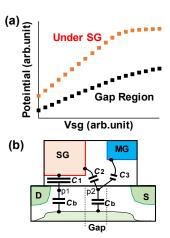

Fig. 1 shows the device structure of SG-MONOS cell [1-4]. A charge trapping layer are placed under the memory gate (MG). In the program condition, electrons are injected to the charge trapped layer (Fig. 2(c)). This makes the threshold voltage of MG transistor high. A datum "0" is stored in this condition. In the erase condition, the trapped electrons are erased and the threshold voltage of MG transistor becomes low

Yoshiyuki Kawashima MCU Device Technology Dept. Renesas Electronics Corporation Hitachinaka-shi, Ibaraki, Japan

Fig. 1 The device structure of Split-Gate (SG) MONOS cell.

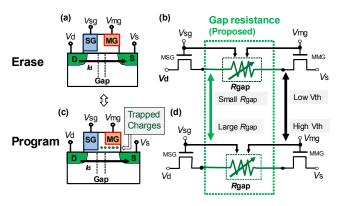

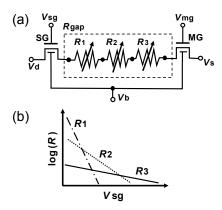

**Fig. 2** The strategy of SG-MONOS read current modeling.  $R_{\rm gap}$  is the gap resistance whose value is dependent on  $V_{\rm sg}$  and  $V_{\rm mg}$ .  $R_{\rm gap}$  also changes between the program condition model and the erase condition model.

(Fig. 2(a)). This is the condition that a datum "1" is stored. A select-gate (SG) transistor operates as a cell selector. A gap is located between SG and MG. The gap region is not covered by any electrodes.

SPICE models which reproduce the cell currents are required both for the erase condition and program condition. Basic method to obtain the two models for split gate memories is to change the threshold voltage parameter of MG transistor. However, the approach cannot reproduce the influence of parasitic resistance in the gap region of SG-MONOS cell ( $R_{\rm gap}$  in Fig. 2). The parasitic resistance strongly affects the cell current especially in the program condition in which trapped charges exist. In addition, the effect becomes significant as the cell is miniaturized. The purpose of this paper is to develop a cell model for SG-MONOS which can reproduce not only the influence of the threshold voltage variation of MG transistor, but also the influence of the parasitic resistance variation due to the change in the trapped charge density, as shown in Fig. 2.

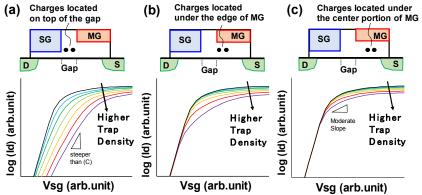

**Fig. 3** Simulated  $I_d$ - $V_{sg}$  characteristics obtained from TCAD.

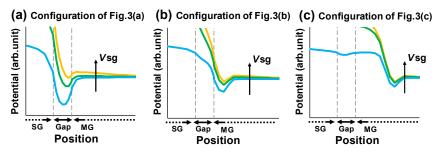

Fig. 4 The horizontal potential distribution at the silicon surface obtained from TCAD. (a), (b), and (c) are plotted for configurations shown in Fig. 3(a), (b), and (c), respectively. Potential distributions for the highest trap density in Fig. 3 are shown.

### III. TCAD ANALYSIS TO FIND MODELING STRATEGY

The influence of trapped charge on the drain current is analyzed by using TCAD. Simplified device structures with a constant doping and abrupt junctions are assumed, since the purpose of TCAD simulation is to obtain a qualitative insight. Fig. 3 shows simulated result of the drain current  $(I_d)$  dependences on the select gate voltage  $(V_{sg})$ . In the structure (a), trapped charges are located over the gap region. The charges are located under the edge of MG in (b), and the charges are located under the center portion of MG in (c).

The influence of trapped charge density on the  $I_{\rm d}$ - $V_{\rm sg}$  curve is significant in the arrangement of Fig. 3(a). The drain current decreases and the subthreshold slope becomes moderate as the trap density increases. In the case (c), no changes in the subthreshold current are observed. The  $I_{\rm d}$ - $V_{\rm sg}$  curve of case (c) suggests that the main reason for the  $I_{\rm d}$  degradation in the case is due to the change in the channel resistance of MG transistor which is serially connected with SG. However, the  $I_{\rm d}$ - $V_{\rm sg}$  curve of case (c) does not resemble the measurements (see Fig. 9 (b)). The result for case (b) shows an intermediate behavior between Fig. 3(a) and (c).

Fig. 4 shows the horizontal electric potential distribution at the silicon surface. Fig. 4 (a), (b), and (c) are plotted for configurations shown in Fig. 3 (a), (b), and (c), respectively. The potential distributions for the highest trap density in Fig. 3 are plotted in the figure. One can see that a large potential dip appears in the Fig. 4 (a). This shows a large parasitic resistance exists in the gap region. Fig. 5(a) shows the potential dependence on  $V_{\rm sg}$  at silicon surface for the configuration of

Fig. 5 (a) Potential dependence on  $V_{\rm sg}$  at silicon surface. The results are shown for the highest trap density configuration of Fig. 3(a). (b) Virtual capacitance networks to explain the difference between two slopes in Fig. 5(a).

Fig. 3(a). The electric potential at the gap region are compared with that under the select gate. The result shows that the sensitivity of surface potential to  $V_{\rm sg}$  at the gap region is weaker than that under SG. This behavior can be explained by virtual capacitance networks shown in Fig. 5(b). The gap region has electrostatic coupling with SG (shown by  $C_2$ ). However, the influence of  $V_{\rm sg}$  on the electric potential of gap region is small, since the capacitive coupling at the gap region  $(C_2)$  is smaller than that under SG  $(C_1)$  and the coupling capacitance with MG  $(C_3)$  exists in the gap region.

## IV. MODEL CONFIGURATION AND PARAMETER FITTING

Fig. 3 suggests that the shape of  $I_d$ - $V_{sg}$  curve is dependent on the spatial distribution of trap density. However, it is difficult to know the actual distribution of trapped charges, and it is also difficult to include an actual spatial distribution in the model equation even if the distribution is found.

Therefore, an approximation has been developed based on the analysis discussed in the section III. Fig. 6(a) shows the proposed macro model configuration for SG-MONOS Cell.  $R_{\text{gap}}$  is approximated by a composition of three variable resistances  $R_1$ ,  $R_2$ , and  $R_3$ . SG and MG transistors are modeled by using BSIM4. Rgap is expressed as in (1) and (2), by using coefficients  $A_n$  which are functions of memory gate voltage

Fig. 6 Proposed macro model for SG-MONOS Cell. (a) Model configuration. (b) The relation among the value of three variable resistances  $R_1$ ,  $R_2$ , and  $R_3$ . The parasitic resistance of the device ( $R_{gap}$ ) is approximated by a composition of  $R_1$ ,  $R_2$ , and  $R_3$ . SG transistor and MG transistor are modeled by using BSIM4.

$(V_{\rm mg})$  and temperature.  $B_{\rm n}$  and  $C_{\rm n}$  in (2) are fitting parameters determined at a reference  $V_{\rm mg}$  and a reference temperature.

$$R_{\rm gap} = \sum_{\rm n=1}^{3} R_{\rm n}$$

(1)

$$R_{\rm n} = A_{\rm n} \exp(B_{\rm n} V_{\rm sg} + C_{\rm n})$$

(2)

$$R_{\rm n} = A_{\rm n} \exp \left( B_{\rm n} V_{\rm sg} + C_{\rm n} \right) \tag{2}$$

The relations among the three resistances  $R_1$ ,  $R_2$ , and  $R_3$  are shown in Fig. 6(b).  $R_2$  has a weaker dependence on  $V_{sg}$  than  $R_1$ does, and  $R_3$  has a weaker dependence on  $V_{sg}$  than  $R_2$  does. The parasitic resistance dependence on  $V_{\rm sg}$  in an actual device is approximated by a synthesis of the three resistances.

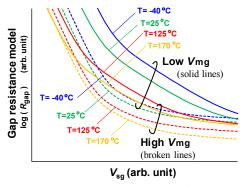

Fig. 7 shows the modeled  $R_{\rm gap}$  for program condition. The configuration shown in Fig. 6 is used. The coefficients for  $R_1$ ,  $R_2$ , and  $R_3$  have been determined from measured cell currents.  $R_{\rm gap}$  dependence on  $V_{\rm sg}$ , that on  $V_{\rm mg}$ , and that on temperature are included in the model.

Fig. 7 The parasitic resistance for the program condition given by sum of  $R_1$ ,  $R_2$ , and  $R_3$ . The coefficients for these variable resistances have been extracted from measurements.

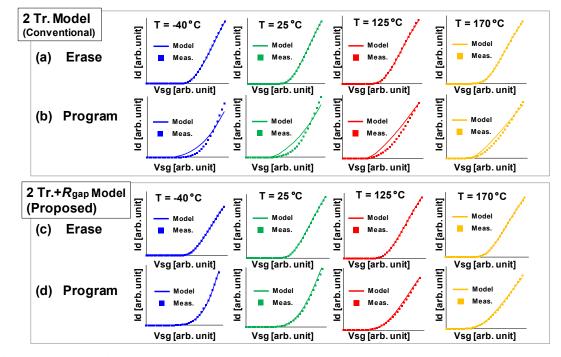

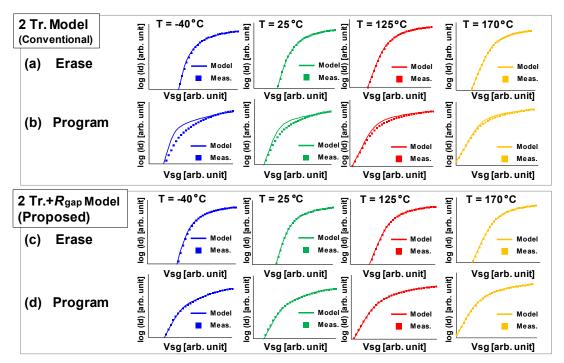

Fig. 8 The fitting result for the read current of 28nm generation SG-MONOS cell. I<sub>d</sub> - V<sub>sg</sub> characteristics at the saturation region are shown for the erase condition and program condition. The prosed  $2\text{Tr.}+R_{\text{gap}}$  model is a single piece model for a continuous temperature, since the  $R_{\text{gap}}$  dependence on the temperature is modeled. In contrast, the conventional 2 Tr. model requires parameter extraction for each discrete temperature.

Fig. 9 The fitting result for the read current of 28nm generation SG-MONOS cell.  $log(I_d)$  -  $V_{sg}$  characteristics at the saturation region are shown for the erase condition and program condition. The prosed 2 Tr.+ $R_{gap}$  model is a single piece model for a continuous temperature, since the  $R_{gap}$  dependence on the temperature is modeled. In contrast, the conventional 2 Tr. model requires parameter extraction for each discrete temperature.

### V. RESULT OF MODEL FITTING

Figs. 8 and 9 show the fitting result for the read current of 28nm generation SG-MONOS cell.  $I_{\rm d}$  -  $V_{\rm sg}$  characteristics at the saturation region are shown in the Fig. 8 and 9. The measured and simulated cell currents are plotted on a linear scale in Fig. 8 and plotted on a logarithmic scale in Fig. 9. A conventional model without  $R_{\rm gap}$  (2 Tr. model) does not reproduce the read current of the program condition, as shown in Fig. 8(b) and Fig. 9(b). However, the proposed model (2 Tr. +  $R_{\rm gap}$  model) exhibits an excellent fitting both for the erase and the program conditions (see Fig. 8 (c), Fig. 8(d), Fig. 9(c), and Fig. 9(d)).

## VI. CONCLUSIONS

A new SPICE-compatible model which reproduces the trap induced parasitic resistance of SG-MONOS cell using a synthesis of several variable resistances has been proposed. The model shows an excellent fitting on the cell current of 28nm generation SG-MONOS.

# REFERENCES

[1] Y. Taito, T. Kono, M. Nakano, T. Saito, T. Ito, K. Noguchi, H. Hidaka, and T. Yamauchi, "A 28 nm Embedded Split-Gate MONOS (SG-MONOS) Flash Macro for Automotive Achieving 6.4 GB/s Read

Throughput by 200 MHz No-Wait Read Operation and 2.0 MB/s Write Throughput at Tj of 170 C", IEEE J. Solid-state circuit, Vol. 51, pp. 213-212 (2016)

- [2] T. Kono, T. Ito, T. Tsuruda, T. Nishiyama, T. Nagasawa, T. Ogawa, Y. Kawashima, H. Hidaka, and T. Yamauchi, "40-nm Embedded Split-Gate MONOS (SG-MONOS) Flash Macros for Automotive With 160-MHz Random Access for Code and Endurance Over 10 M Cycles for Data at the Junction Temperature of 170 C", IEEE J. Solid-state circuit, Vol. 49, pp. 154-166 (2014)

- [3] Y. Taito, M. Nakano, H. Okimoto, D. Okada, T. Ito, T. Kono, K. Noguchi, H. Hidaka, and T. Yamauchi, "7.3 A 28nm embedded SG-MONOS flash macro for automotive achieving 200MHz read operation and 2.0MB/S write throughput at Ti, of 170°C", 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, pp.132–133

- [4] Y. Kawashima, T. Hashimoto, I. Yamakawa, "Investigation of the data retention mechanism and modeling for the high reliability embedded split-gate MONOS flash memory", 2015 IEEE International Reliability Physics Symposium (IRPS), pp. MY.6.1 - MY.6.5

- [5] N. Akil, R. Langevelde, P. Goarin, M. Duuren, and M. Slotboom, "SPICE-compatible macro model for split-gate compact NVM cell with various gap sizes", 2004 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp.263-266.

- [6] S. Martinie, O. Rozeau, M. Tadayoni, C. Raynaud, E. Nowak, S. Hariharan, and N. Do, "SPICE Modeling of 55 nm Embedded SuperFlash® Technology 2T Memory Cells", 2015 International Conference on Microelectronic Test Structures (ICMTS), pp.24-28

- [7] M. Tadayoni, S. Martinie, O. Rozeau, S. Hariharanl, C. Raynaud, and N. Do, "Challenges of Modeling the Split-Gate SuperFlash® Memory Cell with 1.1 V Select Transistor", 2016 International Conference on Microelectronic Test Structures (ICMTS), pp.142-146