# Multi-Subband Interface Roughness Scattering using 3D Finite Element Monte Carlo with 2D Schödinger Equation for Simulations of sub-16nm FinFETs

Daniel Nagy<sup>1</sup>, Muhammad A. Elmessary<sup>1,3</sup>, Manuel Aldegunde<sup>4</sup>, Jari Lindberg<sup>2</sup>, Antonio J. García-Loureiro<sup>5</sup>, and Karol Kalna<sup>1</sup>

<sup>1</sup>ESDC, <sup>2</sup>C2EC College of Engineering, Swansea University, Swansea, Wales, UK, SA2 8PP

<sup>3</sup>Dept. of Mathematics & Engineering Physics, Faculty of Engineering, Mansoura University, Mansoura, Egypt

<sup>4</sup>WCPM, School of Engineering, University of Warwick, Coventry CV4 7AL

<sup>5</sup>CITIUS, Universidade de Santiago de Compostela, 15782 Santiago de Compostela, Galicia, Spain

Email: D.Nagy.491828@swansea.ac.uk, Phone: +44 (0) 1792 602816

Abstract—A new multi-subband interface roughness scattering model is incorporated into a 3D Finite Element ensemble Monte Carlo simulator with 2D Schrödinger equation based quantum corrections. The model takes advantage of wavefunctions and energy levels obtained in solutions of Schrödinger equation on 2D slices across the channel to calculate the respective form factors. The new 3D simulation toolbox is then used to predict the performance of SOI Si FinFETs with 10.7 nm gate length and two cross-sections: rectangular-like (REC) and triangular-like (TRI). We found that the multi-subband IRS is much stronger at large electron kinetic energies resulting in a drive current of 600 mA/ $\mu$ m<sup>2</sup> for the REC shaped channel and of 491 mA/ $\mu$ m<sup>2</sup> for the TRI channel.

#### I. INTRODUCTION

Multi-gate controlled non-planar transistors like FinFETs [1] benefit from low OFF-current, large ON-current and excellent control of the short-channel effects thanks to the superior electrostatic integrity. FinFET devices are already in high-volume production by Intel [2] and also strong contenders to be the leading solutions beyond the sub-14 nm technology. In this scaled process, interface roughness scattering (IRS) is considered to be one of the key limiting factors to carrier transport [3], [4] because fabrication of multi-gate nanoscaled devices is harder to control [5].

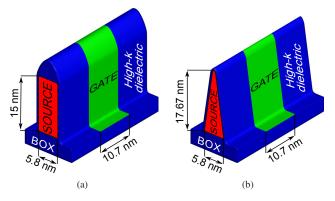

In the current work the development of a new multi-subband IRS model that uses wavefunctions and energy levels from our 3D finite element (FE) Monte Carlo (MC) toolbox [6] with 2D FE Schrödinger equation quantum corrections (SEQC) [7]. The wavefunctions and energy levels are used to calculate form factors entering the multi-subband scattering rate adapted to the FE mesh. The new multi-subband IRS model within the 3D FE MC is then applied to 10.7 nm gate length SOI FinFETs with rectangular-like (Fig. 1(a)) and triangular-like (Fig. 1(b)) [8] cross-sections taking full advantage of the accurate description of their 3D geometry [9] by the FE method and compared with a basic 3D Ando model.

### II. Method

In a previous work [6], a 3D FE MC simulation toolbox with density gradient (DG) quantum corrections demonstrated an excellent agreement with experimental results of the 25 nm gate length SOI FinFET [10]. Since the DG approach requires

Fig. 1. Schematic of the simulated Si SOI FinFETs with (a) rectangular-like (REC) and (b) triangular-like (TRI) cross-sections. Both devices have Gaussian doping with  $\sigma$  of 3.45 nm in the transport direction and an effective oxide thickness (EOT) of 0.62 nm. The perimeter of both devices is kept at 35.8 nm and the area of the channel is 87 and 57 nm<sup>2</sup> for the REC and the TRI, respectively.

calibration of its parameters against a quantum-mechanical simulation the toolbox has been replaced by the 2D FE (time-independent) SEQC [7] to predict transistor performance when in deep nanoscaled region [11]. A 3D FE mesh of the device in the 3D MC toolbox accommodates 2D FE planes perpendicular to the transport direction [7]. The extracted 2D potential V(y, z) from the 3D electrostatic potential  $V(\mathbf{r})$  is used to solve 2D Schrödinger equation at every time step. The eigenstates of the Schrödinger equation are used to calculate the 2D quantum density. The quantum density is then interpolated onto the 3D simulation domain to obtain the quantum corrected potential which, in turn, is used to move particles. During the MC simulation the following scattering processes are taken into account, the acoustic phonon scattering, nonpolar optical phonon scattering (g, f-processes) [12], ionized impurity scattering using the third body exclusion model by Ridley [13] and interface roughness scattering using Ando's model as described in [14]. More details on the 3D FE MC toolbox can be found in Refs. [6] [7] [15].

#### A. Interface Roughness Model

The IRS model requires a power spectrum of the interface roughness that is commonly described with Gaussian or exponential forms [16]. The latter has been chosen as suggested in Ref. [17] and the matrix element for Ando is represented as:

$$\Gamma(\mathbf{k}) = \frac{m^* e^4}{\hbar^3 \epsilon_S^2} \frac{\Delta_{RMS}^2 \Lambda^2 E_{\perp}^2}{\sqrt{1 + k^2 \Lambda^2}} \, \mathcal{E}\left(\frac{k\Lambda}{\sqrt{1 + k^2 \Lambda^2}}\right), \qquad (1)$$

where  $E_{\perp}$  is the transverse electric field,  $\mathcal{E}$  is the complete elliptic integral of the first kind,  $\Delta_{RMS}$  is the RMS height of the interface roughness and  $\Lambda$  is the correlation length. The value for the  $\Delta_{RMS}$  is 0.57 nm, taken from experimental data [18] and  $\Lambda$  is 1.7 nm [17].

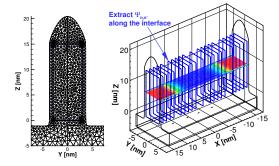

In the current work we have incorporated the multi-subband IRS model that is based on a 2D formulation of the extended Prange & Nee (EPN) scattering model for arbitrary paths [5]. The calculation of the scattering rate is carried out for all 2D planes (21) used by the 2D SEQC as illustrated in Fig. 2.

Fig. 2. One of the slices for the 2D Schrödinger solver is shown with the finite element mesh. Scheme of the rectangular-like FinFET with the 2D interface slices along the transport direction (x-axis) and the Gaussian doping profile.

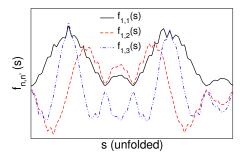

In order to calculate the scattering matrix the wavefunctions are extracted for all the eigenstates along the interface and then unfolded onto an equidistant grid that allows to calculate the form factors as (Fig. 3):

$$f_{n,n'}(s) = \psi_{n,k}^* \psi_{n',k'} \Delta V, \tag{2}$$

where n, n' are the initial and final energy levels, respectively,  $\Delta V$  is the potential barrier between Si channel and high- $\kappa$  dielectric.

Fig. 3. The form factors  $f_{n,n'}(s)$  for the initial state n = 1 and the final states n' = 1, 2, 3 are shown at  $V_D = 0.05$  V and  $V_G = 0.0$  V for the rectangular FinFET.

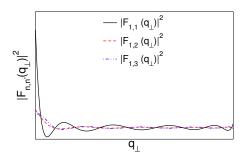

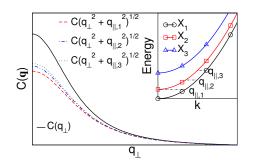

As aforementioned a power spectrum of the interface roughness is characterized by the exponential form. This spectrum is a Fourier transform of the random interface between the channel and the dielectric. Therefore a fast Fourier transform has to be applied to the form factors to calculate the spectral form functions,  $F_{n,n'}(q_{\perp})$  (Fig. 4).

Fig. 4. A fast Fourier transformation of  $f_{n,n'}(s)$  for the initial state n = 1 and the final states n' = 1, 2, 3 using the  $10^{th}$  degree regression are shown at  $V_{\rm D} = 0.05$  V and  $V_{\rm G} = 0.0$  V for the rectangular FinFET.

Finally the scattering rate from the initial state n to the final state n' is calculated as:

$$\frac{1}{\tau_{n,n'}(E)} = \frac{1}{2\hbar} \int_{R} |F_{n,n'}(q_{\perp})|^2 \ C(\mathbf{q}) \ dq_{\perp} \ g_{1D,n'}(E) \ A$$

(3)

where  $g_{1D,n'}$  is the 1D density of states (DOS), A is the area of the channel and  $C(\mathbf{q})$  is the exponential power spectrum, where  $\mathbf{q} = \sqrt{q_{\parallel}^2 + q_{\perp}^2}$ , illustrated in Fig. 5.

Fig. 5. Exponential power spectrum of surface roughness. The inset shows the  $q_{||}$  values. In both cases the initial state is 1 and the final state is 2 at  $V_D = 0.05 V$  and  $V_G = 0.0 V$  for the rectangular FinFET. Symbols are not shown for all data points.

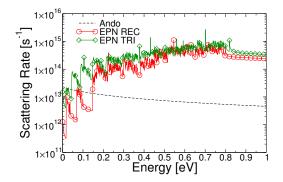

The MC simulation was split to three stages, we run a pre-simulation using the 3D Ando model followed by the calculation of the maximum IRS rate and finally the simulation with the multi-subband EPN model until the steady state is reached. The instantaneous IRS rate, depending on the actual potential distribution in the device, is calculated to perform a rejection technique. The instantaneous IRS rate at the particle location is interpolated from the nearest slice and assumes an exponential decay of the roughness potential strength as a function of distance from the interface [3]. Fig. 6 shows the maximum scattering rate when the drain bias is 0.7 V and the gate bias is 0.9 V for both IRS model. For the multi-subband EPN model, the scattering has a maximum at the subband positions as expected. Note that the Ando model gives a higher probability of scattering below 0.15 eV and 0.05 eV for the REC and TRI, respectively, while at a larger energy the trend is opposite.

Fig. 6. Interface roughness scattering rates (maxima) from 3D (Ando) compared to multi-subband extended Prange & Nee (EPN) models. The EPN is for the 20 lowest electron subbands of the rectangular-like (REC) and triangular-like (TRI) devices at  $V_{\rm D}=0.7$  V and  $V_{\rm G}=0.9$  V showed only up to 1 eV but calculated up to 3 eV. Symbols are not shown for all data points.

#### III. RESULTS

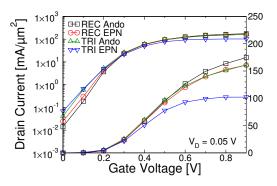

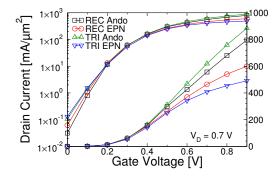

The new IRS model incorporated into the 3D SEQC FE MC toolbox and then applied to investigate n-channel SOI FinFETs with a gate length of 10.7 nm and a  $\langle 100 \rangle$  channel orientation designed following the ITRS guidelines [19]. We study two cross-sections, rectangular-like (REC) and triangular-like (TRI), to demonstrate a versatility of new 3D tool for realistic nanoscale device geometry. Figs. 7 and 8 show  $I_{\rm D}\text{-}V_{\rm G}$  characteristics, with the current normalized-to-area, for the two crosssections comparing the IRS models at low (V  $_{\rm D}=0.05~{\rm V})$  and high ( $V_D = 0.7$  V) drain biases, respectively. At low drain bias, the current is overestimated by the Ando model as the gate voltage increases above 0.4 V for the REC shaped channel by about 8% while for the TRI it is about 37%. At high drain bias, the difference between the two IRS models increases to 25% and 44%, respectively. In short, the difference between the 3D Ando model and the multi-subband EPN is more significant for the TRI device.

Fig. 7.  $I_D$ -V<sub>G</sub> characteristics at V<sub>D</sub> = 0.05 V using a normalised-to-area current for the rectangular-like (REC) and triangular-like (TRI) FinFETs with gate lengths of 10.7 nm comparing the 3D interface roughness model (Ando) with the multi-subband model (EPN).

Table I lists the current at  $V_G-V_T = 0.7V$  and subthreshold slope (SS) from drift-diffusion (DD) simulations. Note that a better SS in the TRI FinFETs is thanks to a better control of the gate over the channel transport due to stronger confinement and that DIBL obtained from MC is larger than DD since it

Fig. 8.  $I_D$ -V<sub>G</sub> characteristics at V<sub>D</sub> = 0.7 V using a normalised-to-area current for the rectangular-like (REC) and triangular-like (TRI) FinFETs with gate lengths of 10.7 nm comparing the 3D interface roughness model (Ando) with the multi-subband model (EPN).

accounts for quantum capacitance [11].

TABLE I.

SS for drain biases of 0.05 V (LOW) and 0.7 V (HIGH) from the DD, DIBL from DD and from MC, and drive currents for normalized-to-area for 3D (Ando) and multi-subband (EPN) interface roughness models.

| Cross-section<br>Model                                 | Rectang<br>Ando | ular-like<br>EPN | Triangu<br>Ando | ılar-like<br>EPN |

|--------------------------------------------------------|-----------------|------------------|-----------------|------------------|

| $SS_{DD}^{LOW}$ [mV/dec]                               | 70              |                  | 66              |                  |

| $SS_{DD}^{HIGH}$ [mV/dec]<br>DIBL <sub>DD</sub> [mV/V] | 71<br>56        |                  | 66<br>34        |                  |

| $DIBL_{MC}$ [mV/V]                                     | 66              | 68               | 64              | 65               |

| ${ m I}_{ m MC}^{LOW}$ [mA/ $\mu$ m <sup>2</sup> ]     | 175             | 161              | 161             | 102              |

| $I_{MC}^{HIGH}$ [mA/ $\mu$ m <sup>2</sup> ]            | 796             | 600              | 885             | 491              |

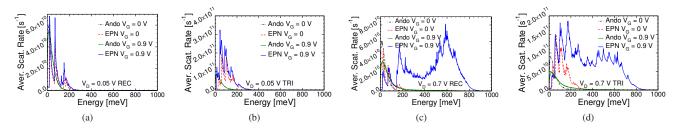

Fig. 9 show the monitoring of an average scattering rate versus the electron kinetic energy for the REC and the TRI shaped FinFETs. The average scattering rate  $\Gamma_{\text{aver}}(E)$  has been calculated as:

$$\Gamma_{\rm aver}(E) = \frac{n_{\rm scat}(E)}{n_{\rm part}\tau_{\rm sim}} \tag{4}$$

where  $n_{\rm scat}(E)$  is the number of scattering events at initial kinetic energy E,  $n_{\rm part}$  is the number of particles in the simulation, and  $\tau_{\rm sim}$  is the monitored simulation time. Fig. 9(a) compares the two IRS models at a low drain bias showing that the difference in the current comes from the underestimation of the IRS at higher energies. This becomes even more significant for the TRI [Fig. 9(b)] device and becomes even more visible at a high drain bias in Fig. 9(c) for REC and Fig. 9(d) for TRI transistors, respectively.

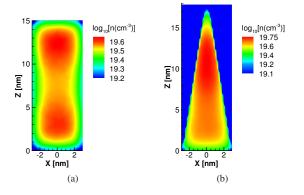

Finally, Fig. 10 shows the electron density profile for the two cross-sections in the middle of the gate at the corresponding overdrive bias for the (a) REC and (b) TRI shape transistors, respectively. Both devices exhibit volume inversion but the density is separated to upper and lower streams in the case of the REC shape. The density profile for the TRI device has a maximum near the upper narrow part of the channel which can be explained by the narrow channel and by vicinity to the gate when compared to the REC one (see Fig. 1).

## IV. CONCLUSION

We have successfully incorporated a new multi-subband EPN model into the 3D FE MC simulation toolbox with 2D

Fig. 9. Average scattering rate compared for 3D (Ando) and multi-subband (EPN) models. The biases are  $V_D = 0.05$  V for the (a) rectangular-like (REC) and (b) triangular-like (TRI) and  $V_D = 0.7$  V for (c) REC and (d) TRI devices at  $V_G-V_T = 0.7V$ .

Fig. 10. Electron density in the middle of the gate of the (a) rectangular-like and (b) triangular-like devices at  $V_G$ - $V_T$  = 0.7 V.

Schrödinger equation based quantum corrections. The new toolbox used to investigate the effect of the IRS models on the 10.7 nm gate length Si SOI FinFETs for two realistic cross-sections, rectangular-like and triangular-like at both low (0.05 V) and high (0.7 V) drain biases. We have observed that the multi-subband EPN IRS is stronger than the 3D Ando IRS at a large electron kinetic energy (from above 0.06 eV in the simulations of 10.7 nm gate length Si SOI TRI FinFETs). The 3D MC simulations which use the multi-subband EPN model predict a drive current of 161 mA/ $\mu$ m<sup>2</sup> for the REC shaped channel and of 104 mA/ $\mu$ m<sup>2</sup> for the TRI one at a low drain bias of 0.05 V. This is about 8% and 37% smaller, respectively, when compared to the results obtained using the 3D Ando model. At a high drain bias of 0.7 V, the predicted drive currents are 600 mA/ $\mu$ m<sup>2</sup> (REC) and 491 mA/ $\mu$ m<sup>2</sup> (TRI), smaller by about 25% and 44%, respectively. The multisubband EPN IRS plays naturally a more significant role in the TRI device due to stronger confinement of carriers in the channel confirming that the IRS is essential for meaningful modelling of carrier transport in nanocale multi-gate transistors.

#### REFERENCES

- X. Huang et al., "Sub 50-nm FinFET: PMOS," in *Electron Devices* Meeting, 1999. IEDM '99. Technical Digest. International, Dec 1999, pp. 67–70.

- [2] Intel, "Intel 14 nm Technology," 2014. [Online]. Available: http://www.intel.com/content/www/us/en/siliconinnovations/intel-14nm-technology.html

- [3] S. Jin, M. V. Fischetti, and T.-w. Tang, "Modeling of electron mobility in gated silicon nanowires at room temperature: Surface roughness

scattering, dielectric screening, and band nonparabolicity," J. Appl. Phys., vol. 102, no. 8, p. 083715, 2007.

- [4] J. Wang et al., "Theoretical investigation of surface roughness scattering in silicon nanowire transistors," *Appl. Phys. Lett.*, vol. 87, no. 4, p. 043101, 2005.

- [5] Z. Stanojevic and H. Kosina, "Surface-roughness-scattering in nonplanar channels – The role of band anisotropy," in *Simulation of Semiconductor Processes and Devices (SISPAD), 2013 International Conference on*, Sept 2013, pp. 352–355.

- [6] M. Aldegunde, A. Garcia-Loureiro, and K. Kalna, "3D Finite Element Monte Carlo Simulations of Multigate Nanoscale Transistors," *IEEE T. Electron. Dev.*, vol. 60, no. 5, pp. 1561–1567, May 2013.

- [7] J. Lindberg *et al.*, "Quantum Corrections Based on the 2-D Schrödinger Equation for 3-D Finite Element Monte Carlo Simulations of Nanoscaled FinFETs," *IEEE T. Electron. Dev.*, vol. 61, no. 2, pp. 423– 429, Feb 2014.

- [8] C. Auth et al., "A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," in VLSI Technology (VLSIT), 2012 Symposium on, June 2012, pp. 131–132.

- [9] R. T. Bühler, R. Giacomini, M. A. Pavanello, and J. A. Martino, "Trapezoidal SOI FinFET analog parameters' dependence on crosssection shape," *Semicond. Sci. Tech.*, vol. 24, no. 11, p. 115017, 2009.

- [10] V. Basker et al., "A 0.063 μm<sup>2</sup> FinFET SRAM cell demonstration with conventional lithography using a novel integration scheme with aggressively scaled fin and gate pitch," in VLSI Technology (VLSIT), 2010 Symposium on, June 2010, pp. 19–20.

- [11] D. Nagy et al., "3-D Finite Element Monte Carlo Simulations of Scaled Si SOI FinFET With Different Cross Sections," *Nanotechnology, IEEE Transactions on*, vol. 14, no. 1, pp. 93–100, Jan 2015.

- [12] C. Jacoboni and P. Lugli, *The Monte Carlo Method for Semiconductor Device Simulation*, ser. Computational Microelectronics. Springer Vienna, 2012.

- [13] B. K. Ridley, "Reconciliation of the Conwell-Weisskopf and Brooks-Herring formulae for charged-impurity scattering in semiconductors: Third-body interference," *Journal of Physics C: Solid State Physics*, vol. 10, no. 10, p. 1589, 1977.

- [14] D. Ferry, Semiconductor Transport. Taylor & Francis, 2000.

- [15] M. Aldegunde, N. Seoane, A. Garca-Loureiro, and K. Kalna, "Reduction of the self-forces in Monte Carlo simulations of semiconductor devices on unstructured meshes," *Comput. Phys. Commun.*, vol. 181, no. 1, pp. 24 – 34, 2010.

- [16] D. Esseni, P. Palestri, and L. Selmi, Nanoscale MOS Transistors: Semi-Classical Transport and Applications. Cambridge University Press, 2011.

- [17] S. M. Goodnick *et al.*, "Surface roughness at the Si(100)-SiO<sub>2</sub> interface," *Phys. Rev. B*, vol. 32, pp. 8171–8186, Dec 1985.

- [18] X. Tang et al., "A Simple Method for Measuring Si-Fin Sidewall Roughness by AFM," *Nanotechnology, IEEE Transactions on*, vol. 8, no. 5, pp. 611–616, Sept 2009.

- [19] ITRS(2012), "International Technology Roadmap for Semiconductors," 2012. [Online]. Available: http://www.itrs.net/Links/2012ITRS/Home2012.htm