# Microscopic Oxide Defects Causing BTI, RTN, and SILC on High-K FinFETs

G. Rzepa\*, M. Walt1\*, W. Goes\*, B. Kaczer<sup>†</sup>, and T. Grasser\*

\*Institute for Microelectronics, TU Wien, Vienna, Austria

†imec, Leuven, Belgium

Abstract—Reliability issues of MOSFETs such as bias temperature instability (BTI), random telegraph noise (RTN), and stress-induced leakage current (SILC), are linked to the trapping of charges in oxides. Even though the chemical structure of these oxide defects is still the subject of debate, detailed studies of these reliability phenomena have shown that their physical behavior can be successfully described by non-radiative multiphonon (NMP) theory. In this work we characterize and study a pMOS high-k FinFET technology starting from degradation measurements up to the simulation of the energy barriers in the framework of NMP theory. This allows to investigate the aforementioned reliability issues all based on their common cause, the microscopic oxide defects.

#### Introduction

Recent MOS technologies have become highly susceptible to the impact of single charge trapping events in their oxides. On the one hand, this has resulted in investigations regarding variability aspects in general [1], on the other hand there is a growing need to understand the details behind the various facets of oxide defects such as RTN [2–6], BTI [7–14] and SILC [15]. The first step towards a physical description that can cover all these effects was the application of NMP theory [3, 16, 17]. Based on detailed studies of individual defects, the four-state NMP model has been suggested recently [18] and its validity was confirmed by successful application to charge trapping related issues [13, 14, 18, 19]. In this work we will characterize this model for a state-of-the-art technology, followed by a detailed investigation of RTN, BTI, and SILC at the single defect level.

# EXPERIMENTAL

In this work we investigate a pMOS FinFET technology with a 1.6 nm thick HfO2 layer (HK) and a 0.6 nm thick SiO<sub>2</sub> interface layer (IL). The fin length is 100 nm and the fin width and height are 10 and 30 nm, respectively. In order to characterize BTI for this technology, we have performed measure-stress-measure (MSM) cycles [20] on structures with 22 fins in parallel (1.54 µm effective width). As the gate voltage during recovery phases  $(V_G^H)$  was fixed at time-zero threshold voltage  $(V_{\text{th},0})$ , the threshold voltage shift  $(\Delta V_{\text{th}})$  was calculated based on the measured drain current using the initial transfer characteristics. This was done for several stress setups, each on "fresh" devices, with gate voltages during stress varying between  $V_{\rm G}^{\rm H}=-0.85$  and  $-1.45\,{\rm V}$  and temperatures between T = 75 and 175°C. The stress times were varied from 0.1 µs up to 10 ks and recovery was recorded with a short measurement delay of a few us and recovery times up to 10 ks. The drain voltage during stress and recovery was -0.1 V. The measurement data are shown in Fig. 1 and Fig. 2 together with the simulation results, which will be discussed in the following.

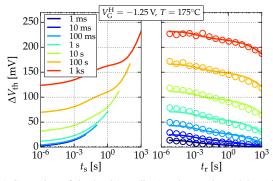

Fig. 1: Comparison of simulated  $\Delta V_{\rm th}$  (lines) to the experimental data (circles) during stress ( $t_{\rm s}$ ) and recovery ( $t_{\rm r}$ ). The stress times of the consecutive stress-recovery cycles of this MSM experiment were stepped between 1 ms for the first cycle (blue) and 1 ks for the last cycle (red), while the recovery time was 1 ks for each cycle in this exemplary setup with  $V_{\rm G}^{\rm H} = -1.25$  V and  $T = 175^{\circ}$ C. The drain current was recorded during recovery only, hence there is no  $\Delta V_{\rm th}$  data for stress.

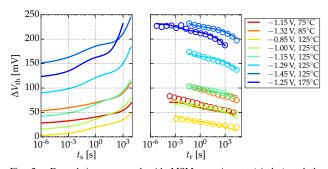

Fig. 2: Degradation measured with MSM experiments (circles) and the corresponding simulation results (lines) for setups with different combinations of temperature and stress voltage. Each condition was measured on another fresh device. Only the data of the last stress ( $t_s$ ) and recovery ( $t_r$ ) cycle is shown.

# Modeling

BTI-related degradation is modeled within the framework of the NMP theory with microscopic oxide and interface defects. The various transitions between the four states of the oxide defects are described using the energy potential surfaces of the defects along selected configuration coordinates (CC) [18]. In addition to oxide defects, the generation and the recovery of interface defects are described by a double-well model [21] while their charge is determined using an amphoteric Shockley-Read-Hall model [22]. The parameters of the microscopic defects were sampled from distributions which were calibrated to measurement data [19, 23]. Simulations of  $\Delta V_{\rm th}$  based on these defects match the measurement data for various stress setups (Fig. 1 and Fig. 2), hence a representative set of microscopic defects has been obtained.

# Discussion

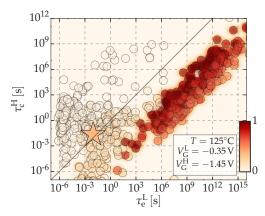

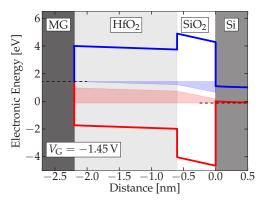

In the following, reliability mechanisms will be discussed with the help of a single four-state NMP defect, denoted as "S". This defect is shown as a star in the scatter plots. Fig. 3 shows a randomly selected subset of interface and oxide defects plotted according to their capture ( $\tau_c$ ) and emission time constants ( $\tau_c$ ) while their color indicates their contribution to  $\Delta V_{\rm th}$ . These capture/emission time (CET) map plots refer to DC stress with stress voltage  $V_{\rm G}^{\rm H}$  and recovery voltage  $V_{\rm G}^{\rm L}$  [24, 25]. For such stress conditions, the active regions [18] can be specified in the band diagram (Fig. 4). Only traps within these regions have a trap level "passing" the Fermi level of the gate or the channel for the given stress voltages, hence can capture or emit a hole from the gate or the channel, respectively, and thus contribute to a change in the measured  $V_{\rm th}$ .

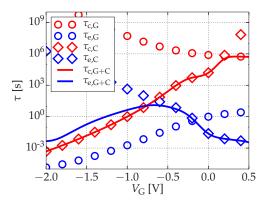

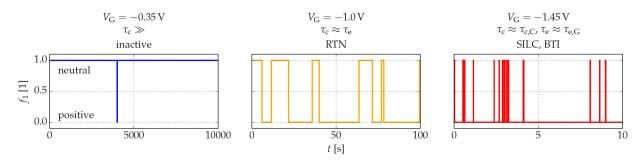

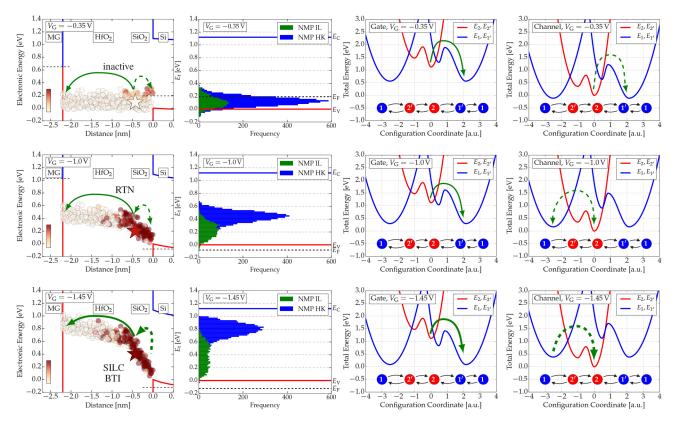

While an increase in the stress voltage increases the defect's probability to capture a hole from the channel, it decreases the probability to capture a hole from the gate. These interactions always appear concurrently and result in effective capture and emission times measurable with timedependent defect spectroscopy (TDDS) [26]. Simulations allow for separate analysis of these effects as shown for defect "S" in Fig. 5. In accordance with the simulated occupancy of this defect (Fig. 6)  $\tau_c$  is huge around the threshold voltage  $(V_{\rm G} = V_{\rm th,0} = -0.35 \, \rm V)$  and, therefore, the defect is neutral and inactive while for moderate stress voltages ( $V_{\rm G} = -1.0\,{\rm V}$ )  $\tau_{\rm c}$ is of the same order of magnitude as  $\tau_e$  and typical RTN steps can be observed. For high stress ( $V_G = -1.45 \text{ V}$ ) capture times via the channel  $(\tau_{c,C})$  and emission times via the gate  $(\tau_{e,G})$ decrease and the defect now contributes to SILC. These three stress conditions are further analyzed in Fig. 7 where each row shows the same plots only for different  $V_G$ . In the 1<sup>st</sup> column the shift of the trap levels is depicted in the band diagram. The electric field is smaller in the HK layer, hence the shift of the trap levels is less position dependent compared to the IL. This is in agreement with the density of states (DOS) of oxide defects shown in the  $2^{nd}$  column. The occupancy probability f, which is indicated by the color of the circles in the 1st column, depends on the Fermi levels of both, the channel and the gate,

Fig. 3: Capture time constants at  $V_{\rm G}^{\rm H}$  and emission time constants at  $V_{\rm G}^{\rm L}$  of a randomly selected subset of simulated oxide and interface defects. The color of the defects represent their impact on  $\Delta V_{\rm th}$  for the given setup. In accordance with the measurements, a broad distribution of time constants can be observed. Defect "S" is depicted by a star.

Fig. 4: Band diagram of the high-k pMOS FinFET. Active regions are depicted with respect to  $V_{\rm G}^{\rm L}=-0.35$  V for gate (MG) interaction (blue area) and channel (Si) interaction (red area). The Fermi levels are indicated by dashed black lines.

Fig. 5: Simulated bias dependence of  $\tau_c$  (red) and  $\tau_e$  (blue) of defect "S" for gate only (diamonds), channel only (circles), and the combination of both interactions (lines). A discharge of this defect can be triggered by applying gate voltages around 0 V. In this regime the emission into the channel can become very fast which is why this type of defects is termed "switching oxide trap" [18]. Note that the combined interactions yield larger emission times than sole gate interaction. This is because of the interplay of the transition rates via the metastable states.

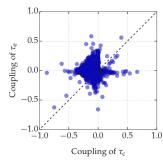

as well as the energy barriers and the tunneling coefficients between the respective carrier reservoirs. The energy levels and barriers of defect "S" are investigated in the CC diagrams for gate interaction (3<sup>rd</sup> column) and channel interaction (4<sup>th</sup> column) which helps to explain the bias dependent contribution of this defect to BTI, RTN, and SILC in agreement with the observations made in Fig. 5. The fact that  $\tau_c$  of an oxide defect can be determined by a channel interaction while  $\tau_e$  is determined by a gate interaction and vice versa is not only a necessary finding to understand SILC [27], but it also explains the broad distribution of couplings of time constants found by RTN based measurements [28]. The coupling factors of the simulated oxide defects are shown in Fig. 8.

Compared to measurement data of typical high-k devices, the technology investigated in this work shows a significant fraction of defects with large emission time constants. This pronounced contribution of "permanent" defects could be due to the higher interface trap density at the side walls of the fin structures [29], but the clarification of this issue will require additional investigations.

Fig. 6: Transient simulation of the occupancy of the neutral state "1"  $(f_1)$  [18] of defect "S", which strongly depends on  $V_G$ . For  $V_G = V_{th} = -0.35 \, \text{V}$  (top) the capture time constant is huge, hence the defect is basically not active. With increasing stress voltage the frequency of capture events via the channel increase significantly. Around  $V_G = -1.0 \, \text{V}$  (middle) the capture and emission time constants are on the same order of magnitude which results in typical RTN traces. For a further rise of the stress voltage this trend continues. As the frequency of emission events into the gate increase too, this defect contributes to SILC. Additionally, at  $V_G = -1.45 \, \text{V}$  (bottom) holes capture much faster than they emit, so the average of  $f_1$  is close to zero. Therefore, the defect is positively charged most of the time and will cause BTI.

Fig. 7: Each row shows the same plots only for different stress voltage:  $1^{st}$  row:  $V_G = -0.35$  V,  $2^{nd}$  row:  $V_G = -1.0$  V,  $3^{rd}$  row:  $V_G = -1.45$  V.  $1^{st}$  column: Band diagrams with oxide defects (circles, defect "S": star), their color indicates their occupancy probability at equilibrium. For  $V_G = -0.35$  V most defects are below the Fermi levels of both, the gate and the channel and are thus neutral. With increasing stress voltage the trap levels of more and more defects are moved above the Fermi level of the channel, thus can capture holes from the channel. Still, the trap levels are below the Fermi level of the gate to which they can emit holes and, therefore, the occupancy probability results from the balance of these carrier exchanges.  $2^{nd}$  column: The DOS of defects in the interface layer (green) and in the high-k (blue). The trap levels of defects in layers with higher permittivity are less position dependent. Still, they see a larger shift with respect to the band edges of the channel while their distribution stays narrow compared to the trap levels of the defects in the IL.  $3^{rd}$  column: CC diagrams for gate interaction with defect "S".  $4^{th}$  column: CC diagrams for channel interaction with defect "S". In accordance with the pronounced decrease of  $\tau_c$  around  $V_G = 0$  V (compare Fig. 5) this defect acts as a switching oxide trap and favors emission via the smaller barrier to 1' for these gate voltages. The green arrows highlight hole capture and emission between defect "S" and the gate (solid arrows) or the channel (dashed arrows) while thicker arrows represent larger rates, hence shorter time constants. For  $V_G = -0.35$  V ( $1^{st}$  row) holes are emitted to both, the gate and the channel but capture events are very unlikely and the defect is thus inactive (compare Fig. 6). An increase of  $V_G$  ( $2^{nd}$  row) shifts the trap level of defect "S" above the Fermi level of the channel and, therefore, the defect ( $3^{rd}$  row) increases both,  $\tau_{c,C}$  and  $\tau_{c,G}$ , hence

Fig. 8: Simulated oxide defects plotted according to their coupling factors of  $\tau_e$  and  $\tau_c$ . A positive coupling factor refers to a positive slope of the respective time constant for increasing stress voltage. As we have considered gate and channel interaction, all combinations of coupling factors can be observed, which is in agreement with observations based on RTN measurements [28].

#### Conclusions

Based on degradation measurements we have successfully characterized a pMOS high-k FinFET technology. Close analysis of the extracted microscopic oxide defects, described by the four-state NMP model, has revealed the details of the mechanisms which let them cause BTI, RTN, and SILC. The distribution of trap levels was investigated and the interplay of carrier exchange with the gate and with the channel was studied in detail as it explains the variety of experimental observations related to charge trapping of oxides.

## ACKNOWLEDGEMENTS

This work has received funding from the the European Community's FP7 n°619234 (MoRV) and the Intel Sponsored Research Project n°2013111914.

## REFERENCES

- [1] J. Franco, B. Kaczer, P. Roussel, J. Mitard, M. Cho, L. Witters, T. Grasser, and G. Groeseneken, "SiGe Channel Technology: Superior Reliability Toward Ultrathin EOT Devices – Part I: NBTI," *IEEE Trans. Electron Devices*, vol. 60, pp. 396–404, Jan 2013.

- [2] K. Ralls, W. Skocpol, L. Jackel, R. Howard, L. Fetter, R. Epworth, and D. Tennant, "Discrete Resistance Switching in Submicrometer Silicon Inversion Layers: Individual Interface Traps and Low-Frequency (1/f?) Noise," *Physical Review Letters*, vol. 52, no. 3, pp. 228–231, 1984.

- [3] M. Kirton and M. Uren, "Noise in Solid-State Microstructures: A New Perspective on Individual Defects, Interface States and Low-Frequency (1/f) Noise," Adv. Phys., vol. 38, no. 4, pp. 367–486, 1989.

- [4] A. Palma, A. Godoy, J. A. Jimenez-Tejada, J. E. Carceller, and J. A. Lopez-Villanueva, "Quantum Two-Dimensional Calculation of Time Constants of Random Telegraph Signals in Metal-Oxide-Semiconductor Structures," *Physical Review B*, vol. 56, no. 15, pp. 9565–9574, 1997.

- [5] T. Nagumo, K. Takeuchi, T. Hase, and Y. Hayashi, "Statistical Characterization of Trap Position, Energy, Amplitude and Time Constants by RTN Measurement of Multiple Individual Traps," in *Proc. Intl. Electron Devices Meeting (IEDM)*, pp. 628–631, 2010.

- [6] B. Kaczer, M. Toledano-Luque, W. Goes, T. Grasser, and G. G., "Gate Current Random Telegraph Noise and Single Defect Conduction," *Microelectronic Engineering*, vol. 109, no. 7, pp. 123–125, 2013.

- [7] C. Zhao, J. Zhang, G. Groeseneken, and R. Degraeve, "Hole-Traps in Silicon Dioxides Part II: Generation Mechanism," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1274–1280, 2004.

- [8] V. Huard, C. Parthasarathy, and M. Denais, "Single-Hole Detrapping Events in pMOSFETs NBTI Degradation," in *Proc. Intl. Integrated Reliability Workshop*, pp. 5–9, 2005.

- [9] T. Wang, C.-T. Chan, C.-J. Tang, C.-W. Tsai, H. Wang, M.-H. Chi, and D. Tang, "A Novel Transient Characterization Technique to Investigate Trap Properties in HfSiON Gate Dielectric MOSFETs-From Single Electron Emission to PBTI Recovery Transient," *IEEE Trans.Electron Devices*, vol. 53, no. 5, pp. 1073–1079, 2006.

- [10] D. Ang, S. Wang, G. Du, and Y. Hu, "A Consistent Deep-Level Hole Trapping Model for Negative Bias Temperature Instability," *IEEE Trans. Dev. Mat. Rel.*, vol. 8, no. 1, pp. 22–34, 2008.

- [11] T. Grasser, B. Kaczer, W. Goes, T. Aichinger, P. Hehenberger, and M. Nelhiebel, "Understanding Negative Bias Temperature Instability in the Context of Hole Trapping," *Microelectronic Engineering*, vol. 86, no. 7-9, pp. 1876–1882, 2009.

- [12] H. Reisinger, T. Grasser, and C. Schlünder, "A Study of NBTI by the Statistical Analysis of the Properties of Individual Defects in pMOSFETs," in *Proc. Intl. Integrated Reliability Workshop*, pp. 30–35, 2009.

- [13] T. Grasser, ed., Bias Temperature Instability for Devices and Circuits. Springer, New York, 2014.

- [14] T. Grasser, K. Rott, H. Reisinger, M. Waltl, J. Franco, and B. Kaczer, "A Unified Perspective of RTN and BTI," in *Proc. Intl.Rel.Phys.Symp.* (IRPS), pp. 4A.5.1–4A.5.7, June 2014.

- [15] J. Maserjian and N. Zamani, "Behavior of the Si/SiO2 Interface Observed by FowlerNordheim Tunneling," *J.Appl.Phys.*, vol. 53, no. 1, pp. 559–567, 1982.

- [16] K. Huang and A. Rhys, "Theory of Light Absorption and Non-Radiative Transitions in F-Centres," *Proc.R.Soc.A*, vol. 204, pp. 406–423, 1950.

- [17] D. Lang and C. Henry, "Nonradiative Recombination at Deep Levels in GaAs and GaP by Lattice-Relaxation Multiphonon Emission," *Physical Review Letters*, vol. 35, no. 22, pp. 1525–1528, 1975.

- [18] T. Grasser, "Stochastic Charge Trapping in Oxides: From Random Telegraph Noise to Bias Temperature Instabilities," *Microelectronics Reliability*, vol. 52, pp. 39–70, 2012.

- [19] G. Rzepa, W. Goes, G. Rott, K. Rott, M. Karner, C. Kernstock, B. Kaczer, H. Reisinger, and T. Grasser, "Physical Modeling of NBTI: From Individual Defects to Devices," in *Proc. Simulation of Semiconductor Processes and Devices*, pp. 81–84, 2014.

- [20] T. Grasser, P.-J. Wagner, P. Hehenberger, W. Goes, and B. Kaczer, "A Rigorous Study of Measurement Techniques for Negative Bias Temperature Instability," *IEEE Trans.Dev.Mat.Rel.*, vol. 8, no. 3, pp. 526 – 535, 2008.

- [21] T. Grasser, T. Aichinger, G. Pobegen, H. Reisinger, P.-J. Wagner, J. Franco, M. Nelhiebel, and B. Kaczer, "The 'Permanent' Component of NBTI: Composition and Annealing," in *Proc. Intl.Rel.Phys.Symp.* (IRPS), pp. 605–613, Apr. 2011.

- [22] Y. Yang and M. White, "Charge Retention of Scaled SONOS Non-volatile Memory Devices at Elevated Temperatures," *Solid-State Electron.*, vol. 44, pp. 949–958, 2000.

- [23] Minimos-NT (www.globaltcad.com).

- [24] H. Reisinger, T. Grasser, K. Ermisch, H. Nielen, W. Gustin, and C. Schlünder, "Understanding and Modeling AC BTI," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 597–604, Apr. 2011.

- [25] T. Grasser, P.-J. Wagner, H. Reisinger, T. Aichinger, G. Pobegen, M. Nelhiebel, and B. Kaczer, "Analytic Modeling of the Bias Temperature Instability Using Capture/Emission Time Maps," in *Proc. Intl. Electron Devices Meeting (IEDM)*, pp. 27.4.1–27.4.4, Dec. 2011.

- [26] T. Grasser, H. Reisinger, P.-J. Wagner, W. Goes, F. Schanovsky, and B. Kaczer, "The Time Dependent Defect Spectroscopy (TDDS) for the Characterization of the Bias Temperature Instability," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 16–25, May 2010.

- [27] W. Goes, M. Toledano-Luque, O. Baumgartner, M. Bina, F. Schanovsky, B. Kaczer, and T. Grasser, "Understanding correlated drain and gate current fluctuations," in *Proc. Intl.Symp. on Physical and Failure Analysis of Integrated Circuits*, pp. 51–56, 2013.

- [28] H. Miki, N. Tega, M. Yamaoka, D. J. Frank, A. Bansal, M. Kobayashi, K. Cheng, C. D'Emic, Z. Ren, S. Wu, J.-B. Yau, Y. Zhu, M. A. Guillorn, D.-G. Park, W. Haensch, E. Leobandung, and K. Torii, "Statistical Measurement of Random Telegraph Noise and Its Impact in Scaleddown High-κ/Metal-gate MOSFETs," in Proc. Intl. Electron Devices Meeting (IEDM), pp. 450–453, 2012.

- [29] G. Kapila, B. Kaczer, A. Nackaerts, N. Collaert, and G. V. Groeseneken, "Direct Measurement of Top and Sidewall Interface Trap Density in SOI FinFETs," vol. 28, pp. 232–234, 2007.