# Analysis of Worst-Case Hot-Carrier Degradation Conditions in the Case of n- and p-channel High-Voltage MOSFETs

Ivan Starkov and Hajdin Ceric

Christian Doppler Laboratory for Reliability Issues

in Microelectronics at the Institute for Microelectronics,

Technische Universität Wien

Gußhausstraße 27-29, A-1040 Vienna, Austria

Email: {starkov|ceric}@iue.tuwien.ac.at

Stanislav Tyaginov and Tibor Grasser Institute for Microelectronics, TU Wien Gußhausstraße 27-29, A-1040 Vienna, Austria Email: {tyaginov|grasser}@iue.tuwien.ac.at Hubert Enichlmair and Jong-Mun Park

Process Development and Implementation Department,

Austriamicrosystems AG, Tobelbader Straße 30,

A-8141 Unterpremstaetten, Austria,

Email: Hubert.Enichlmair@austriamicrosystems.com

Jong-Mun.Park@austriamicrosystems.com

Christoph Jungemann

Institute für Theoretische Elektrotechnik,

RWTH Aachen, 52056 Aachen, Germany

Email: Jungemann@ieee.org

Abstract—We have analyzed the worst-case conditions of hot-carrier induced degradation for high-voltage n- and p-MOSFETs with our model. This model is based on the evaluation of the carrier distribution function along the  $\mathrm{Si/SiO_2}$  interface, i.e. on thorough consideration of carrier transport. The distribution function obtained by means of a full-band Monte-Carlo device simulator is used to calculate the acceleration integral, which controls how effectively the carriers are breaking  $\mathrm{Si}-\mathrm{H}$  bonds. Therefore, we analyze the worst-case conditions using this integral as a criterion. We compare the simulated picture with the experimental one and conclude that the model fits the experimental data precisely well for both transistor types.

#### I. INTRODUCTION

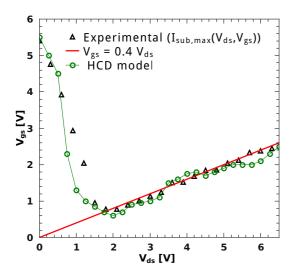

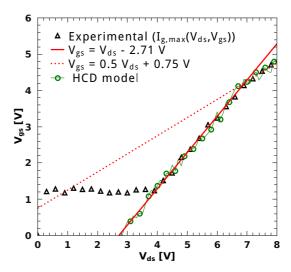

The worst-case conditions (WCC) of hot-carrier degradation (HCD) in the case of a long-channel n-MOSFET are reached when the substrate current  $I_{\text{sub}}$  is at its maximum [1]-[4]. It is usually assumed that this maximum corresponds to the interrelation between gate and drain voltages:  $V_{\rm gs} = (0.4 \div$  $0.5)V_{\rm ds}$ . As for long-channel p-MOSFETs, WCC are achieved at the maximum gate current  $I_{\rm g}$  and such an empirical link between the voltages is not established [5]-[7]. Although the experimental WCC was determined out some time ago, a detailed numerical analysis of the matter is still missing. This is related to lack of a comprehensive model for hot-carrier degradation. At the same time, a predictive diagram reflecting how detrimental these given stress/operating conditions are for the device performance would be of great significance for reliability engineers. Furthermore, representation of such experimental diagrams by an HCD model should serve as a criterion of the model soundness. In this work we apply our physics-based model for hot-carrier degradation [8], [9] in order to represent the experimental color maps depicting the device damage as a function of  $\{V_{\rm gs}, V_{\rm ds}\}$  in the case of high-voltage n- and p-MOSFETs.

### II. EXPERIMENTAL DETAILS

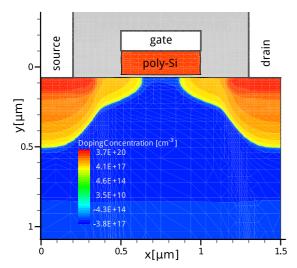

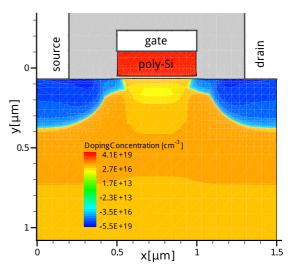

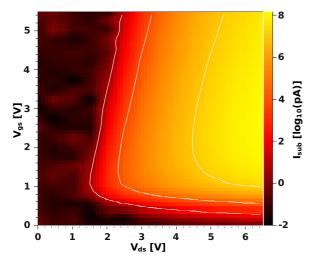

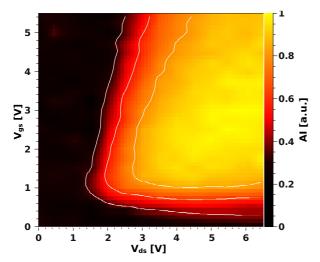

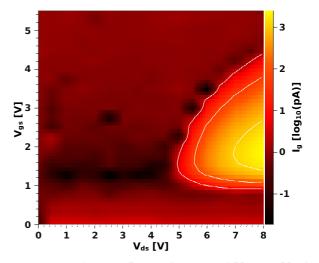

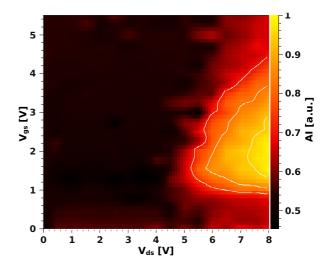

5V n- and p-MOSFETs fabricated on a standard  $0.35\mu\mathrm{m}$  process with a channel length of  $0.5\mu\mathrm{m}$  (the device architectures and the net doping profiles are sketched in Figs. 1,2) have been employed for monitoring the criteria reflecting the severity of HCD. All lateral coordinates x refer to an origin placed at the left edge of the source contact for both devices. Together with a relatively high operation voltage this channel length ensures that the single-electron mechanism of the Si – H bond dissociation is the dominating one [4]. In the case of an n-MOSFET the substrate current as a function of varying  $\{V_{\mathrm{ds}}, V_{\mathrm{gs}}\}$  was recorded and binned onto a color map (Fig. 3). For p-MOSFET we measured  $I_{\mathrm{g}} = I_{\mathrm{g}}(V_{\mathrm{gs}}, V_{\mathrm{ds}})$ , see Fig. 4.

# III. THE APPROACH

To analyze the worst-case conditions we employ our physics-based model for hot-carrier degradation which considers the interplay between single- and multiple-carrier modes of Si-H bond dissociation [8], [9]. Note that in [10] we consider also the damage produced by the channel holes. However, we showed that in the case of the channel length of  $0.5\,\mu\mathrm{m}$  the linear drain current degradation is satisfactorily described only by the electron contribution. Both mechanism of Si-H bond-breakage are controlled by the carrier acceleration integral

$$I_{\text{SC/MC}} = \nu_{\text{SC/MC}} \int_{E_{\text{AL}}}^{\infty} f(E)g(E)\sigma_{\text{SC/MC}}(E)v(E)dE,$$

which is calculated as the reaction cross section  $\sigma_{\rm SC/MC}$  multiplied on the density-of-states g(E) and the carrier velocity v(E), weighted with the carrier energy distribution

Fig. 1: The topology of 5V n-MOSFET with the net doping profile highlighted.

function (DF) f(E) and integrated over energy starting from the threshold value typical for the bond dissociation reaction.

As we discussed in [8], [11] the dose of damage provided by the MC-component is homogeneously distributed over the lateral coordinate. This is because the prefactor in the MCinduced interface state concentration (see [8], [11]) defined by the acceleration integral is already saturated due to the high concentration of relatively "cold" carriers (represented by the low-energy fragment of the DF). As a result, the nonuniform nature of HCD is related to the single-carrier bondbreakage process with the corresponding contribution to the total interface state density  $N_{\rm it}$  localized near the drain end of the gate. Therefore, in order to find the stress conditions corresponding to the worst-case scenario, we suggest to analyze the behavior of the acceleration integral, not considering the interaction between the SC and MC-mechanisms. In literature, one may find other criteria how efficiently carriers interact with the bond, such as the maximum of the electric field, the carrier dynamic temperature, position where the DF demonstrates most extended high-energy tales, etc. However, as we showed in [9], the  $N_{\rm it}$  peak just corresponds to the maximum of the AI and is shifted away with respect to maxima of other quantities.

In order to create the numerical picture for the worst-case conditions the following computational procedure was used. As it was shown in [9] just the position of the AI peak defines the maximum of the interface state density  $(N_{\rm it})$ . Therefore, we use the acceleration integral as a criterion to judge how severe HCD is. In other words, we calculate the AI as a function of  $\{V_{\rm gs},V_{\rm ds}\}$  and produce the color maps (see Figs. 5,6) in the same fashion as Figs. 3,4. The computational procedure implies the following steps. Initially, we vary  $V_{\rm gs}$  and  $V_{\rm ds}$  in the range of 0..6 V and 0..7 (for p-MOSFET the  $V_{\rm ds}$  range is of 0..8V) with the step of 0.2 V. For each pair  $\{V_{\rm gs},V_{\rm ds}\}$  we calculate the set of carrier DFs (i.e. at each point along the Si/SiO $_{\rm 2}$  interface) using a full-band Monte-Carlo device simulator MONJU [12]. This

Fig. 2: The topology of 5V p-MOSFET with the net doping profile highlighted.

information is then used to calculate the dependences of the carrier acceleration integral vs. the lateral coordinate. After processing these dependencies we have plotted the maximum value of the acceleration integral  $I_{\rm SC}$  as a function of  $V_{\rm ds}, V_{\rm gs}$ . Therefore, the whole computational routine contains about 1000 different combinations of stress voltages while each pair  $\{V_{\rm gs}, V_{\rm ds}\}$  includes time expensive Monte-Carlo simulations of the carrier DF. These three-dimensional plots (discussed in details in the next Section) have been further compared with the experimental results and analyzed.

## IV. RESULTS AND DISCUSSION

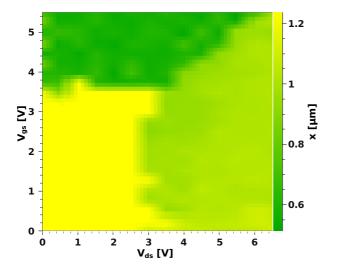

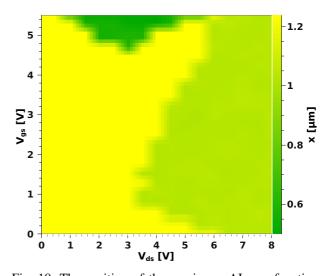

The comparison between Figs. 3,4 and Figs. 5,6 demonstrates a good agreement between experimental and simulated color maps for both types of transistors. We also plotted the dependence of the gate voltage on the drain bias corresponding to the worst-case conditions, see Figs. 7,8. This data are extracted from Figs. 3,4 where  $V_{\rm gs}$  is presented as a function of  $V_{

m ds}$  which is found as the value guaranteeing the maximum of either experimental data ( $I_{

m sub}$  for n-MOSFET and  $I_{

m g}$  for p-MOSFET) or  $I_{\rm SC}$  (simulations with our HCD model) for the chosen value of  $V_{\rm ds}$ . At a drain voltage above 2.0V for the n-MOSFET this dependence follows the law  $V_{\rm gs}=0.4V_{\rm ds}$ typical for this device. Although for the p-MOSFET this dependence is more complicated (Fig. 8), the experimental and simulated pictures are in a good agreement. Finally, the position where the maximum AI is observed, is plotted vs.  $\{V_{\rm gs}, V_{\rm ds}\}$ , see Figs. 9,10. Since the peak of the acceleration integral determines the location of the most severe degradation spot, this graph can be used to predict where the most degraded section of the device is located. Note that these color maps presented in Figs. 9,10 reflect the pattern shown in Figs. 5,6. For instance, the orange area pronounced in Fig. 5 (and bordered by the right contour curve) corresponds to the light green spot in Fig. 9.

Fig. 3: Experimental  $I_{\rm sub}$  as a function of  $V_{\rm gs}$  and  $V_{\rm ds}$  for the n-MOSFET.

Fig. 5: Maximum value of the AI as a function of  $V_{\rm gs}$  and  $V_{\rm ds}$  for the n-MOSFET.

## V. CONCLUSION

We have examined the worst-case conditions of hot-carrier degradation in the case of high-voltage n- and p-MOSFETs. For this purpose we employed our HCD model which is based on a thorough treatment of the carrier distribution function obtained using a full-band Monte-Carlo device simulator, i.e. relies on the direct solution of the Boltzmann transport equation. The carrier acceleration integral was used as a criterion of the degradation severity. We have concluded that our model reproduce the WCC with a reasonable accuracy. Simulated diagrams representing the maximum of the AI as a function of gate and drain voltages well agree with the color maps  $I_{\rm sub} = I_{\rm sub}(V_{\rm gs}, V_{\rm ds})$  for n-MOSFET and  $I_{\rm g} = I_{\rm g}(V_{\rm gs}, V_{\rm ds})$  for p-MOSFET. Finally, our HCD model predicts the position where the most degraded device section is localized (i.e. between the drain end of the gate and the drain).

Fig. 4: Experimental  $I_{\rm g}$  as a function of  $V_{\rm ds}$  and  $V_{\rm gs}$  for the p-MOSFET.

Fig. 6: Maximum value of the AI as a function of  $V_{\rm gs}$  and  $V_{\rm ds}$  for the p-MOSFET.

## REFERENCES

- [1] M. Song, K. MacWilliams, and C. Woo, "Comparison of nMOS and pMOS hot carrier effects from 300 to 77K," *IEEE Trans Electron Dev.*, vol. 44, no. 2, pp. 268–276, 1997.

- [2] J. Wang-Ratkovic, R. Lacoe, K. Williams, M. Song, S. Brown, and G. Yabiku, "New understanding of LDD CMOS hot-carrier degradation and device lifetime at cryogenic temperatures," *International Reliability Physics Symposium*, pp. 312–314, 2003.

- [3] S. Rauch and G. L. Rosa, "CMOS hot carrier: From physics to end of life projections, and qualification," in *Proc. International Reliability Physics Symposium (IRPS)*, tutorial, 2010.

- [4] A. Bravaix and V. Huard, "Hot-carrier degradation issues in advanced CMOS nodes," in *Proc. European Symposium on Reliability of Electron Devices Failure Physics and Analysis (ESREF), tutorial*, 2010.

- [5] W. Qin, W. Chim, D. H. Chan, and C. Lou, "Modelling the degradation in the subthreshold characteristics of submicrometre LDD pMOSFETs under hot-carrier stressing," *Semicond. Sci. Technol.*, vol. 13, no. 5, pp. 453–459, 1998.

- [6] S. Manzini and A. Gallerano, "Avalanche injection of hot holes in the gate oxide of LDMOS," *Solid-State Electron.*, vol. 44, no. 1, pp. 1325– 1330, 2000.

- [7] V. Reddy, "An introduction to CMOS semiconductor reliability," in Proc. International Reliability Physics Symposium (IRPS), tutorial, 2004.

Fig. 7: The interrelation between  $V_{\rm gs}$  and  $V_{\rm ds}$  corresponding to the WCC (n-MOSFET).

Fig. 8: The interrelation between  $V_{\rm gs}$  and  $V_{\rm ds}$  corresponding to the WCC (p-MOSFET).

Fig. 9: The position of the maximum AI as a function of  $V_{\rm gs}$  and  $V_{\rm ds}$  (n-MOSFET).

Fig. 10: The position of the maximum AI as a function of  $V_{\rm gs}$  and  $V_{\rm ds}$  (p-MOSFET).

- [8] S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Enichlmail, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Interface traps density-of-states as a vital component for hot-carrier degradation modeling," *Microel. Reliab.*, vol. 50, pp. 1267–1272, 2010.

- [9] I. Starkov, S. Tyaginov, H. Enichlmair, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Ceric, and T. Grasser, "Hot-carrier degradation caused interface state profile - simulations vs. experiment," *Journal of Vacuum Science and Technology - B*, vol. 29, no. 1, pp. 01AB09–1– 01AB09–8, 2011.

- [10] S. Tyaginov, I. Starkov, O. Triebl, H. Enichlmair, C. Jungemann, J. Park, H. Ceric, and T. Grasser, "Secondary generated holes as a crucial com-

- ponent for modeling of HC degradation in high-voltage n-MOSFET," in *Proc. International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)*, 2011, accepted.

- [11] S. Tyaginov, I. Starkov, O. Triebl, J. Červenka, C. Jungemann, S. Carniello, J. Park, H. Enichlmair, M. Karner, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Hot-carrier degradation modeling using full-band monte-carlo simulations," in *Proc. Interna*tional Symposium on the Physical & Failure Analysis of Integrated Circuits (IPFA), 2010.

- [12] C. Jungemann and B. Meinerzhagen, Hierarchical Device Simulation. Springer Verlag Wien/New York, 2003.