SIMULATION OF SEMICONDUCTOR PROCESSES AND DEVICES Vol. 12 Edited by T. Grasser and S. Selberherr - September 2007

# **Asymmetrical Triple-Gate FET**

Meng-Hsueh Chiang, Jeng-Nan Lin, Keunwoo Kim\*, and Ching-Te Chuang\*

National Ilan University, I-Lan 260, Taiwan, ROC \*IBM T. J. Watson Research Center, Yorktown Heights, NY 10598, USA mhchiang@niu.edu.tw

#### Abstract

A novel triple-gate MOSFET structure with polysilicon gate process is proposed using asymmetrical  $(n^+/p^+)$  polysilicon gates. CMOS-compatible  $V_T$ 's for high-performance circuit applications can be achieved for both nFET and pFET. The superior subthreshold characteristics and device performance are analyzed by three-dimensional numerical simulations. Comparisons of device properties with the midgap metal gate are presented.

# 1 Introduction

The triple-gate (TG) MOSFET has emerged as one of the promising candidates to extend CMOS technology beyond the scaling limit of conventional CMOS technology. The control of short-channel effects (SCEs) has become the major issue for device scaling beyond the 65 nm node [1]-[2]. In multi-gate FETs, thinning the channel film thickness is usually required yet challenging to suppress SCEs. Due to the superior SCEs, flexible body dimension, and manufacturability, the TG FET has been of much interest [1], [3]. Metal-gates with proper work functions, instead of channel doping engineering, have been employed to achieve the desired  $V_T$  in advanced multi-gate structures [4]. For CMOS application, two different work functions are usually required in order to balance the drive currents of nFET and pFET, which leads to technology complexity. In addition, gate work function engineering for multi-V<sub>T</sub> design requires more exotic gate materials. This paper describes an asymmetrical (n<sup>+</sup>/p<sup>+</sup>) poly-gate structure for TG FinFET devices with CMOS-compatible V<sub>T</sub>'s using tilted implantations [5]-[6]. The device characteristics are analyzed using three-dimensional numerical simulations, and compared with metal-gate TG FinFET.

# **2 Proposed Device Structure**

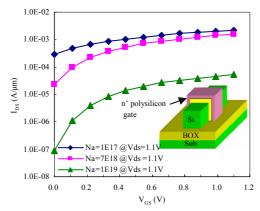

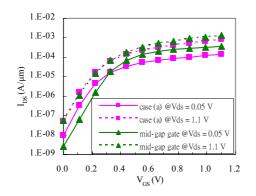

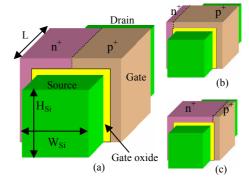

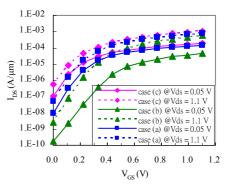

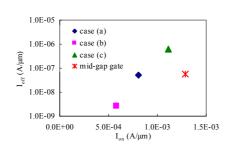

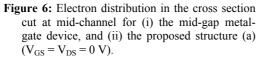

A novel TG FinFET structure compatible with the polysilicon process is proposed. In the conventional dual polysilicon CMOS technology (i.e. n+ and p+ polysilicon for nFET and pFET, respectively), the required channel doping density for TG devices has to be extremely high to achieve proper  $V_T$  (~0.2 V) or I<sub>off</sub> (100 nA/µm), as indicated in Fig. 1. The proposed TG device structure with physically equivalent n<sup>+</sup>polysilicon gate and p<sup>+</sup>-polysilicon gate is shown in Fig. 2(a). Two other possible structures with n<sup>+</sup>/p<sup>+</sup> polysilicon gate offsets are shown in Fig. 2(b) and (c). The gate oxide surrounded by the gate has a uniform thickness (T<sub>ox</sub>). The device structure under study has a cross-sectional body dimension of height (H<sub>Si</sub>) and width (W<sub>Si</sub>). Both H<sub>Si</sub> and W<sub>Si</sub> are assumed equal and are half of the effective channel length for proper SCE control. The total channel width can be defined as 2H + W. Multi-V<sub>T</sub> options can be achieved using different patterns of the n<sup>+</sup>/p<sup>+</sup> polysilicon. We first assess the device I-V characteristics for the three gate structures, as compared with the mid-gap metal-gate device using a 3D numerical tool [7]. All the devices (nFETs) have the same L of 25 nm, Tox of 1.3 nm, and thick buried oxide of 200 nm. In the simulations, Fermi-Dirac statistics, modified local density approximation for carrier confinement, and drift-diffusion transport model with fielddependent mobility were used. Fig. 3 shows the simulated I<sub>DS</sub> vs. V<sub>GS</sub> characteristics for the proposed structure (a) and mid-gap metal-gate device with comparable  $I_{\rm off}$ (~50 nA/ $\mu$ m) set at V<sub>DS</sub> = 1.1 V. To achieve the equal I<sub>off</sub> value, a channel doping density of  $7 \times 10^{18}$  cm<sup>-3</sup> is needed for the proposed structure, whereas an undoped body is used for the near-mid-gap metal-gate device. Due to higher mobility in the undoped channel, the mid-gap metal-gate device gives higher  $I_{on}$  (@V<sub>GS</sub> = V<sub>DS</sub> = 1.1 V). On the other hand, the proposed device exhibits better DIBL characteristics due to the higher vertical field attained by the positive back-gate filed in the asymmetrical device configuration as well as the use of the doped body. The proposed structures with different  $n^+/p^+$  polysilicon gate offsets are compared in Fig. 4, which shows the simulated  $I_{DS}$  vs.  $V_{GS}$  characteristics for the three cases shown in Fig. 2. The same channel doping density  $(7x10^{18} \text{ cm}^{-3})$  is used. Case (b) with larger p<sup>+</sup>-polysilicon portion has the highest V<sub>T</sub>, whereas case (c) with larger n<sup>+</sup>-polysilicon portion has the lowest V<sub>T</sub>. Fig. 5 further shows the I<sub>on</sub> vs. I<sub>off</sub> characteristics for the three poly-gate and the metal-gate devices. The three proposed structures offer a wide range of V<sub>T</sub> selection, thus multiple  $V_T$  can be made.

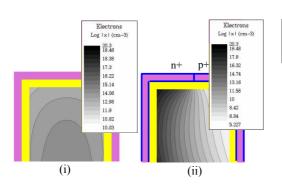

The detailed device characteristics are listed in Table 1. The DIBL values of the proposed cases are much lower than that of the metal-gate device. Fig. 6 shows the inversion carrier distribution in the channel. The electron density is more uniformly distributed for the mid-gap metal-gate device, while it is crowded near the  $n^+$ -gate surface for the proposed structure (a) (results for structures (b) and (c) are not shown, yet similar). Hence, the proposed structures have improved DIBL's, as the carriers are better controlled due to the higher field perpendicular to the predominant  $n^+$ -gate.

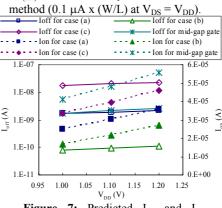

Fig. 7 shows the  $I_{on}$  and  $I_{off}$  sensitivities to  $V_{DD}$ . As expected,  $I_{off}$  for structure (a) is slightly less sensitive than that of the mid-gap metal-gate device due to less DIBL. The  $I_{on}$  dependences on  $V_{DD}$  are similar for the three proposed structures, implying consistent dynamic power scaling when these structures are integrated on the same chip for multi- $V_T$  design. The DIBL advantage is further reflected in Fig. 8. To gain insight into CMOS circuit speed performance, we also simulated C-V characteristics, as shown in Fig. 9, for CV/I comparison. The CV/I<sub>on</sub> value of our proposed structure (case (a)) is about 50% (at  $V_{DD}$  of 1.1V) higher than that of the mid-gap metal-gate one mainly due to lower  $I_{on}$ . However, as  $V_{DD}$  is decreased, the gate capacitance for the proposed scheme decreases faster and hence it is more suitable for low-voltage applications.

# 3 Conclusion

A novel TG MOSFET structure using asymmetrical polysilicon gates is proposed. Due to the superior SCEs, the proposed TG device offers better channel length scalability compared with TG devices with near-mid-gap metal-gates. By changing the patterns/offsets of the  $n^+/p^+$  polysilicon gates, multiple  $V_T$  can be achieved. Hence, this structure can be used in low-power high-performance VLSI.

SIMULATION OF SEMICONDUCTOR PROCESSES AND DEVICES Vol. 12 Edited by T. Grasser and S. Selberherr - September 2007

# Acknowledgements

M.-H. Chiang and J.-N. Lin were partially supported by the National Science Council of Taiwan, ROC under contract NSC95-2221-E-197-021. K. Kim and C. T. Chuang were partially supported by the DARPA contract NBCH30390004.

### References

[1] B. Doyle et al., *Symp. VLSI Tech. Dig.*, p. 133, 2003. [2] *ITRS*, 2004 update (<u>http://public.itrs.net/</u>). [3] J.-W. Yang and J. G. Fossum, *IEEE T-ED*, p. 1159, 2005. [4] Y. K. Choi, *IEDM Tech. Dig.*, pp. 259–262, 2002. [5] K. Kim and J. G. Fossum, *IEEE T-ED*, pp. 294-299, Feb. 2001. [6] J. Kedzierski, et al., *IEDM Tech. Dig.*, pp. 437-440, 2001. [7] Taurus-Device, Synopsis, Inc., Oct. 2005. [8] M. H. Na, et al., *IEDM Tech. Dig.*, pp. 121-124, 2002.

Figure 1: Taurus-simulated  $I_{DS}$  vs.  $V_{GS}$  characteristics for a TG nMOSFET with n<sup>+</sup> polysilicon gate and different dopings (N<sub>a</sub>'s). The inset shows the 3-D structure (not to scale) for simulation (L = 25 nm, gate oxide = 1.3 nm, silicon height = silicon width = 12.5 nm).

Figure 3: Taurus-simulated  $I_{DS}$  vs.  $V_{GS}$  characteristics for the proposed structure (a) and the mid-gap metal-gate device with comparable  $I_{off}$  (~50 nA/µm) set at  $V_{DS} = 1.1$  V.

Figure 2: 3-D view of the proposed triple-gate structures (a), (b), and (c) with different  $n^+/p^+$  polysilicon gate offsets. (The thick buried oxide (BOX) layer underneath is not shown for brevity.)

Figure 4:. Taurus-simulated  $I_{DS}$  vs.  $V_{GS}$  characteristics for the three proposed structures.

### SIMULATION OF SEMICONDUCTOR PROCESSES AND DEVICES Vol. 12 Edited by T. Grasser and S. Selberherr - September 2007

**Figure 5:** I<sub>on</sub> vs. I<sub>off</sub> for the proposed structures and the near-mid-gap metal-gate device.

Figure 8: Predicted  $V_{T(sat)}$  and DIBL vs. L scaling.

| Device                        | Mid-gap                   | Case                      | Case                      | Case                      |

|-------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| type                          | gate                      | (a)                       | (b)                       | (c)                       |

| V <sub>T(sat)</sub> (V)       | 0.16                      | 0.15                      | 0.27                      | 0.08                      |

| $I_{off}\left(A/\mu m\right)$ | 5.76<br>x10 <sup>-8</sup> | 5.16<br>x10 <sup>-8</sup> | 2.52<br>x10 <sup>-9</sup> | 5.34<br>x10 <sup>-7</sup> |

|                               | -                         | -                         | X10                       |                           |

| $I_{on} (A/\mu m)$            | 1.29                      | 8.05                      | 5.80                      | 1.05                      |

|                               | x10 <sup>-3</sup>         | x10 <sup>-4</sup>         | x10 <sup>-4</sup>         | x10 <sup>-3</sup>         |

| $I_{eff}\left(A/\mu m\right)$ | 7.77                      | 4.74                      | 3.05                      | 6.40                      |

| [8]                           | x10 <sup>-4</sup>         | x10 <sup>-4</sup>         | x10 <sup>-4</sup>         | x10 <sup>-4</sup>         |

| DIBL                          | 101                       | 50                        | 82                        | 54                        |

| (mV/V)                        |                           |                           |                           |                           |

| Sub. Swing                    | 90                        | 81                        | 79                        | 89                        |

| (mV/dec)                      |                           |                           |                           |                           |

| CV/I <sub>on</sub>            | 1                         | 1.49                      | 2.00                      | 1.20                      |

| normalized                    |                           |                           |                           |                           |

**Table 1:** Predicted device characteristics<br/>of the proposed and mid-gap metal-gate<br/>devices for comparison ( $V_{DD} = 1.1 \text{ V}$ ).<br/> $V_{T(sat)}$  was extracted by constant current

Figure 7: Predicted  $I_{on}$  and  $I_{off}$  sensitivities to  $V_{DD}$ .

Figure 9: Predicted C-V characteristics.