# Proposal of a physics-based compact model for nanoscale MOSFETs including the transition from drift-diffusion to ballistic transport

Giorgio Mugnaini<sup>1</sup> and Giuseppe Iannaccone<sup>1,2</sup>

<sup>1</sup> Dipartimento di Ingegneria dell'Informazione, Università di Pisa, and <sup>2</sup> IEIIT-CNR,

Via Caruso, 56122 Pisa, Italy,

giorgio.mugnaini@iet.unipi.it, g.iannaccone@iet.unipi.it

# **Abstract**

We present an analytical model for nanoscale MOSFETs capable to describe the transition from drift-diffusion to ballistic transport. We start from a closed-form model of ballistic Fully Depleted SOI (FDSOI) and Double Gate (DG) MOSFETs with non degenerate statistics, and, on the basis of the Büttiker interpretation of dissipative transport in terms of virtual voltage probes, we show that a long channel MOSFET described in terms of drift-diffusion equations can be rigorously represented by a finite chain of ballistic MOSFETs. Such results allow us to recover velocity saturation as a consequence of the ballistic limit, and to propose a novel mobility model.

#### 1 Introduction

The intermediate regime between ballistic and drift-diffusion transport in Field Effect Transistors is a very important issue for the circuit simulation of nanoscale MOSFETs. However, present compact models lack a physical description of such intermediate regime. We intend here to propose a physics-based analytical model, with a small number of parameters, capable to describe in an appropriate way the transition from drift-diffusion to ballistic transport as MOSFETs approach the nanometer scale. We will focus on DG and FDSOI MOSFETs with rectangular confinement in the thin silicon body, neglecting the effects of Fermi-Dirac statistics and assuming the conduc-

silicon body, neglecting the effects of Fermi-Dirac statistics and assuming the conduction band edge approximatively flat. We expect this type of confinement to be predominant in devices with silicon body thickness  $t_{si} < 3$  nm, though it can be useful for MOSFETs with larger  $t_{si}$  in the subthreshold regime.

### 2 Model

If we consider ballistic transport in a thin DGMOSFET with non-degenerate electron gas, we have two hemi-maxwellian carrier populations on the peak of the barrier, therefore:

$$2C_g(V_g - \phi_m + \chi - \phi_c) = Q_b + \frac{qN_c}{2} \left[ \exp\left(-\frac{V_s}{\phi_t}\right) + \exp\left(-\frac{V_d}{\phi_t}\right) \right] \exp\left(\frac{\phi_c}{\phi_t}\right)$$

(1)

where  $C_g$  is the effective gate capacitance,  $\phi_c$  is the electrostatic potential in the channel defined as in Ref. [1],  $V_d$  and  $V_s$  are the drain and source Fermi potentials, respectively,  $N_c$  is the effective density of states summed over all 2D subbands, and  $Q_b$  is the fixed

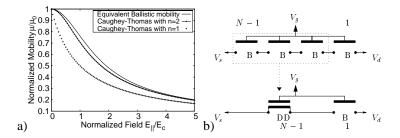

Figure 1: a) Comparison of ballistic chain mobility with the Caughey-Thomas models for electrons and holes. b) Approximate aggregation of first N-1 ballistic transistors in an equivalent Drift-Diffusion. The global circuit can be seen as a macromodel for a device in intermediate transport.

charge per unit area in the body. This equation can be solved in terms of the Lambert W-function [2], and the current  $I_{ds}$  is described by the following expression, that represents one of major results of the present paper:

$$I_{ds} = I^{+} - I^{-} = Q_{n} \mathcal{W} \left( \frac{e^{\frac{V_{g} - V_{s} - V_{T}}{\phi_{t}}} + e^{\frac{V_{g} - V_{d} - V_{T}}{\phi_{t}}}}{2} \right) v_{t} \tanh \left( \frac{V_{ds}}{2\phi_{t}} \right)$$

(2)

Remarkably, the previous description can also be used in the case of local equilibrium transport, i.e. drift-diffusion transport. Indeed, if we place  $V_s = V_d = V_{Fn}$  where  $V_{Fn}$  is the local quasi Fermi potential we obtain the non-degenerate form of local vertical electrostatics proposed in [1]. We find for the mobile charge per unit area in local equilibrium  $Q_m(V_{Fn})$ :

$$V_g - V_T - V_{Fn} = \frac{Q_m}{2C_g} + \phi_t \log \frac{Q_m}{qN_c}$$

(3)

that is the same equation used in the EKV [3] model. Following the approach of Büttiker probes [4], a drift-diffusion MOSFET can be interpreted as a sufficiently long chain of ballistic transistors. We define  $V_k$  the Fermi potential at the k-th contact, and we assume that the k-th contact is placed at  $x_k = k\lambda$  [x = 0 (x = L) corresponds to the source (drain)]. If N is the number of MOSFETs in the chain, current continuity enforced on the ballistic chain imposes N equations, corresponding to writing (2) for each ballistic MOSFET of the chain. If a voltage  $V_{ds}$  is applied to the chain, we expect that each ballistic MOSFET is in the linear region if  $V_{ds}/N << 2\phi_t$  (no high field effects). If N is large enough, we can substitute the discrete  $V_k$ 's with a continuous quasi-Fermi potential  $V_{Fn}$ , so that the ballistic equation (2) becomes:  $I_{ds} = \mu_n Q_m \nabla V_{Fn}$ , that describes drift-diffusion transport with a low field mobility:  $\mu_{no} \equiv \frac{\lambda v_t}{2\phi_t}$ , where  $\lambda$  is the mean free path. If we integrate such equation along the channel, the current of a DD MOSFET is given by:

$$I_d = \frac{\mu_n Q_n \phi_t}{L} \left( \frac{Q_{ms}^2 - Q_{md}^2}{2Q_n^2} + \frac{Q_{ms} - Q_{md}}{Q_n} \right), \tag{4}$$

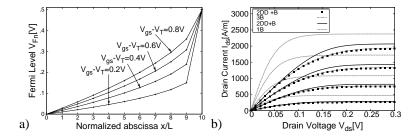

Figure 2: a) Discrete quasi-Fermi potential with N=10 at fixed  $V_{ds}=0.5 \text{V}$  b) Output characteristics of different approximations. 2DD+1B denotes the series of a drift-diffusion with  $L/\lambda=2$  and a ballistic transistor, 3DD denotes a drift-diffusion transistor with  $L/\lambda=3$ ,  $2DD^*+1B$  denotes reduced mobility model [2].  $t_{ox}=2.5$  nm.

where  $Q_{ms}$  ( $Q_{md}$ ) is  $Q_m$  computed at the source (drain), and  $Q_n$  is the normalization charge  $2C_{e}\phi_{t}$ . Equation (4) constitutes the basic structure of EKV-like compact models [3]. When the channel bias of each elementary transistor is larger than  $\phi_t$ , limitation of the maximum current due to ballistic injection at each elementary source results in an effective reduction of the mobility  $\mu_n$ . Mobility  $\mu_n$  is defined as  $\mu_n$  =  $v_t \tanh\left(\frac{\lambda}{2\phi_t} \frac{dV_{Fn}}{dx}\right) / \frac{dV_{Fn}}{dx}$ , where the term  $\frac{2\phi_t}{\lambda}$  can be interpreted as a "critical field", analogous to critical field in the saturation velocity effect. Such phenomenon exhibits a striking similarity with the Caughey-Thomas model for saturation velocity effect, as shown in Figure 1(a). We want to underline that a similar mobility expression was independently proposed by V.Arora in [5]. In order to build a more compact macromodel, we observe in the example in Fig.2(a), that when non-linear transport emerges, it manifests its effects approximatively only on the last ballistic transistor of the chain. This fact suggests that we can aggregate the first N-1 ballistic transistors in an approximate equivalent drift-diffusion transistor with ratio  $L/\lambda = N - 1$ , as schematically represented in Fig.1(b). In Figure 2(b) the output characteristics of a series of N=3ballistic transistors and possible macromodels are compared: the series of one DD and one ballistic transistor has a small but not negligible error. The reason of such error is the approximation of linear transport in the first N-1 transistors. However, it is possible to improve the approximation in the simple way discussed in [2], leading to the line denoted by "DD\* + B". An important point is that no smoothed clamp to an "effective  $V_{ds}$ " has been used, because its role is covered by the ballistic MOSFET.

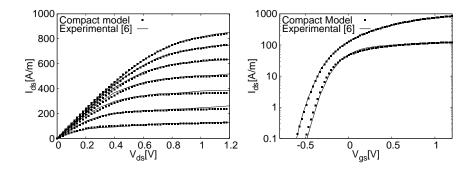

In order to describe the 2D electrostatic effects we introduce two geometrical capacitances  $C_s$ ,  $C_d$  that model coupling to the source and drain, responsible for DIBL. Degradation of mobility at high vertical fields, series resistances and polysilicon depletion effect are introduced in the model [2] and are described by four additional parameters:  $R_s$ ,  $R_d$ ,  $N_p$ ,  $\theta$ . In Figure 3 the characteristics obtained from our proposed model and experimental data for a FinFET with channel length L=80 nm from Ref. [6]. The proposed model is not yet complete, but we believe that the proposed interpretation can be the basis of more physical compact models.

Figure 3: Output (left) and transfer (right) characteristics of a FinFET with L=80 nm: experiments (solid line) and proposed model (squares).

# 3 Conclusions

We have proposed a novel closed-form solution for ballistic ultrathin body MOSFET. Our model is analytical, explicit and inherently symmetrical. We have shown that a long chain of ballistic MOSFETs can be interpreted as a drift-diffusion transistor with constant mobility, while if the device is shorter, a behavior emerges similar to the saturation velocity effect. Then, we have proposed a physics-based macromodel for short MOSFETs is proposed. Because of its structure, this model can be thought as a generalization of EKV-like models [3] such as ACM, USIM, and it is suitable for circuit simulation. We anticipate an extension to Fermi-Dirac statistics [2] that describes a mobility degradation caused by degeneracy. Support from Fondazione Cassa di Risparmio di Pisa and from the EU through the NoE SINANO is gratefully acknowledged.

#### References

- [1] G. Baccarani and S. Reggiani,"A compact double-gate MOSFET model comprising quantum-mechanical and nonstatic effects", IEEE Trans. Electron Devices, vol. 46, pp. 1656-1666, Aug. 1999.

- [2] G. Mugnaini and G. Iannaccone, "Physics-based compact models of nanoscale MOSFETs: Transition from drift-diffusion to ballistic transport", unpublished, 2004.

- [3] C.C.Enz, F.Krummenacher and E.Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-power applications", Analog Integ. Circuits Signal Proc, 1995.

- [4] M.Büttiker, "Role of quantum coherence in series resistors", Phys. Rev. B, no. 33, pp. 3020-3026, 1986.

- [5] V. K. Arora, "Drift diffusion and Einstein relation for electrons in silicon sujected to a high electric field", Applied Physics Letters, vol. 80, no. 20, pp. 3763-3765, May 2002.

- [6] B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C.-Y. Yang, C. Tabery, C. Ho, Q. Xiang, T.-J. King, J. Bokor, C. Hu, M.-R. Lin, and D. Kyser, "FinFET scaling to 10 nm gate length", in IEDM Digest International 2002, Dec. 2002.