# Compact Modeling of Flash Memory Cells Including Substrate-Bias-Dependent Hot-Electron Gate Current

Ken'ichiro Sonoda<sup>1</sup>, Motoaki Tanizawa<sup>2</sup>, Satoshi Shimizu<sup>1</sup>, Yasuhiko Araki<sup>1</sup>, Shinji Kawai<sup>3</sup>, Taku Ogura<sup>3</sup>,

Shin'ichi Kobayashi<sup>3</sup>, Kiyoshi Ishikawa<sup>1</sup>, Yasuo Inoue<sup>4</sup>

<sup>1</sup>LSI Manufacturing Technology Unit, Renesas Technology Corp.

<sup>2</sup>LSI Product Technology Unit, Renesas Technology Corp.

<sup>3</sup>Memory Business Unit, Renesas Technology Corp.

<sup>4</sup>Corporate Strategic Technology Office, Renesas Technology Corp.

<sup>4</sup>-1, Mizuhara, Itami-shi, Hyogo 664-8641, Japan

Email: kenichiro.sonoda@renesas.com

Norihiko Kotani Dept. of Information Technology Hiroshima Int'l Univ. 5-1-1, Hirokoshingai, Kure-shi, Hiroshima 737-0112, Japan

*Abstract*— We propose a compact model for flash memory cells that is suitable for SPICE simulation. The model includes a hotelectron gate current model that considers not only Channel Hot Electron (CHE) injection but also CHannel Initiated Secondary ELectron (CHISEL) injection to express properly substrate bias dependence. Simulation results of both programming and erasing characteristics for 130nm-technology flash memory cells indicate that our model is useful in designing and optimizing circuit for flash memories.

## I. INTRODUCTION

Flash memories are indispensable for mobile equipments because of their nonvolatility. A growing need to process more complicated task on these equipments requires flash memories to have larger capacity and lower power consumption, which leads to finer wafer process and more complex circuit design. Therefore, circuit simulation becomes very important in circuit design and optimization for flash memories.

Programming efficiency, which is defined as a ratio of gate current to programming current, is one of the most important factor for flash memories to determine power consumption and programming speed. The programming efficiency of flash memory cells which utilize hot-electron injection to program is enhanced by applying substrate bias[1][2][3][4]. Mechanisms of the enhancement by substrate bias have been investigated from device physics perspective of view by measurements[5][6][7] and simulations[8][9]. From circuit level perspective of view, some work has been done to construct a compact model for the substrate-bias-dependent gate current[10], but a closed-form model has not been proposed yet. In this work, we propose a SPICE friendly compact model for gate current and show simulation results of the programming/erasing characteristics of a flash memory cell.

## II. MODELING

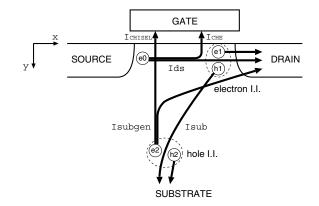

A flash memory cell has a floating gate (FG) between a control gate (CG) and a channel of an MOSFET. Electrons are

injected into the floating gate in program mode, whereas they are released in erase mode. These operations are expressed by an equivalent circuit of an MOSFET and a capacitor with two current sources as shown in Fig. 1[11][12]. Model parameters for  $I_{\rm ds}$  and  $I_{\rm sub}$  of the MOSFET are extracted to fit measurement data of a dummy cell, in which bias can be directly applied to the floating gate. Capacitance between FG and CG is extracted to fit a measured coupling coefficient  $r_{\rm cp} \equiv \Delta V_{\rm FG}/\Delta V_{\rm CG}$ . Gate currents,  $I_{\rm gd}$  and  $I_{\rm gb}$ , are described below.

## A. Hot-Electron Injection

A gate current in program mode is expressed as

$$I_{\rm gd} = I_{\rm CHE} + I_{\rm CHISEL},\tag{1}$$

where  $I_{\text{CHE}}$  and  $I_{\text{CHISEL}}$  are injection currents by Channel Hot Electron (CHE) and CHannel Initiated Secondary ELectron (CHISEL), respectively. These components, which are shown in Fig. 2, will be modeled using a lucky-electron model[13][14]. Based on the lucky-electron model, the probability of an electron acquiring the sufficient kinetic energy from the electric field, E, and retaining the appropriate momentum after elastic collision is expressed as [14]  $p_{ini}(E) =$  $(E\lambda/4\Phi_{\rm b})\exp(-\Phi_{\rm b}/E\lambda)$ , where  $\lambda$  is the inelastic scattering mean-free-path of the hot electron. The effective barrier height  $\Phi_{\rm b}$  including the barrier lowering effects due to the image field and the tunneling is expressed as[14]  $\Phi_{\rm b}(E_{\rm ox}) = \Phi_{\rm b0} \Phi_{\rm b1}\sqrt{E_{\rm ox}} - \Phi_{\rm b2}E_{\rm ox}^{2/3}$  when  $E_{\rm ox} > 0$  and  $\Phi_{\rm b}(E_{\rm ox}) = \Phi_{\rm b0}$ when  $E_{\rm ox} < 0$ , where  $E_{\rm ox} \equiv (V_{\rm gs} - V(x) - \phi_{\rm wf})/t_{\rm ox}$  is the electric field in the gate dielectric film and  $\phi_{wf}$  is the work-function difference between silicon substrate and gate electrode.

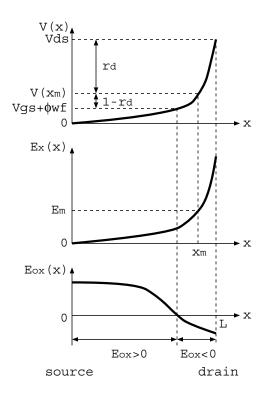

The CHE component comes from energetic channel electrons which are accelerated by channel electric field. The channel potential, V(x), in the velocity saturation region is proportional to  $\exp(x/\ell_c)$ , and the channel electric field  $E_x$ is expressed as  $E_x = (V(x) - V_{dsat})/\ell_c$ , where  $\ell_c$  is the characteristic length which is determined by the thickness of the gate dielectric film and the drain-substrate junction depth[15]. An electron which surmounts the potential barrier is swept into the gate electrode in the region where  $E_{ox} > 0$ , whereas it may be pushed back to the channel in the region where  $E_{\rm ox} < 0$ [16]. The injection, however, occurs in the latter region because some electrons have momentum which is large enough to reach the gate electrode against the electric field in the gate dielectric film. As shown in Fig. 3, the channel potential is  $V_{\rm gs} + \phi_{\rm wf}$  at the point where  $E_{\rm ox} = 0$ , and it increases monotonically toward  $V_{\rm ds}$  along the channel direction. The channel potential at the critical point,  $x = x_{\rm m}$ , beyond which the electron is pushed back, is between  $V_{\rm gs} + \phi_{\rm wf}$ and  $V_{\rm ds}$ . We express the channel potential at the point as  $V(x_{\rm m}) = r_{\rm d}(V_{\rm gs} + \phi_{\rm wf}) + (1 - r_{\rm d})V_{\rm ds}$  using the fitting parameter  $r_{\rm d} \leq 1$ . The electric field at the point  $x_{\rm m}$  is, therefore,  $E_{\rm m} = (r_{\rm d}(V_{\rm gs} + \phi_{\rm wf}) + (1 - r_{\rm d})V_{\rm ds} - V_{\rm dsat})/\ell_{\rm c}$ when  $V_{\rm ds} > V_{\rm gs} + \phi_{\rm wf}$  and  $E_{\rm m} = (V_{\rm ds} - V_{\rm dsat})/\ell_{\rm c}$  when  $V_{\rm ds} < V_{\rm gs} + \phi_{\rm wf}$ . Integrating the product of the channel current  $I_{\rm ds}$  and the injection probability  $p_{\rm inj}$  from x = 0 to  $x = x_{\rm m}$ along the channel, the gate current by CHE injection is

$$I_{\rm CHE} = A_{\rm d} I_{\rm ds} \left(\frac{\lambda E_{\rm m}}{\Phi_{\rm bd}}\right)^2 \exp\left(-\frac{\Phi_{\rm bd}}{\lambda E_{\rm m}}\right),\tag{2}$$

where  $\Phi_{\rm bd} = \Phi_{\rm b}(E_{\rm ox}(x_{\rm m}))$  and  $A_{\rm d}$  is a fitting parameter.

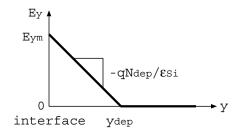

The CHISEL component comes from energetic electrons which are generated by hole impact ionization in the substrate and accelerated by vertical electric field. The generated current by hole impact ionization in the substrate,  $I_{\rm subgen}$ , is calculated by integrating hole impact ionization coefficient  $\alpha_{\rm h} = \alpha_{\rm h0} \exp(-\beta_{\rm h}/E)$ [17] along the current path of the substrate current,  $I_{\rm sub}$ . Assuming the electric field to decrease linearly from its maximum value  $E_{\rm db}$  along the current path of  $I_{

m sub}$ , the current  $I_{

m subgen}$  is expressed as  $I_{\rm subgen} \propto I_{\rm sub}(E_{\rm db}/\beta_{\rm h}) \exp(-\beta_{\rm h}/E_{\rm db})$ , where  $E_{\rm db}$  =  $\sqrt{2qN_{\rm dep}(\phi_{\rm s}-V_{\rm bd})}/\epsilon_{\rm Si}, \phi_{\rm s}=2(kT/q)\log(N_{\rm dep}/n_{\rm i}), N_{\rm dep}$ is the channel doping concentration,  $\epsilon_{Si}$  is the dielectric constant of silicon, and  $n_i$  is the intrinsic carrier concentration. The vertical electric field, which accelerates electrons of  $I_{\rm subgen}$  is determined by the Poisson equation dE/dy = $qN_{\rm dep}/\epsilon_{\rm Si}$ . Approximating  $N_{\rm dep}$  to be constant, the vertical electric field linearly depends on the depth as shown in Fig. 4. Integrating the product of the current  $I_{subgen}$  and the injection probability  $p_{inj}$  along the current path, the gate current by CHISEL injection is expressed as

$$I_{\text{CHISEL}} = A_{\text{s}} I_{\text{sub}} \left(\frac{E_{\text{db}}}{\beta_{\text{h}}}\right)^2 \exp\left(-\frac{\beta_{\text{h}}}{E_{\text{db}}}\right) \\ \times \left(\frac{\lambda E_{\text{ym}}}{\Phi_{\text{bs}}}\right)^3 \exp\left(-\frac{\Phi_{\text{bs}}}{\lambda E_{\text{ym}}}\right), \quad (3)$$

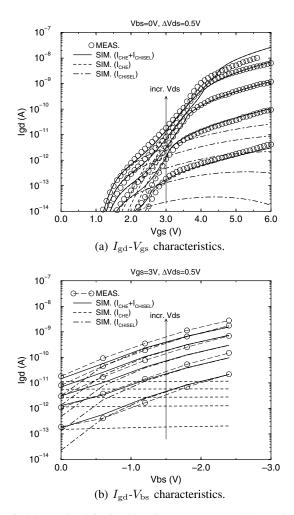

where  $E_{\rm ym} = \sqrt{2qN_{\rm dep}(\phi_{\rm s} - V_{\rm bs})/\epsilon_{\rm Si}}$ ,  $\Phi_{\rm bs} \equiv \Phi_{\rm b}(E_{\rm ox}(0))$ and  $A_{\rm s}$  is a fitting parameter. Measured and simulated hot-electron gate currents,  $I_{\rm gd}$ , are shown in Fig. 5. The proposed model gives proper drain, gate and substrate bias dependence. From the simulated data, CHE is dominant for the total current,  $I_{\rm CHE} + I_{\rm CHISEL}$ , when the gate voltage is high as shown in Fig. 5 (a). As the gate voltage becomes low, the CHE component has less effect than the CHISEL component, because the electric field in the gate dielectric film near the drain changes from attractive to repulsive which suppresses CHE injection[7][9][16]. The CHE component is independent of the substrate bias, as shown in Fig. 5 (b), because the chanel potential, V(x), and the channel electric field,  $E_{\rm m}$ , are insensitive to the substrate bias. The CHISEL component, on the other hand, increases as the substrate bias goes negative owing to the dependence of  $E_{\rm db}$ and  $E_{\rm ym}$  on  $V_{\rm bd}$  and  $V_{\rm bs}$ , respectively.

#### B. Fowler-Nordheim Tunneling

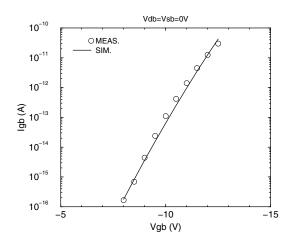

A gate current in erase mode,  $I_{\rm gb}$ , is governed by Fowler-Nordheim (FN) tunneling. We use the BSIM4 gate tunneling current model in accumulation mode[18],  $I_{\rm gbacc}$ , to express the FN tunneling current because it is implemented in most simulators for industrial use. The BSIM4 gate tunneling current model is based on FN tunneling model and contains some modification to suit direct tunneling[19]. In the erase bias range, measured tunneling current is well expressed by the BSIM4 gate tunneling current model as shown in Fig. 6.

### **III. RESULTS AND DISCUSSION**

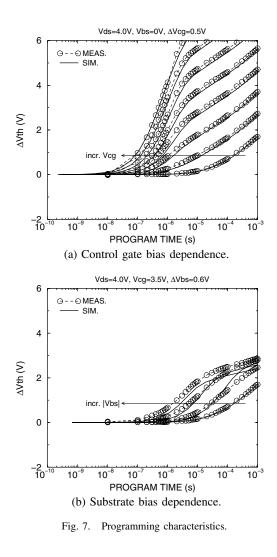

Experimental and simulated programming characteristics for 130nm-technology flash memory cells are shown in Fig. 7. The threshold voltage shift,  $\Delta V_{\rm th}$ , in the simulation is calculated using the shift of floating gate potential and the coupling coefficient. A good agreement is obtained for every control gate voltage. Applying substrate bias improves programming efficiency and leads to shorter programming time owing to CHISEL injection, which is properly expressed by our model.

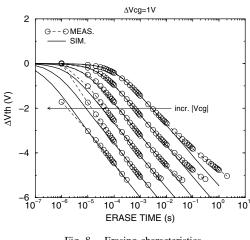

Erasing characteristic is also simulated and compared with experimental data in Fig. 8. A good agreement is obtained for every control gate voltage using common BSIM4 model.

The simulation results of both programming and erasing indicate that our model is useful in designing and optimizing circuits including flash memory cells.

#### IV. CONCLUSION

We have proposed a compact model for flash memory cells including a substrate-bias-dependent hot-electron gate current model. The hot-electron gate current model is based on the lucky-electron model, and substrate bias dependence is properly incorporated in it. The tunneling gate current is expressed by the BSIM4 tunneling gate current model. Simulation results of both programming and erasing characteristics have been shown to validate our model.

#### REFERENCES

- J. D. Bude et al., "EEPROM/Flash Sub 3.0V Drain-Source Bias Hot Carrier Writing," IEDM Tech. Dig., pp. 989–991, 1995.

- [2] J. D. Bude et al., "Secondary Electron Flash a High Performance, Low Power Flash Technology for 0.35μm and Below," *IEDM Tech. Dig.*, pp. 279–282, 1997.

- [3] S. Mahapatra et al., "CHISEL Flash EEPROM–Part I: Performance and Scaling," IEEE Trans. Electron Devices, vol. 49, pp. 1296–1301, 2002.

- [4] S. Mahapatra et al., "CHISEL Flash EEPROM–Part II: Reliability," IEEE Trans. Electron Devices, vol. 49, pp. 1302–1307, 2002.

- [5] D. Esseni et al., "Experimental Signature and Physical Mechanisms of Substrate Enhanced Gate Current in MOS Devices," *IEDM Tech. Dig.*, pp. 579–582, 1998.

- [6] D. Esseni et al., "A Better Understanding of Substrate Enhanced Gate Current in VLSI MOSFET's and Flash Cells–Part I: Phenomenological Aspects," IEEE Trans. Electron Devices, vol. 46, pp. 369–375, 1999.

- [7] L. Selmi et al., "A Better Understanding of Substrate Enhanced Gate Current in VLSI MOSFET's and Flash Cells–Part II: Physical Analysis," *IEEE Trans. Electron Devices*, vol. 46, pp. 376–382, 1999.

- [8] J. D. Bude, "Gate Current by Impact Ionization Feedback in Sub-Micron MOSFET Technologies," Symp. VLSI Tech. Dig., pp. 101–102, 1995.

- [9] J. D. Bude et al., "Monte Carlo Simulation of the CHISEL Flash Memory Cell," IEEE Trans. Electron Devices, vol. 47, pp. 1873–1881, 2000.

- [10] L. Larcher et al., "A New Analytical Model of Channel Hot Electron (CHE) and CHannel Initiated Secondary ELectron (CHISEL) Current Suitable for Compact Modeling," *Modeling and Simulation of Microsys*tems 2002, pp. 738–741, 2002.

- [11] F. Gigon, "Modeling and Simulation of the 16Megabit Eprom Cell for Write/Read Operation with a Compact Spice Model," *IEDM Tech. Dig.*, pp. 205–208, 1990.

- [12] S. S. Chung et al., "A Spice-Compatible Flash EEPROM Model Feasible for Transient and Program/Erase Cycling Endurance Simulation," *IEDM Tech. Dig.*, pp. 179–182, 1999.

- [13] C. Hu, "Lucky-Electron Model of Channel Hot Electron Emission," IEDM Tech. Dig., pp. 22–25, 1979.

- [14] S. Tam et al., "Lucky-Electron Model of Channel Hot-Electron Injection in MOSFET's," IEEE Trans. Electron Devices, vol. ED-31, pp. 1116– 1125, 1984.

- [15] P. K. Ko, "Approaches to Scaling," VLSI Electronics Microstructure Science, vol. 18, ed. N. G. Einspruch and G. S. Gildenblat, San Diego, Academic Press, 1989.

- [16] B. Eitan et al., "Hot-Electron Injection into the Oxide in n-Channel MOS Devices," IEEE Trans. Electron Devices, vol. ED-28, pp. 328–340, 1981.

- [17] R. v. Overstraeten *et al.*, "Measurement of the Ionization Rates in Diffused Silicon *p-n* Junctions," *Solid-State Electron.*, vol. 13, pp. 583– 608, 1970.

- [18] X. Xi et al., BSIM4.2.1 MOSFET Model-User's Manual, http://www-device.eecs.berkeley.edu/~bsim3/bsim4.html, 2001.

- [19] K. F. Schuegraf et al., "Ultra-thin Silicon Dioxide Leakage Current and Scaling Limit," 1992 Symp. VLSI Tech. Dig., pp. 18–19, 1992.

CONO

S o− Igb

Fig. 2. Schematic diagram of generation mechanisms of gate current during programming. CHE and CHISEL components correspond to  $I_{\rm CHE}$  and  $I_{\rm CHISEL}$ , respectively.

Fig. 3. Schematic diagram of the channel potential, V(x), the electric field along the channel,  $E_x(x)$ , and the vertical electric field in the gate insulator,  $E_{ox}(x)$  along the channel direction.

ç

В

Fig. 4. Schematic diagram of the vertical electric field in the silicon substrate.

Fig. 5. Measured and simulated hot-electron gate current. Measured current is obtained by differenciating measured programming characteristics with time.

Fig. 6. Measured and simulated tunneling gate current. Measured current is obtained by differenciating measured erasing characteristics with time.

Fig. 8. Erasing characteristics.