# Influence of the S/D architecture on the V<sub>T</sub> of deep submicron MOSFETs

Serge Biesemans<sup>a</sup> and Kristin De Meyer<sup>a,b</sup>

<sup>a</sup> ASP-division, IMEC, Kapeldreef 75, B-3001 Leuven, Belgium <sup>b</sup> ESAT, KULeuven, Kardinaal Mercierlaan 94, B-3001 Leuven, Belgium

#### Abstract

In this paper, the influence of the source/drain (S/D) architecture on the short channel effect (SCE) and the device performance (through  $R_s$ ) is investigated using both experimental and simulation results. While most existing models relate the SCE and performance only to the oxide thickness ( $T_{ox}$ ) and substrate doping ( $N_{sub}$ ), we show that there exists a universal curve for the threshold voltage roll-off ( $\Delta V_T$ ) for various different S/D profiles. The question of which 'L' should be taken in SCE models is addressed.

# Introduction

As MOSFET devices continue to shrink, the ability to simulate correctly the device characteristics becomes more difficult. Especially for devices with channel lengths around 100 nm, the accuracy with which the material thickness and the doping profiles have to be known, is very high. The SIMS technique can provide vertical doping profiles with an accuracy as good as 5%. However, no direct information is available by using a physical characterization technique to gain information of the exact 2D profile of the S/D structure, although some effort is undertaken. Furthermore, the dependence of the lateral S/D profile on the SCE has not been investigated at all. While most SCE models for the V<sub>T</sub> include correctly  $T_{ox}$  and  $N_{sub}$ , no information regarding the lateral S/D junction profile is included.

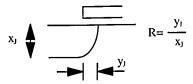

Here, we use the results of the work of [1] where a calibration of the device simulator MEDICI was undertaken. A good quantitative agreement with experiment for a complete Larray, for poly gate lengths ranging from 10  $\mu$ m down to 0.08  $\mu$ m, has been achieved. The simulations performed are done for nMOSFETs with 5 nm gate oxide. The main parameter for bookkeeping is the metallurgical channel length L<sub>met</sub>. The same vertical As extension profile has been used but with different values for the ratio R, shown in Fig.1. Although this procedure of creating a 2D n+ profile out of a 1D SIMS profile is somewhat arbitrary, it is ideal for studying its result on the device characteristics. It can answer the questions like 'what happens if I make my profile steeper ?'', or "what is an optimum S/D profile ?"

Fig.1 The ratio R quantifies how far a certain vertical doping profile extends laterally

This investigation can then be followed by a study using a process simulator in order to find the process conditions to be able to actually fabricate the optimum S/D profile.

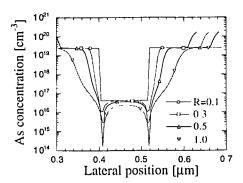

The physical gate length  $L_g$  has been adapted so to end up with the same  $L_{met}$ . The lateral doping profiles for 4 ratios (R=0.1/0.3/0.5/1.0) are shown in Fig.2 for a device of  $L_{met}=120$  nm. The influence of the steepness of the lateral doping profile on the SCE and the parasitic S/D resistance (R<sub>s</sub>) will be investigated next.

Fig.2 Four different lateral doping profiles used to study the influence of the steepness of the profile

### **Results and discussion**

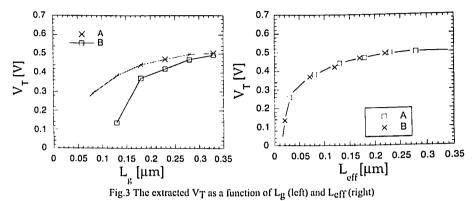

We use a modified Shift&Ratio algorithm [2], [3] to extract the V<sub>T</sub>, the effective channel length  $L_{eff}$  and the R<sub>s</sub> from the I<sub>ds</sub>-V<sub>gs</sub> characteristics in the linear regime (V<sub>ds</sub>=20 mV). We start by reporting the results for experimentally made nMOSFET [4]. Two devices are taken who are identical except in the As extension dose. Device 'A has a dose of 1E14 cm<sup>-2</sup> while device 'B' has a dose of 9E14 cm<sup>-2</sup>. Fig.3 (left) shows the extracted V<sub>T</sub> as a function of the physical poly Si gate length L<sub>g</sub> while Fig.3 (right) plots the same data but as a function of the electrical channel length L<sub>eff</sub>. It can be seen that, although the difference in dose is nearly one order of magnitude, the data follow essentially one and the same curve. The authors do not know of any model analytical model which can distinguish between the two cases of Fig.3. As a result, this phenomenon is not entirely understood. It is clear that L<sub>eff</sub> is the important parameter which serves the same importance as E<sub>eff</sub> for the universal mobility curve. The L<sub>eff</sub> parameters

contains the information of the lateral S/D profile and can be determined through  $I_{ds}-V_{gs}$  measurements.

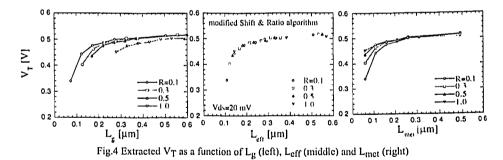

Next, we will try to reproduce this result using simulation data with the profiles of Fig.2. The results of the V<sub>T</sub> extraction in the linear regime are shown in Fig.4 as a function of L<sub>g</sub>, L<sub>eff</sub> and L<sub>met</sub>. Only as a function of L<sub>eff</sub>, we obtain a universal V<sub>T</sub>-L<sub>eff</sub> curve. This indicates that in the SCE models, it is the L<sub>eff</sub> which has to be used and not L<sub>g</sub> or L<sub>met</sub>. Under normal circumstances, L<sub>met</sub><L<sub>eff</sub><L<sub>g</sub>.

It is interesting to note that for a fixed  $L_{met}$ , it is preferable to have less steep profiles. In this way, the depletion layer depth created by the S/D spans mainly the S/D area itself and

penetrates less the electrical channel.

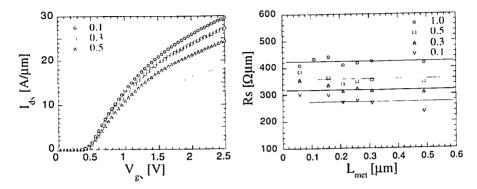

To investigate the influence of the lateral S/D profile on the device performance, we have plotted the  $I_{ds}$  and the extracted  $R_s$  in Fig. 5 for  $L_{met}=0.12 \ \mu m$  and  $V_{ds}=20 \ mV$ .

The  $R_s$  has different contributions like contact, diffusion, spreading and accumulation resistance [5]. The difference between the various profiles can be fully attributed to the

spreading and accumulation resistance which is located mainly under the gate. It is noted, however, that the steepness does not alter the total  $R_s$  dramatically. The values range between 280 and 420  $\Omega\mu$ m. The variation in the current is also influenced by the L<sub>eff</sub>, which is longer if the ratio R increases. This can be seen especially around V<sub>T</sub> where the Rs has little influence. Here, the slope is smaller due to a larger L<sub>eff</sub>.

Fig.5 (left)  $I_{ds}$ -V<sub>gs</sub> curve for Vds=20 mV and various values for R, (right) extracted R<sub>s</sub> for the four different profiles under study

Depending on the specific requirements of the device, this study shows again the well known trade-off between SCE and performance, but includes the effect of the lateral S/D profile. This study allows to find out what the optimum steepness of this profile is to comply with a given set of specifications on the saturation and leakage current. It is clear that a steep profile has the highest I<sub>sat</sub> but also suffers most from SCE. An optimum can be found. It is then up to the process engineer to find out how this profile can actually be fabricated.

## References

[1] S. Biesemans, K. De Meyer, proceedings SISPAD, p.46, 1996

- [2] S. Biesemans, S. Kubicek, K. De Meyer, Symposium VLSI Technology, p.166, 1996

- [3] S. Biesemans, A. Nackaerts, "m-S&R", demo software package for MAC and PC

- [4] S. Kubicek, S. Biesemans, K. De Meyer, Symposium VLSI Technology, p.105, 1995

- [5] K.K. Ng, W. T. Lynch, IEEE Trans. on Electron Devices, p.965, July 1986