SIMULATION OF SEMICONDUCTOR DEVICES AND PROCESSES Vol. 3 Edited by G. Baccarani, M. Rudan - Bologna (Italy) September 26-28, 1988 - Tecnoprint

# IMPACT4 - A GENERAL TWO-DIMENSIONAL MULTILAYER PROCESS SIMULATOR

B. Baccus, D. Collard, E. Dubois and D. Morel

Institut Supérieur d'Electronique du Nord 41, Boulevard Vauban, 59046 LILLE Cedex, FRANCE

### SUMMARY

A new two-dimensional multilayer process simulator based on finite element method has been developed to accuratly study advanced silicon technologies. The basic processing steps simulation are presented and numerical problems arising from the multilayer structures are outlined. Finally, the capabilities of the program are demonstrated with the simulation of a self-aligned polysilicon bipolar transistor.

## INTRODUCTION

The silicon technology has evolved from quasi one-dimensional (1D) structures to two-dimensional (2D) devices where lateral effects become increasingly important. Moreover, the development of silicon processing towards multilayer structures is well illustrated by polysilicon emitter bipolar transistor (Tang, 1982). This evolution of VLSI devices requires the use of very accurate and powerfull simulations tools. The complexity in process simulation has to deal with three parameters: the multi-dimensional aspects of the devices, the number of layers or materials that have to be considered and finally the refinement degree of the process models.

2D simulators use to solve the impurity diffusion in silicon (Collard, 1986) or are restricted to silicon-silicon oxide systems (Borucki, 1985). Multilayers 2D programs are devoted to topology simulations (Oldham, 1980).

The purpose of this paper is to present a new 2D process simulation approach that covers both topology simulation and doping profile calculation in multilayer structures with an unique program : IMPACT4. Developed from previous successful results (Collard, 1986 and 1987), IMPACT4 main characteristics are:

- 1) Handling of 6 materials currently used in fabrication technology : Si, Si-Poly,  $SiO_2$ ,  $Si_3N_4$ , Al and resist. Up to 10 layers can be simulated simultaneously.

- 2) Full integration of topology calculations within other usual processing steps simulations.

- 3) Ion implantation and diffusion simulations with independent and adjustable models for each material.

- 4) General data organization specialized for finite element method (FEM).

- 5) Modeling of complex problems such as the polysilicon-silicon interface or the trench etching process.

#### PROCESS STEPS AND NUMERICAL ASPECTS

#### Mesh generation

One of the main problem is the capability to handle arbitrarily shaped structures. This is partly solved by an original data organization. The data used during calculations are classified into several entities (nodes, layers, material properties...) and are accessed without any hierarchy.

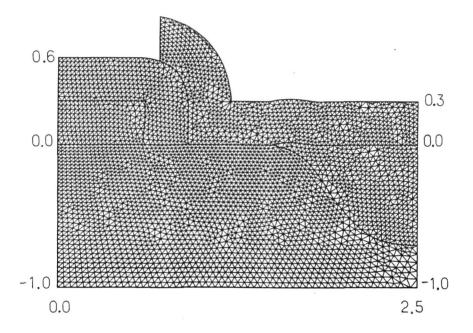

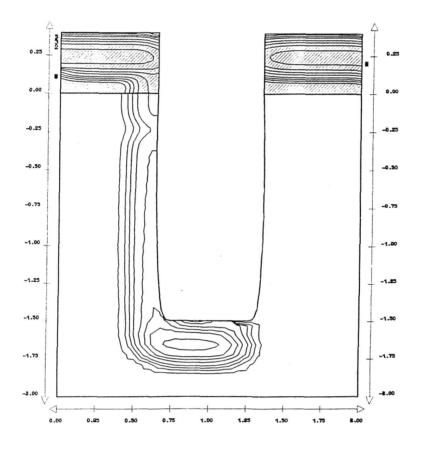

The spatial discretization is also of major importance. FEM has been chosen and 3-noded triangles are used due to their flexibility in complex shapes description. An example of mesh generation is shown in fig.1 for the case of a self-aligned polysilicon bipolar transistor, including two levels of polysilicon (extrinsic base and emitter formations). The mesh generator MSHPTS (Hecht, 1986) from INRIA software library is used in IMPACT4 and has proved to be robust enough to be adapted to any kind of multilayer structure.

# Etching and deposition sceps

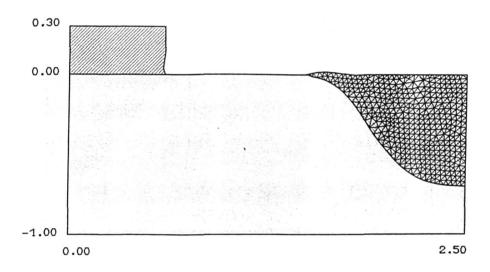

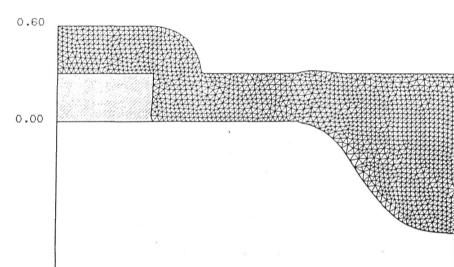

layer management is performed by the topology The simulation module, accordingly to the etching or deposition steps. The well-known string model is used and special algorithmic problems have been solved in order to take into account the general multi-layer aspect. The compatibility with mesh generation has been also carefully studied: the string model points are also the surface vertices of the FEM triangulation. This approach has been found to guaranty a good compromise between the precision in shape definition and the points spacing requirements for mesh generation. This method is well illustrated in fig. 2 in wich the formation steps of structure of fig. 1 are detailed. Isotropic and the anisotropic components can be mixed to reproduce dry etching processes.

Fig. 1: Mesh generation in a self-aligned polysilicon emitter bipolar transistor including two levels of polysilicon, a sidewall spacer and Full-Rox isolation.

Fig. 2a: Original structure including Full-Rox isolation and the first polysilicon level.

Fig. 2b: Oxide deposition for the sidewall spacer. A single layer of oxide remains.

Fig. 2c: Anisotropic etching of silicon oxide. The emitter window is defined and the initial oxide layer is splitted.

## Ion implantation

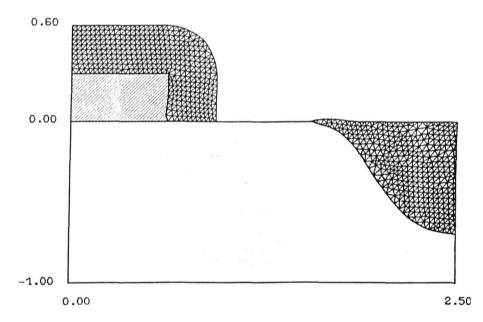

The ion implantation module uses the dose matching model (Ryssel, 1983) to accuratly solve the multilayer target problem and an original 2D formulation has been developed to extend it to 2D problems. As the simulation of tilted implant increasingly important , this possibility has been becomes implemented illustrated in fig.3 with a trench and is structure. The silicon RIE etching through an oxide window has been simulated with sophisticated models including the effects of ions and radicals (Yamamoto, 1987). This is followed by a tilted implant of boron. The resulting contours show the 7° sensibility of the 2D multilayer calculation.

Fig. 3:  $7^{\circ}$  tilted implant in a trench structure with oxide masks.

# Diffusion

As dopant exchanges between layers are of prime importance, the diffusion equation has to be solved in all layers, with appropriate boundary conditions. The FEM formulation is based on the classical Galerkin procedure and the linear matrix system is directly set up by the Newton-Raphson method:

(1)

$$[A].[\Delta C] = [B]$$

in which [A] is the jacobian matrix,  $[\Delta C]$  the nodal concentrations correction vector and [B] the residual vector. The temporal discretization is assumed by an incomplete implicit scheme. The linear system resolution is performed by an incomplete Cholesky decomposition followed by a conjugate gradient method.

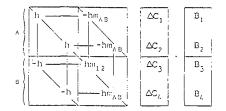

Prior to the ILDU decomposition, an unknown scaling is necessary in order to reduce the bad jacobian conditionement introduced by the equilibrium segregation condition at the interfacial nodes (fig.4). The jacobian symmetry is recovered by dividing the rows and multiplying the unknowns by the segregation coefficient between a given material and silicon as shown in fig.5. With this method, the ILDU-CG exhibits a rapid convergence even when large time steps are used. This property was verified by eigenvalues calculations.

$F_{1,m_3} = 2 h (C_1 - r_{AB} C_3)$  $F_{2m_1} = 1 h (C_2 - r_{AB} C_1)$

Fig. 4: Introduction of the segregation flux term in the jacobian matrix.

${\rm m}_{\rm AB}$  : segregation coefficient between materials A and B.

h : boundary transport rate.

Fig. 5: Scaling of the jacobian matrix.

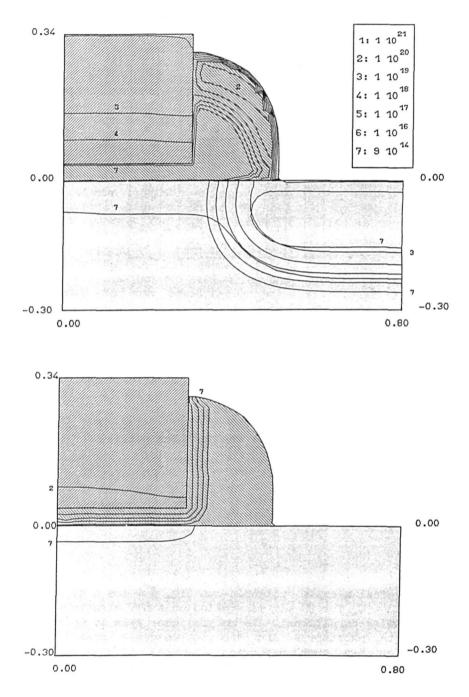

A typical example is shown in fig. 6 where a diffusion step at 1000°C for 30 min is applied on a MOS structure with the following conditions: the polysilicon gate is uniformly doped with phosphorus and the source-drain arsenic ion implantation has been performed. Several effects can be examined : the arsenic diffusion in silicon with segregation effect at the interface of the sidewall spacer, the slight diffusion in the oxide with evaporation, and the coupling with boron in silicon (Fig. 6a). On the other hand, the initial condition in the polysilicon gate implies the diffusion of phosphorus in the gate oxide and also in silicon under the gate (Fig. 6b).

Fig. 6: Diffusion in a MOS device for 30 min at 1000°C in neutral ambient. a) Arsenic and boron contours. b) Phosphorus contours.

### APPLICATION

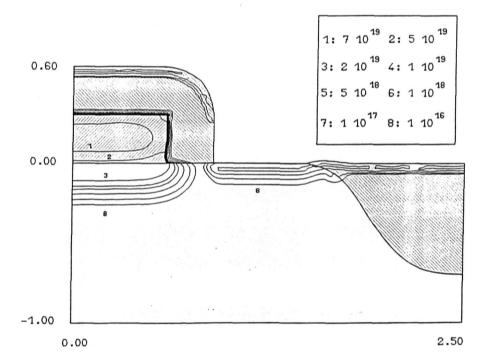

Tn this section, the possibilities of IMPACT4 are illustrated with the simulation of a polysilicon bipolar This example introduces complex 2D multilayer transistor. effects. The structure of fig.2 is used after the definition of the emitter window. As the lateral encroachment of the extrinsic base in the transistor active area is of major importance for electrical characteristics, this region must be carefully simulated. Starting from fig. 2c, boron is first diffused from polysilicon by an annealing at 950°C for 40 mn. The intrinsic base is then implanted with BF2 at 40 Kev in order to achieve a very shallow collector-base junction. The resulting contours are shown in fig.7 where the 2D segregation effects can be clearly seen in the region near the first polysilicon layer.

Fig. 7: Boron countours after intrinsic base implant and extrinsic base annealing in the polysilicon emitter transistor.

Arsenic doped polysilicon is then deposited to form the emitter contact and the emitter doping by diffusion. The process models implemented are those used in SUPREM III for silicon and oxide. Moreover, the diffusion barrier effect of the native oxide lying between the doped polysilicon and the silicon substrate is modeled by a segregation condition for arsenic given by (Sagara, 1987):

(2)

$$m_{si-p} = \frac{C_{si}}{C_{poly}} = 0.5$$

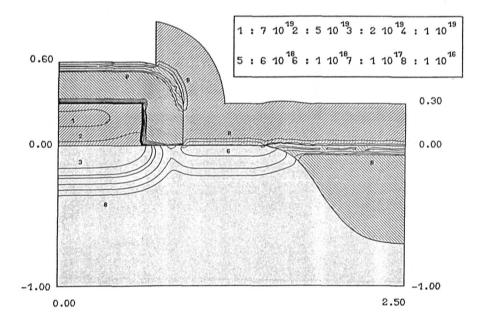

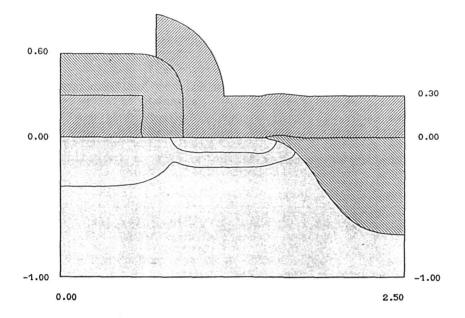

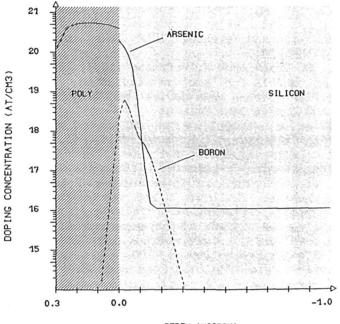

Finally, the emitter is diffused at 950°C for 40 min in neutral ambient. The resulting profiles are shown for boron (fig.8) and net concentrations (fig.9). From these figures, one can see that the overall boundary conditions are efficiently solved. A cross-section in the active area of the device is shown in fig.10. The total number of nodes is 7402 and the total number of nodes is 4015. The overall simulation requires about 2 hours of cpu time on a 1 Mips machine (IBM 4341).

# Fig. 8: Boron contours in the final structure.

264

Fig. 9: Junctions locations in the final structure.

DEPTH (MICRON)

Fig. 10: Cross section of the active device.

#### CONCLUSIONS

A new 2D multilayer process simulator has been presented that allows precise simulation of advanced silicon devices. The future work will be concerned with oxidation step in a general multilayer structure and a detailed study of the polysilicon material, since the flexibility of the program allows modeling of complex diffusion effects including grain segregation.

#### REFERENCES

- Borucki L et al. (1985). FEDSS- A 2D semiconductor fabrication process simulator. *IBM J. Res. Develop.*, 29, 3, 263-276.

- Collard D. and K. Taniguchi (1986). IMPACT a point defect based two dimensional process simulator : modeling the lateral oxidation enhanced diffusion of dopants in silicon. *IEEE Trans. Electron Devices*, *ED*-33, 1454-1462.

- Collard D. et al. (1987). IMPACT User's guide. ISEN.

- Hecht F. and A. Marrocco (1986). Internal technical report on MSHPTS, INRIA, Roquencourt, France.

- Oldham W.G. et al (1980). A general simulator for VLSI lithography and etching processes : Part II - application to deposition and etching. *IEEE Trans. Electron Devices*, *ED-27*, 1455-1459.

- Ryssel H., G. Prinke and K. Hoffmann (1983). Implantation and diffusion models for process simulation. In K.M. De Meyer (Ed.), VLSI process and device modeling, Vol. 1, summer course 1983, Heverlee, Belgium.

- Sagara K. et al. (1987). The effect of thin interfacial oxides on electrical characteristics of silicon bipolar devices. *IEEE Trans. Electron Devices*, ED-34, 11, 2286-2290.

- Tang D.D. et al (1982). 1.25 µm deep-groove-isolated selfaligned bipolar circuits. IEEE J. Solid-State Circuits, SC-17, 925-931.

- Yamamoto S. et al (1987). A two-dimensional etching profile simulator : ESPRIT. IEEE Trans. Computer-Aided-Design, CAD-6, 417-421.