## New Approaches in A Parallel 3-D One-Carrier Device Solver

Ke-Chih Wu, Robert F. Lucas, Ze-Yi Wang, Robert W. Dutton

Integrated Circuits Laboratory AEL 231F, Stanford University, Stanford, CA94305

## ABSTRACT

A 3-D one-carrier device solver has been developed on an Intel iPSC/MX<sup>TM</sup> hypercube multiprocessor which uses Slotboom variable in conjunction with the Gummel-Scharfetter scheme. A novel initial guess scheme is employed which allows stable calculation for large voltage steps. A modified singular perturbation scheme has been implemented to effectively speed up the convergence under high Vgs and Vds bias conditions.

## New Approaches in A Parallel 3-D One-Carrier Device Solver

Ke-Chih Wu, Robert F. Lucas, Ze-Yi Wang, Robert W. Dutton

Integrated Circuits Laboratory AEL 231F, Stanford University, Stanford, CA94305

A three dimensional one-carrier device solver has been developed on an Intel iPSC/MX<sup>TM</sup> hypercube multiprocessor which can handle 180 K variables (90K nodes). Typical solution time for a MOSFET example of 70 K nodes is 150 minutes per bias point on the current system but the execution time is expected to be reduced by a factor of 30 on a iPSC/2VX<sup>TM</sup> system.

Due to the constraints imposed by the huge number of nodes required for a realistic 3-D solution, iterative matrix solvers and Gummel iteration based non-linear solution methods are used. In this paper, some of the issues involved in developing such a 3-D solver are discussed.

Slotboom variable is used with the current continuity equation which requires the less expensive symmetric matrix solver in pure Gummel iterations. Through appropriate scaling, overflow problem can be avoided for bias of as high as 60 volts. To preserve the accuracy of current calculation, Scharfetter-Gummel formulation is used and which is shown to differ from the traditional formulation by a no-more-than-one correction coefficient.

A good initial guess is essential for a speedy and stable solution of the nonlinear semiconductor equations. For the Gummel iteration methods, the traditional initial guess scheme which is general in nature<sup>1</sup> suffers from severe concentration overshoot at large voltage steps because of its failure to anticipate the change in space charge region. A novel scheme is used in our program to prevent such a problem. In recognizing the fact that only overestimation of carrier concentration causes stability problems, the quasi-Fermi level is adjusted during the Poisson solution following the initial guess to prevent dramatic increase in carrier concentration. With this scheme, very large potential updates can be allowed without stability problem. In fact, an initial bias of Vgs = 5V and Vds = 5V has been successfully computed for a coarsely grided one-micron MOSFET.

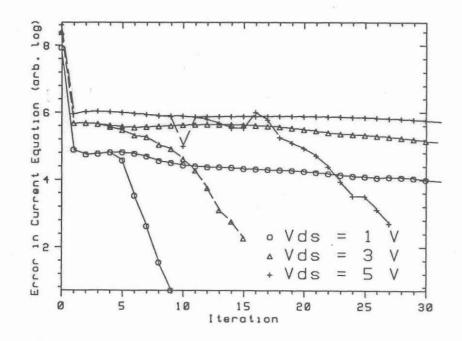

Despite the claim that scaling the Slotboom variable has extended significantly the satisfactory convergence region for Gummel iteration<sup>2</sup>, the convergence is still very slow at high Vgs and Vds region. To stay within the frame work of a Gummel iteration method, the singular perturbation (SP) scheme proposed by Ringhofer<sup>3</sup> has been implemented to accelerate the convergence. The original version is found to be rather unstable. However, a simple modification of using the full diagonal of the Poisson matrix (instead of excluding the contribution from the Laplace operator) has yielded a significant improvement in convergence properties. Table 1 shows the comparison of pure and SP modified Gummel iteration after SP modification has set in. The speed-up in CPU time ranges from a factor of 3.0 to 6.4. The asymptotic convergence rate, however, is found to be linear and deteriorate with increasing Vds. Fig. 1 shows the reduction of error in current equation versus iteration including the initial steps.

It is found that the modified SP scheme can be analyzed using the same block matrix formulation which has been used to analyze the alternate block factorization (ABF) scheme of Bank and Smith<sup>4</sup> and block iteration approach can be used. In the resulting matrix, the coupling block below the diagonal is reduced due to the fact that the main matrix of Poisson's equation is a diagonally dominant one.

## References

- 1. M. S. Mock, "Basic Theory of Stantionary Numerical Models," in *Process and Device Modeling*, ed. W. L. Engl, pp. 166 - 169, Elsevier Science Publishers B. V., North-Holand, 1986.

- 2. P. Blakey, G. Conrad, N. Kluksdahl, and R. Mezenner, "On the Use of Concus-Golub Transformed Slotboom Variables in Semiconductor Device Simulations," NUPAD I, 1986.

- 3. C. Ringhofer, "A Decoupled Iteration Method for the Basic Semiconductor Device Equations," NUPAD I, 1986.

- 4. R. E. Bank and R. K. Smith, "The Alternate Block Factorization Procedure for Systems of Partial Differential Equations," to appear.

| Vds | # of iterations |    | CPU speedup |       |

|-----|-----------------|----|-------------|-------|

|     | Gummel          | SP | Par. Solun. | Total |

| 1V  | 74              | 6  | 6.4         | 3.9   |

| 3V  | 136             | 13 | 4.1         | 3.4   |

| 5V  | 166             | 21 | 3.0         | 2.6   |

Table 1 Effect of SP modification in a MOSFET example (Vgs = 5V)

Figure 1 Current equation error versus iteration (Vgs = 5V)