## Optimization and benchmarking of graphenebased heterostructure FETs

D. Logoteta, G. Fiori, G. Iannaccone\*

Dipartimento di Ingegneria dell'Informazione, University of Pisa, Via G. Caruso 16, 56126 Pisa, Italy \*presenting author: e-mail: g.iannaccone@unipi.it

Native graphene has a zero energy gap and it is therefore not suitable as a transistor channel material for digital electronics [1]. However, recent advances based on materials engineering have demonstrated graphene-based "materials on demand", with tailored properties [2,3]. Vertical graphene heterostructures have been proven to be suitable for FETs [4,5] and hot-electron transistors [6] exhibiting large current modulation [7].

Inspired by recent progress in the growth of seamless *lateral graphene heterostructures* [8-10], graphene-based lateral heterostructure (LH)-FETs have been proposed [11-13], exhibiting extremely promising switching behavior in terms of leakage current, propagation delay, and power-delay product.

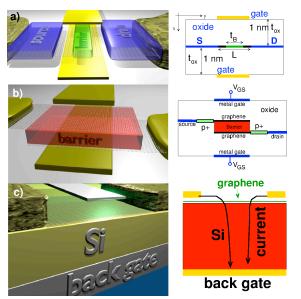

In this work, we explore the performance potential state-of-the-art graphene-based devices, which have already been demostrated to provide large Ion/Ioff ratios. We use a benchmark the predictions of the International Technology Roadmap for Semiconductors (ITRS) [12]. We focus on the lateral heterostructure FET (LH-FET), and two FETs based on vertical graphenebased heterostructures: one proposed by Britnell et al. [4], that we call VH-FET, and the "barristor" proposed in [14]. The three device structures are shown in Figs. 1a-c. Device simulation has been performed with the open source package NanoTCAD ViDES, implementing the selfconsistent solution of the Poisson and the Schroedinger equation within the Non-Equilibrium Green's Function formalism.

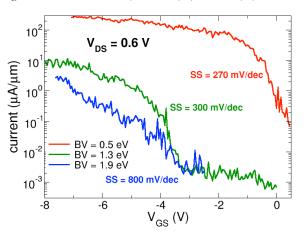

Vertical Heterostructure FET Performance - We consider the VH-FET shown in Fig. 1b, experimentally demonstrated in [4-5] and also analyzed in [7]. The barrier consists of three atomic layers of boron-carbon-nitride, AB-stacked on graphene. Fig. 2 shows the pFET transfer characteristics for different valence band edge barriers BV. Performance figures shown are poor:

the Ion/Ioff ratio is always smaller than 20 and the delay time is four orders of magnitude larger than that expected from ITRS.

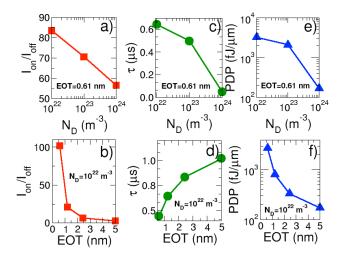

Barristor Performance - The device structure is shown in Fig. 1c. Silicon has a donor doping ND and the gate dielectric has effective oxide thickness EOT. The gate voltage modulates the Schottky barrier between graphene and silicon exploiting the partial graphene screening properties. Fig. 3 shows that performance is again much worse as compared to ITRS requirements CMOS transistors, i.e. poor Ion/Ioff, larger Power Delay Product (PDP) and large time switching  $(\tau)$ .

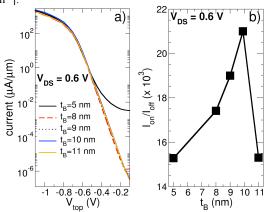

**LH-FET Optimization and performance** – Finally, we consider the double-gate p-channel LH-FET illustrated in Fig. 1a, BC2N is lattice-matched to graphene and has a bandgap of 1.6 eV, offering a barrier to holes from graphene of 0.64 eV. As can be seen in Fig. 4a, the transfer characteristics are almost independent of tB, and all performance parameters are optimized when tB = L (Figs. 4b). As can be seen, in this case, Ion/Ioff is very large ( $10^4$ ) and complying with ITRS requirements, and outperforming VH-FET and the barristor device.

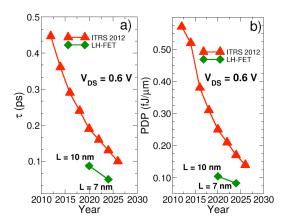

Conclusion - Finally, we compare in Fig. 5 the requirements of ITRS 2012 for high performance **CMOS** [12] with graphene-based heterostructure FETs. As can bee seen, LH-FETs exhibit lower intrinsic delay time and lower  $\tau$  than CMOS for the same gate length (considering 10 nm for 2020, and 7 nm for 2024). VH-FET and barristor cannot be included in the comparison since they exhibit larger delay times by at least four orders of magnitude. We are aware that our simulations do not consider the impact of dissipation in the channel, that typically reduces Ion by a factor two. Even taking this aspect into account, graphene-based lateral heterostructure FETs stand out as the most promising graphenebased transistors for digital electronics.

## REFERENCES

- [1] G. Iannaccone et al., IEDM Tech. Dig. 2009

- [2] F. Bonaccorso et al, Mat. Today Vol. 15, pp. 564, 2012.

- [3] K.S. Novoselov et al., Phys. Scr. T146, 014006, 2012.

- [4] L. Britnell et al., Science, Vol. 335 (2012), 947.

- [5] T. Georgiou, et al, Nat. Nanotech. Vol. 8, 100, 2013.

- [6] S. Vaziri et al. Nano Lett. Vol. 13, pp. 1435-1439, 2012.

- [7] G. Fiori et al., IEEE-TED Vol. 60, pp. 268-2703, 2013.

- [8] L. Ci, et al, Nat. Materials, 9 (2010), 430.

- [9] M. P. Levendorf et al. Nature 488, 627 (2012).

- [10] Z. Liu, et al. Nature Nanotechnology, 8, 119 (2013).

- [11] G. Iannaccone, G. Fiori, Patent WO 2013080237

- [12] G. Fiori et al., IEDM Tech. Dig. 2011

- [13] G. Fiori et al. ACS Nano 6, 2642-2648 (2012)

- [14] H. Yang, Science Vol. 336, pp. 1140-1143 (2012).

Fig.1.Device structure of a) LH-FET; b) VH-FET; c) Barristor

Fig. 2. Transfer characteristics of the VH-FET of Fig. 1b, for different values of the barrier BV at the valence band edge. The device has EOT = 0.62 nm (4nm HfO2), barrier thickness of three atomic layers

Fig. 3. a) [b)] Ion/Ioff, c) [d)]  $\tau$ , and e) [f)] DPI of the barristor as a function of  $N_D$  for EOT = 0.61 nm [of EOT for  $N_D = 10^{22}$  m<sup>-3</sup>].

Fig. 4. a) Transfer characteristics of the LH-FET for different values of  $t_B$ . b) Ion/Ioff ratio as a function of  $t_B$ . The device has the structure showninFig.1a,with L=10 nm,  $t_{ox} = 1 \text{nm}$ ,  $V_{dd} = 0.6 \text{V}$ , f = 0.01.

Fig. 5. a) Intrinsic delay time  $\tau$  and b) DPI as a function of year of shipment according to the ITRS 2012. On the same plot: comparison with simulation results for the LH-FETs with metal gate length of 10 nm (year 2020) and 7 nm (year 2024)